通过FPGA实现基于RS232串口的指令发送并控制显示器中目标位置

1.算法理论概述

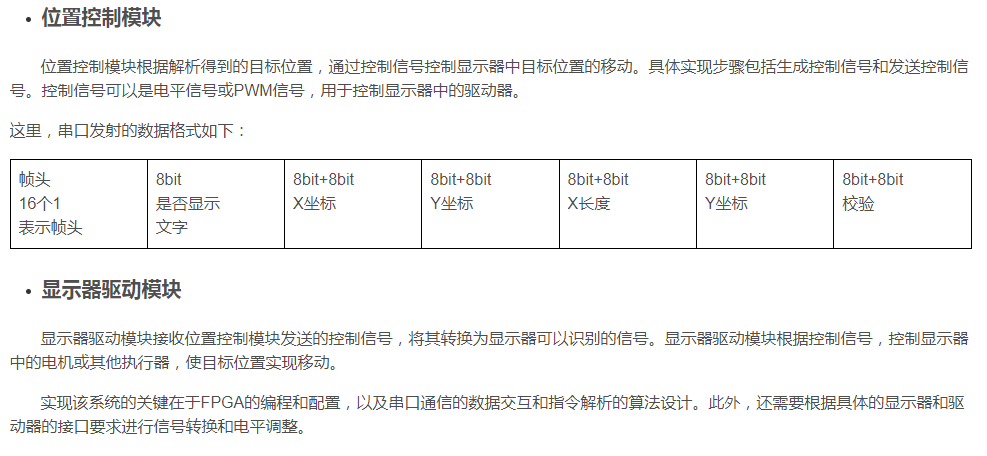

通过FPGA实现基于RS232串口的指令发送并控制显示器中目标位置是一种常见的应用场景,用于实现对显示器中目标位置的控制。该系统利用FPGA芯片作为主控制器,通过RS232串口与计算机或其他设备进行通信,接收指令并解析,然后控制显示器中目标位置的移动。该系统的主要原理是利用FPGA芯片作为主控制器,通过RS232串口与计算机或其他设备进行通信。计算机通过串口发送指令到FPGA,FPGA接收并解析指令,然后根据指令控制显示器中目标位置的移动。系统主要包括串口通信模块、指令解析模块、位置控制模块和显示器驱动模块。

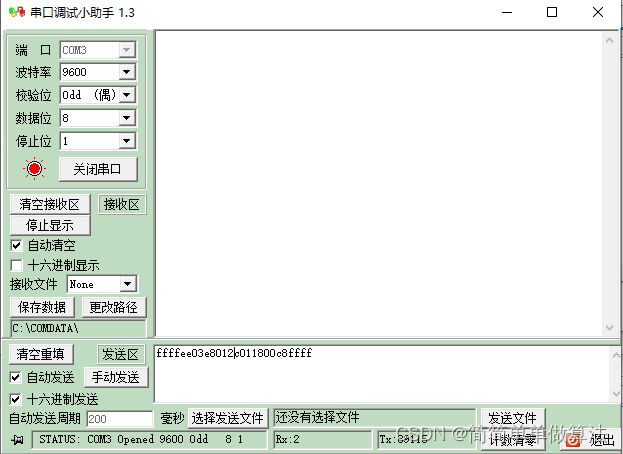

串口通信模块

串口通信模块用于与计算机或其他设备进行数据交互。通过RS232串口协议,实现数据的发送和接收。具体实现步骤包括串口初始化、数据发送和数据接收。

指令解析模块

指令解析模块用于解析接收到的指令,提取控制参数。指令可以是设定目标位置的命令,例如“MOVE X=100 Y=200”,其中X和Y为目标位置的横纵坐标。指令解析模块通过解析指令中的参数,提取目标位置的横纵坐标。

2.算法运行软件版本

MATLAB2022a

ISE14.7

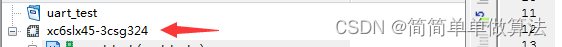

芯片型号:

使用的FPGA开发板型号如下:

黑金AX545开发板SPARTANT6 XC6S LX45

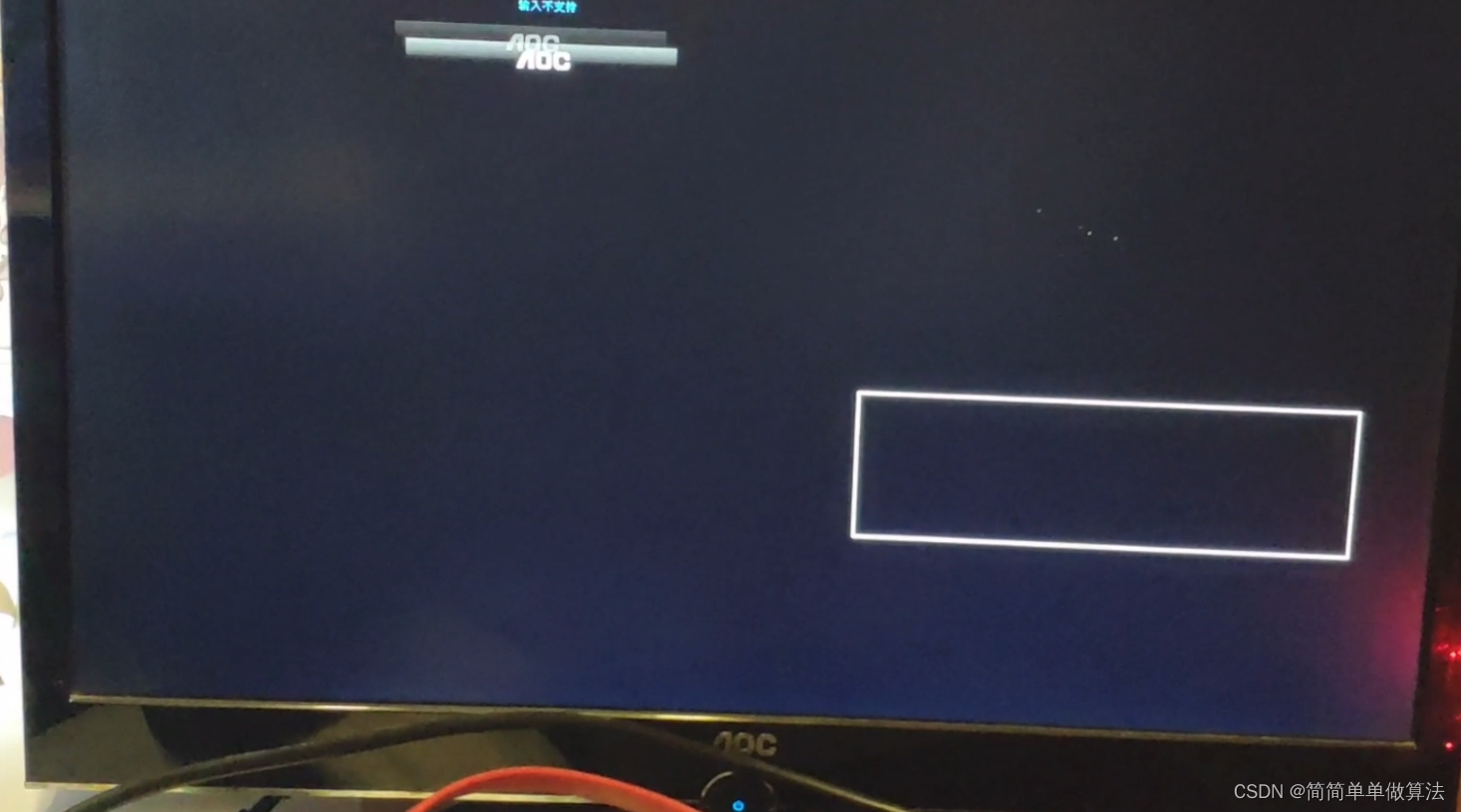

3.算法运行效果图预览

4.部分核心程序

wire RST;

assign RST = ~reset;

wire clk50M;

wire clk25M;

CLK_dcm CLK_dcm_u(// Clock in ports

.CLK_IN1 (clk50), // IN

// Clock out ports

.CLK_OUT1(clk50M), // OUT

.CLK_OUT2(clk25M)

); // OUT

//根据输入使能信号产生行列计数器,用来进行定位

//根据输入使能信号产生行列计数器,用来进行定位

//根据输入使能信号产生行列计数器,用来进行定位

wire [4:0] wvga_r;

wire [5:0] wvga_g;

wire [4:0] wvga_b;

wire [10:0]x_cnt;

wire [9:0] y_cnt;

wire vga_hsync;

wire vga_vsync;

//VGA显示控制部分

vga_disp vga_disp_inst(

.vga_clk (clk25M),

.vga_rst (RST),

.ddr_data_vga (64'd0), //如果使用DDR送入视频,那么从这里输入即可,我这边测试则不考虑,这里空出来

.vga_r (wvga_r), //DDr转换为R,

.vga_g (wvga_g), //DDr转换为G,

.vga_b (wvga_b), //DDr转换为B,

.vga_hsync (vga_hsync),

.vga_vsync (vga_vsync),

.ddr_addr_rd_set (), //ddr_addr_rd_set

.ddr_rden (), //ddr_rden

.ddr_rd_cmd (), //ddr_rd_cmd

.x_cnt (x_cnt),

.y_cnt (y_cnt)

);

//串口输入信号

//串口输入信号

//串口输入信号

//串口输入信号

wire[15:0]w_head;

wire[7 :0]w_text_view;

wire[15:0]w_x;

wire[15:0]w_y;

wire[15:0]w_w;

wire[15:0]w_h;

wire clk_data;

wire clk;

UART_signal instance_name (

.clk50 (clk50M),

.rx (rx),

.reset (RST),

.LED_test (),

.o_head (w_head),

.o_text_view(w_text_view),

.o_x (w_x),

.o_y (w_y),

.o_w (w_w),

.o_h (w_h),

.clk_data (clk_data),

.clk (clk)

);

reg[15:0]r_head;

reg[7 :0]r_text_view;

reg[15:0]r_x;

reg[15:0]r_y;

reg[15:0]r_w;

reg[15:0]r_h;

always @(posedge clk50M or posedge RST)

begin

if(RST)

begin

r_head <= 16'd0;

r_text_view <= 8'd0;

r_x <= 16'd0;

r_y <= 16'd0;

r_w <= 16'd0;

r_h <= 16'd0;

end

else begin

r_head <= w_head;

r_text_view <= w_text_view;

r_x <= w_x;

r_y <= w_y;

r_w <= w_w;

r_h <= w_h;

end

end

//字体显示

/

wire w_FLAG1;

test_load test_load_u(

.i_clk (clk25M),

.i_rst (RST),

.i_en (r_text_view[7]|r_text_view[6]|r_text_view[5]|r_text_view[4]|r_text_view[3]|r_text_view[2]|r_text_view[1]|r_text_view[0]),

.i_xcnt(x_cnt), //根据H和V的使能,得到视频区域的计数器

.i_ycnt(y_cnt), //根据H和V的使能,得到视频区域的计数器

.o_FLAG(w_FLAG1)

);

/

wire w_FLAG2;

box_load box_load_u(

.i_clk (clk25M),

.i_rst (RST),

.i_xcnt (x_cnt), //根据H和V的使能,得到视频区域的计数器

.i_ycnt (y_cnt), //根据H和V的使能,得到视频区域的计数器

.i_width (r_w), //16'd300

.i_height(r_h), //16'd200

.i_xc (r_x), //16'd1000

.i_yc (r_y), //16'd300

.o_flag (w_FLAG2)

);

wire[7:0]CCD_R;

wire[7:0]CCD_G;

wire[7:0]CCD_B;

wire[7:0]CCD_R1;

wire[7:0]CCD_G1;

wire[7:0]CCD_B1;

assign CCD_R1=(w_FLAG1==1'b1)?8'd255:{wvga_r,3'd0};

assign CCD_G1=(w_FLAG1==1'b1)?8'd255:{wvga_g,2'd0};

assign CCD_B1=(w_FLAG1==1'b1)?8'd255:{wvga_b,3'd0};

assign CCD_R=(w_FLAG2==1'b1)?8'd255:{CCD_R1};

assign CCD_G=(w_FLAG2==1'b1)?8'd255:{CCD_G1};

assign CCD_B=(w_FLAG2==1'b1)?8'd255:{CCD_B1};

assign vga_r=CCD_R[7:3];

assign vga_g=CCD_G[7:2];

assign vga_b=CCD_B[7:3];

//在线信号检测,实际最后可以删除

//在线信号检测,实际最后可以删除

//在线信号检测,实际最后可以删除

//在线信号检测,实际最后可以删除

wire[99:0]testdata;

assign testdata[15:0] = r_head;

assign testdata[23:16] = r_text_view;

assign testdata[39:24] = r_x;

assign testdata[55:40] = r_y;

assign testdata[71:56] = r_w;

assign testdata[87:72] = r_h;

assign testdata[88] = clk_data;

assign testdata[89] = clk;

Chipscop Chipscop_u(

.i_clk(clk),

.trig(8'b0000_0000),

.testdata(testdata)

);

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号