基于FPGA的火焰识别系统开发——简化版

基于FPGA的火焰识别系统开发的详细版欢迎订阅本博:

https://blog.csdn.net/ccsss22/article/details/115406504

1.问题描述

传统的森林火灾检测技术由于效率低、价格昂贵等缺点,并不适用于森林火灾探测。文中提出并设计与实现了一种基于小波变换的森林视频火灾烟雾检测方法,使用帧间差分法和质心算法提取疑似烟雾运动目标区域,然后对提取的运动目标的前景区域和背景区域进行小波能量特征提取与分析。

2.部分程序:

timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 08:29:24 02/23/2018

// Design Name:

// Module Name: smoke_reg1

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module smoke_reg1(

i_clk25MHz,

i_rst,

i_en,

i_R,

i_G,

i_B,

i_Fire_reg,

o_Smke_reg,

o_R_delay,

o_G_delay,

o_B_delay

);

parameter T0 =25;

input i_clk25MHz;

input i_rst;

input i_en;

input[7:0] i_R;

input[7:0] i_G;

input[7:0] i_B;

input i_Fire_reg;

output o_Smke_reg;

output[7:0]o_R_delay;

output[7:0]o_G_delay;

output[7:0]o_B_delay;

//[M,N] = size(R);

//SMKE = zeros(M,N);

//T0 = 25;

//

//

//%特征提取

//for i = 1:M

// for j = 1:N

// Cmax = max([R(i,j),G(i,j),B(i,j)]);

// Cmin = min([R(i,j),G(i,j),B(i,j)]);

// I = (R(i,j)+G(i,j)+B(i,j))/3;

// end

//end

reg[7:0]Cmax;

reg[7:0]Cmin;

reg[9:0]I;

reg o_Smke_reg;

reg[7:0]TR;

reg[7:0]TG;

reg[7:0]TB;

always @(posedge i_clk25MHz or posedge i_rst)

begin

if(i_rst)

begin

Cmax <= 8'd0;

Cmin <= 8'd0;

TR <= 8'd0;

TG <= 8'd0;

TB <= 8'd0;

I <= 10'd0;

o_Smke_reg <= 1'b0;

end

else begin

if(i_R >= i_G & i_R >= i_B)

Cmax <= i_R;

if(i_G >= i_R & i_G >= i_B)

Cmax <= i_G;

if(i_B >= i_R & i_B >= i_G)

Cmax <= i_B;

if(i_R <= i_G & i_R <= i_B)

Cmin <= i_R;

if(i_G <= i_R & i_G <= i_B)

Cmin <= i_G;

if(i_B <= i_R & i_B <= i_G)

Cmin <= i_B;

I <= {2'b00,i_R}+{2'b00,i_G}+{2'b00,i_B};

if(i_R >= i_G)

TR <= i_R - i_G;

else

TR <= i_G - i_R;

if(i_R >= i_B)

TB <= i_R - i_B;

else

TB <= i_B - i_R;

if(i_B >= i_G)

TG <= i_B - i_G;

else

TG <= i_G - i_B;

// if fire(i,j) == 0 %对非火焰区域进行烟雾检测

// if I>= 20 & I <= 150&...

// (abs(R(i,j)-G(i,j)) <= T0 & abs(R(i,j)-B(i,j)) <= T0 & abs(B(i,j)-G(i,j)) <= T0)

// SMKE(i,j) = 1;

// end

// end

if(i_Fire_reg == 1'b0)

begin

if((I >= 10'd60 & I <= 10'd450) & (TR <= T0) & (TG <= T0) & (TB <= T0))

// if((I >= 10'd60 & I <= 10'd450) & (TR <= T0 & TR >= 3) & (TG <= T0 & TG >= 3) & (TB <= T0 & TB >= 3))

o_Smke_reg <= 1'b1;

else

o_Smke_reg <= 1'b0;

end

else

begin

o_Smke_reg <= 1'b0;

end

end

end

//delay

reg[7:0]r_R_delay1;

reg[7:0]r_G_delay1;

reg[7:0]r_B_delay1;

reg[7:0]r_R_delay2;

reg[7:0]r_G_delay2;

reg[7:0]r_B_delay2;

always @(posedge i_clk25MHz or posedge i_rst)

begin

if(i_rst)

begin

r_R_delay1 <= 8'd0;

r_G_delay1 <= 8'd0;

r_B_delay1 <= 8'd0;

r_R_delay2 <= 8'd0;

r_G_delay2 <= 8'd0;

r_B_delay2 <= 8'd0;

end

else begin

r_R_delay1 <= i_R;

r_G_delay1 <= i_G;

r_B_delay1 <= i_B;

r_R_delay2 <= r_R_delay1;

r_G_delay2 <= r_G_delay1;

r_B_delay2 <= r_B_delay1;

end

end

assign o_R_delay = r_R_delay2;

assign o_G_delay = r_G_delay2;

assign o_B_delay = r_B_delay2;

endmodule

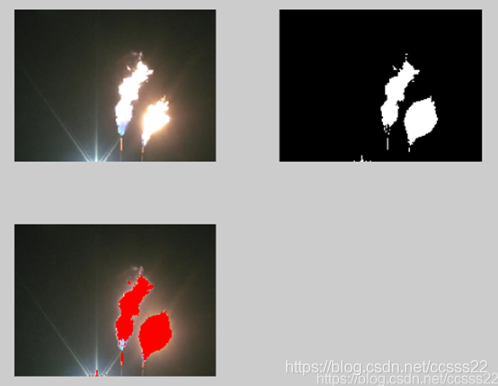

3.仿真结论:

A-023-040

浙公网安备 33010602011771号

浙公网安备 33010602011771号