基于FPGA的双目相机目标深度图像提取实现

目录

一、理论基础

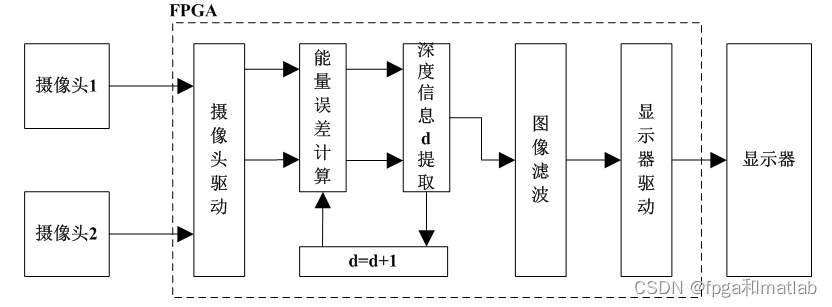

系统的整体框架结构如下图所示:

双目立体视觉模拟了人类双眼感知环境的方式其结构如图2-1所示,主要包括图像采集、摄像机表达、图像校正、立体匹配、及深度获取等五部分构成。

为了使得双目立体视觉能够走出实验室进入到实际应用中,研究者们在优化双目立体视觉系统实时性方面做了许多努力。在这些工作中有一些是基于资源受限的平台如FPGA、DSP或者ASIC等,它们都具有良好的并行计算的能力,并且使用T兼容性很好的局部匹配算法,但是它们的设计都十分复杂,并且具有较长的开发周期。而一些最近的研究确信FPGA是目前较为适合硬件开发的平台P41。在早期的研究中,大部分基于FPGA的平台为了满足实时性W及嵌入式应用的需求,大都使用原理较为简单的基于SAD的算法。而对于PC平台来说,即使是最简单的SAD算法也是不可能满足实时性的需求。然而,对于硬件平台来说,算的速度W及资源的占用是设计的核也内容,而准确性却被忽视了。在这之后,随着立体视觉技术W及FPGA制造工艺技术的发展,越来越多的基于FPGA的平台涌现出来。这些平台使用了更新更有效的算法,但是大部分都没有进行准确性方面的实验和测试。

二、核心程序

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 18:11:17 06/08/2018

// Design Name:

// Module Name: deep_image1

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module deep_image19(

FCLK_CLK0,

gpio_rtl_tri_o_0,

Edis0,

disparity0,

FIFO_M_AXIS_0_tdata,

FIFO_M_AXIS_1_tdata,

Edis1,

disparity1

);

input FCLK_CLK0;

input gpio_rtl_tri_o_0;

input[15:0]Edis0;

input[15:0]disparity0;

input[23:0]FIFO_M_AXIS_0_tdata;

input[23:0]FIFO_M_AXIS_1_tdata;

output[15:0]Edis1;

output [15:0]disparity1;

reg [7:0]R1;

reg [7:0]G1;

reg [7:0]B1;

reg [7:0]Rdelay1;

reg [7:0]Gdelay1;

reg [7:0]Bdelay1;

reg [7:0]Rdelay1a;

reg [7:0]Gdelay1a;

reg [7:0]Bdelay1a;

reg [7:0]Rdelay1b;

reg [7:0]Gdelay1b;

reg [7:0]Bdelay1b;

reg [7:0]Rdelay1c;

reg [7:0]Gdelay1c;

reg [7:0]Bdelay1c;

reg [7:0]Rdelay1d;

reg [7:0]Gdelay1d;

reg [7:0]Bdelay1d;

reg [7:0]Rdelay1e;

reg [7:0]Gdelay1e;

reg [7:0]Bdelay1e;

reg [7:0]Rdelay1f;

reg [7:0]Gdelay1f;

reg [7:0]Bdelay1f;

reg [7:0]Rdelay1g;

reg [7:0]Gdelay1g;

reg [7:0]Bdelay1g;

reg [7:0]Rdelay1h;

reg [7:0]Gdelay1h;

reg [7:0]Bdelay1h;

reg [7:0]Rdelay1i;

reg [7:0]Gdelay1i;

reg [7:0]Bdelay1i;

reg [7:0]Rdelay1j;

reg [7:0]Gdelay1j;

reg [7:0]Bdelay1j;

reg [7:0]Rdelay1k;

reg [7:0]Gdelay1k;

reg [7:0]Bdelay1k;

reg [7:0]Rdelay1l;

reg [7:0]Gdelay1l;

reg [7:0]Bdelay1l;

reg [7:0]Rdelay1m;

reg [7:0]Gdelay1m;

reg [7:0]Bdelay1m;

reg [7:0]Rdelay1n;

reg [7:0]Gdelay1n;

reg [7:0]Bdelay1n;

reg [7:0]Rdelay1o;

reg [7:0]Gdelay1o;

reg [7:0]Bdelay1o;

reg [7:0]Rdelay1p;

reg [7:0]Gdelay1p;

reg [7:0]Bdelay1p;

reg [7:0]Rdelay1q;

reg [7:0]Gdelay1q;

reg [7:0]Bdelay1q;

reg [7:0]Rdelay1r;

reg [7:0]Gdelay1r;

reg [7:0]Bdelay1r;

reg [7:0]Rdelay11;

reg [7:0]Gdelay11;

reg [7:0]Bdelay11;

always @(posedge FCLK_CLK0 or negedge gpio_rtl_tri_o_0)

begin

if(!gpio_rtl_tri_o_0)

begin

R1 <= 8'd0;

G1 <= 8'd0;

B1 <= 8'd0;

Rdelay1<= 8'd0;

Gdelay1<= 8'd0;

Bdelay1<= 8'd0;

Rdelay1a<= 8'd0;

Gdelay1a<= 8'd0;

Bdelay1a<= 8'd0;

Rdelay1b<= 8'd0;

Gdelay1b<= 8'd0;

Bdelay1b<= 8'd0;

Rdelay1c<= 8'd0;

Gdelay1c<= 8'd0;

Bdelay1c<= 8'd0;

Rdelay1d<= 8'd0;

Gdelay1d<= 8'd0;

Bdelay1d<= 8'd0;

Rdelay1e<= 8'd0;

Gdelay1e<= 8'd0;

Bdelay1e<= 8'd0;

Rdelay1f<= 8'd0;

Gdelay1f<= 8'd0;

Bdelay1f<= 8'd0;

Rdelay1g<= 8'd0;

Gdelay1g<= 8'd0;

Bdelay1g<= 8'd0;

Rdelay1h<= 8'd0;

Gdelay1h<= 8'd0;

Bdelay1h<= 8'd0;

Rdelay1i<= 8'd0;

Gdelay1i<= 8'd0;

Bdelay1i<= 8'd0;

Rdelay1j<= 8'd0;

Gdelay1j<= 8'd0;

Bdelay1j<= 8'd0;

Rdelay1k<= 8'd0;

Gdelay1k<= 8'd0;

Bdelay1k<= 8'd0;

Rdelay1l<= 8'd0;

Gdelay1l<= 8'd0;

Bdelay1l<= 8'd0;

Rdelay1m<= 8'd0;

Gdelay1m<= 8'd0;

Bdelay1m<= 8'd0;

Rdelay1n<= 8'd0;

Gdelay1n<= 8'd0;

Bdelay1n<= 8'd0;

Rdelay1o<= 8'd0;

Gdelay1o<= 8'd0;

Bdelay1o<= 8'd0;

Rdelay1p<= 8'd0;

Gdelay1p<= 8'd0;

Bdelay1p<= 8'd0;

Rdelay1q<= 8'd0;

Gdelay1q<= 8'd0;

Bdelay1q<= 8'd0;

Rdelay1r<= 8'd0;

Gdelay1r<= 8'd0;

Bdelay1r<= 8'd0;

Rdelay11<= 8'd0;

Gdelay11<= 8'd0;

Bdelay11<= 8'd0;

end

else begin

R1 <= FIFO_M_AXIS_0_tdata[23:16];

G1 <= FIFO_M_AXIS_0_tdata[15:8];

B1 <= FIFO_M_AXIS_0_tdata[7:0];

Rdelay1 <= FIFO_M_AXIS_1_tdata[23:16];

Gdelay1 <= FIFO_M_AXIS_1_tdata[15:8];

Bdelay1 <= FIFO_M_AXIS_1_tdata[7:0];

Rdelay1a<= Rdelay1;

Gdelay1a<= Gdelay1;

Bdelay1a<= Bdelay1;

Rdelay1b<= Rdelay1a;

Gdelay1b<= Gdelay1a;

Bdelay1b<= Bdelay1a;

Rdelay1c<= Rdelay1b;

Gdelay1c<= Gdelay1b;

Bdelay1c<= Bdelay1b;

Rdelay1d<= Rdelay1c;

Gdelay1d<= Gdelay1c;

Bdelay1d<= Bdelay1c;

Rdelay1e<= Rdelay1d;

Gdelay1e<= Gdelay1d;

Bdelay1e<= Bdelay1d;

Rdelay1f<= Rdelay1e;

Gdelay1f<= Gdelay1e;

Bdelay1f<= Bdelay1e;

Rdelay1g<= Rdelay1f;

Gdelay1g<= Gdelay1f;

Bdelay1g<= Bdelay1f;

Rdelay1h<= Rdelay1g;

Gdelay1h<= Gdelay1g;

Bdelay1h<= Bdelay1g;

Rdelay1i<= Rdelay1h;

Gdelay1i<= Gdelay1h;

Bdelay1i<= Bdelay1h;

Rdelay1j<= Rdelay1i;

Gdelay1j<= Gdelay1i;

Bdelay1j<= Bdelay1i;

Rdelay1k<= Rdelay1j;

Gdelay1k<= Gdelay1j;

Bdelay1k<= Bdelay1j;

Rdelay1l<= Rdelay1k;

Gdelay1l<= Gdelay1k;

Bdelay1l<= Bdelay1k;

Rdelay1m<= Rdelay1l;

Gdelay1m<= Gdelay1l;

Bdelay1m<= Bdelay1l;

Rdelay1n<= Rdelay1m;

Gdelay1n<= Gdelay1m;

Bdelay1n<= Bdelay1m;

Rdelay1o<= Rdelay1n;

Gdelay1o<= Gdelay1n;

Bdelay1o<= Bdelay1n;

Rdelay1p<= Rdelay1o;

Gdelay1p<= Gdelay1o;

Bdelay1p<= Bdelay1o;

Rdelay1q<= Rdelay1p;

Gdelay1q<= Gdelay1p;

Bdelay1q<= Bdelay1p;

Rdelay1r<= Rdelay1q;

Gdelay1r<= Gdelay1q;

Bdelay1r<= Bdelay1q;

Rdelay11<= Rdelay1r;

Gdelay11<= Gdelay1r;

Bdelay11<= Bdelay1r;

end

end

reg [7:0]Rd1;

reg [7:0]Gd1;

reg [7:0]Bd1;

reg [15:0]Rdata1;

reg [15:0]Gdata1;

reg [15:0]Bdata1;

reg [15:0]Sdata1;

reg [15:0]ErrorEnergy1;

always @(posedge FCLK_CLK0 or negedge gpio_rtl_tri_o_0)

begin

if(!gpio_rtl_tri_o_0)

begin

Rd1 <= 8'd0;

Gd1 <= 8'd0;

Bd1 <= 8'd0;

Rdata1 <= 16'd0;

Gdata1 <= 16'd0;

Bdata1 <= 16'd0;

Sdata1 <= 16'd0;

ErrorEnergy1 <= 16'd0;

end

else begin

if(R1>Rdelay11)

Rd1 <= R1-Rdelay11;

else

Rd1 <= Rdelay11-R1;

if(G1>Gdelay11)

Gd1 <= G1-Gdelay11;

else

Gd1 <= Gdelay11-G1;

if(B1>Bdelay11)

Bd1 <= B1-Bdelay11;

else

Bd1 <= Bdelay11-B1;

Rdata1 <= Rd1*Rd1;

Gdata1 <= Gd1*Gd1;

Bdata1 <= Bd1*Bd1;

Sdata1 <= Rdata1+Gdata1+Bdata1;

ErrorEnergy1 <= Sdata1;

end

end

reg [15:0]Edis1;

reg [15:0]disparity1;

always @(posedge FCLK_CLK0 or negedge gpio_rtl_tri_o_0)

begin

if(!gpio_rtl_tri_o_0)

begin

Edis1 <= 16'd0;

disparity1 <= 16'd0;

end

else begin

if(Edis0 >= ErrorEnergy1)

begin

disparity1 <= 16'd19;

Edis1 <= ErrorEnergy1;

end

else begin

disparity1 <= disparity0;

Edis1 <= Edis0;

end

end

end

endmodule

三、测试结果

点击run之后,程序就下载到FPGA开发板中了。

A23-44

浙公网安备 33010602011771号

浙公网安备 33010602011771号