latch和dff的区别

触发器:flipflop,锁存器:latch 对于这个认识,我写了几行Verilog代码 代码如下

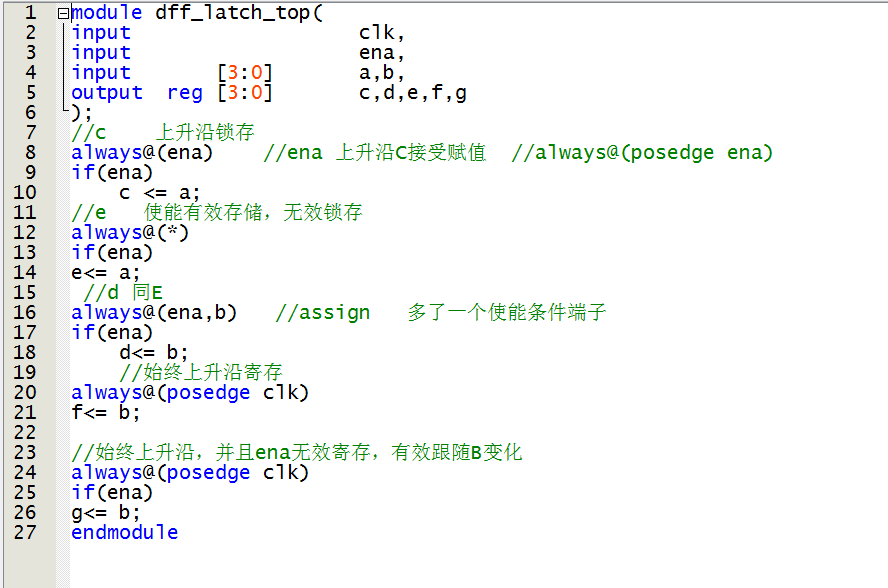

`module dff_latch_top(

input clk,

input ena,

input [3:0] a,

input [3:0] b,

output reg [3:0] c,

output reg [3:0] d,

output reg [3:0] e,

output reg [3:0] f,

output reg [3:0] g

);

//c 上升沿锁存

always@(ena) //ena 上升沿C接受赋值 //always@(posedge ena)

if(ena)

c <= a;

//e 使能有效存储,无效锁存

always@(*)

if(ena)

e<= a;

//d 同E

always@(ena,b) //assign 多了一个使能条件端子

if(ena)

d<= b;

//始终上升沿寄存

always@(posedge clk)

f<= b;

//始终上升沿,并且ena无效寄存,有效跟随B变化

always@(posedge clk)

if(ena)

g<= b;

endmodule `

代码写出来了我们用quartus 综合看下netlistRTL网表

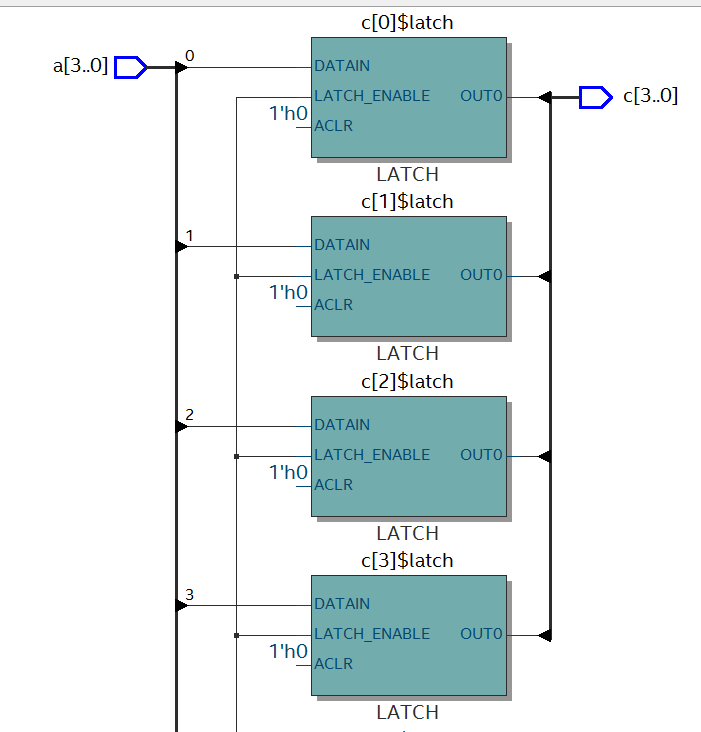

c d e 代码对于的网表

从中可以看出C D E代码对于的是latch

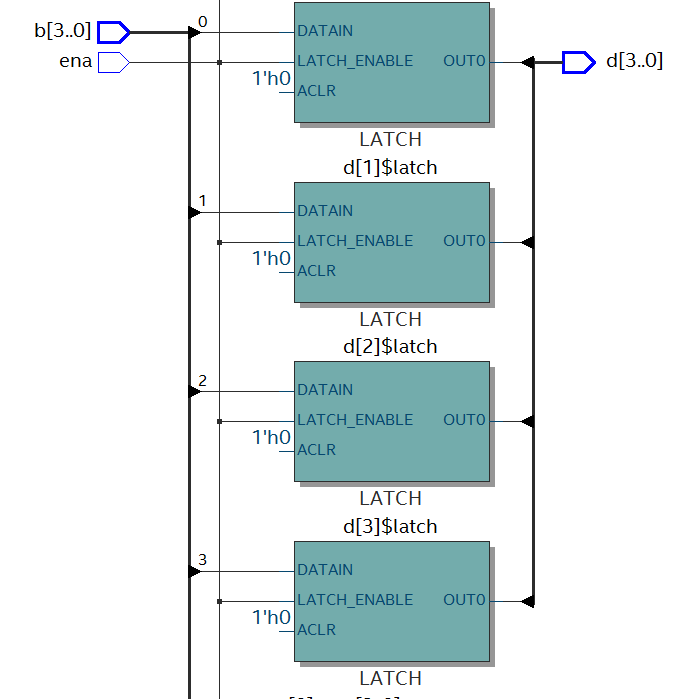

我们再看下GF对于的网表RTL图

这里看得出他们两个都属于DFF触发器

接下来我们用modelsim 仿真看下他们几个的区别

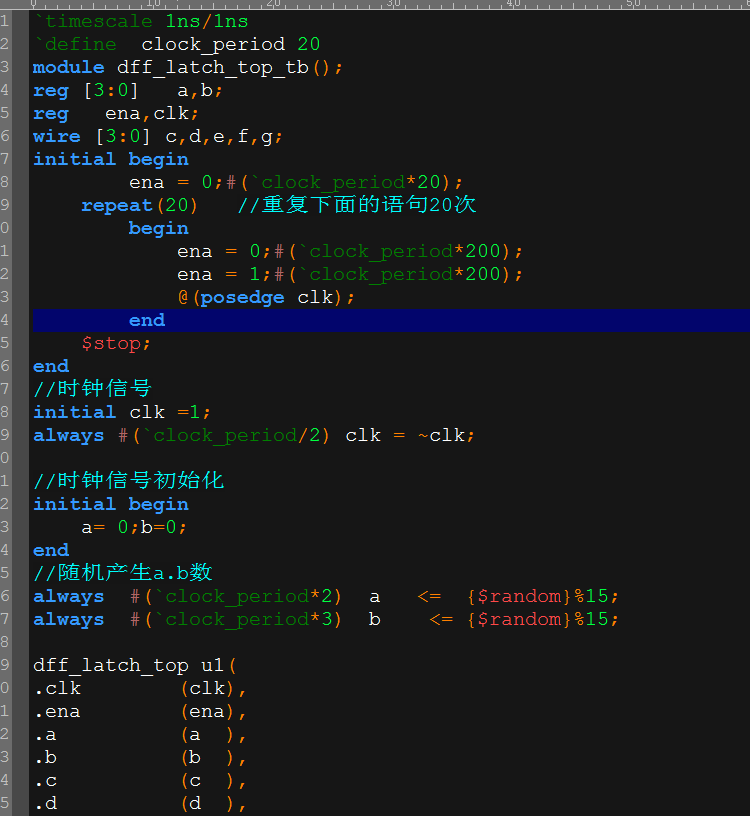

代码图片,和代码如下

``timescale 1ns/1ns

define clock_period 20 module dff_latch_top_tb(); reg [3:0] a,b; reg ena,clk; wire [3:0] c,d,e,f,g; initial begin ena = 0;#(clock_period20);

repeat(20) //重复下面的语句20次

begin

ena = 0;#(clock_period*200); ena = 1;#(clock_period200);

@(posedge clk);

end

$stop;

end

//时钟信号

initial clk =1;

always #(`clock_period/2) clk = ~clk;

//时钟信号初始化

initial begin

a= 0;b=0;

end

//随机产生a.b数

always #(clock_period*2) a <= {$random}%15; always #(clock_period*3) b <= {$random}%15;

dff_latch_top u1(

.clk (clk),

.ena (ena),

.a (a ),

.b (b ),

.c (c ),

.d (d ),

.e (e ),

.f (f ),

.g (g )

);

endmodule`

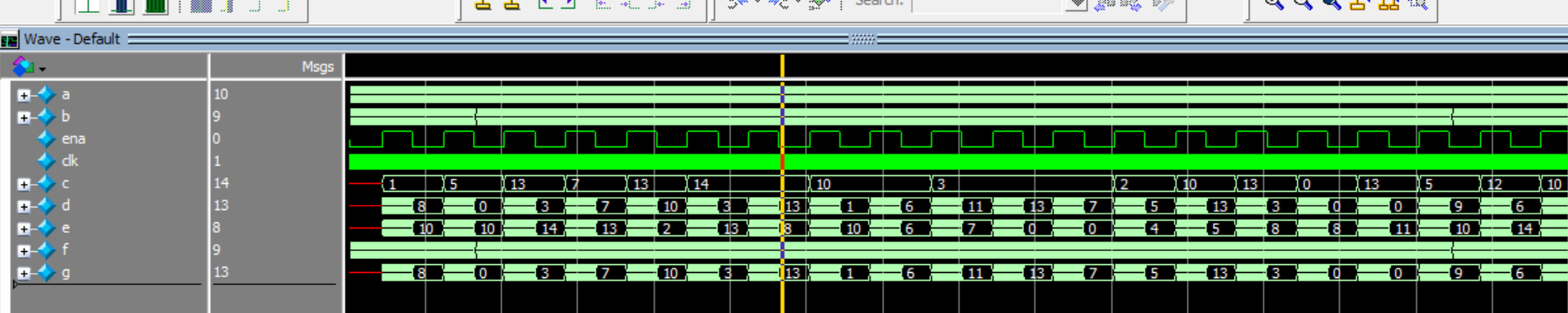

启动modelsim 我们看到如图波形

拉开细节分析

先看c波形

总体上C是在ena的上升沿赋值操作,C 的数据属于存储状态,只有在ena上升沿来到的时候,C得到一次赋值

d的话 也是出于ena地电平锁存,ena 出于高点平,d的属于随b变化而变化

E类似于d 的状态 使能有效d 状态随a变化而变化

f随b的变化而变化,他是在时钟信号的节拍下进行

g 的话在ena有效的情况下,同f变化,当ena无效g出于锁存状态

从这个试验中,希望大家理解DFF和latch 细微的区别

浙公网安备 33010602011771号

浙公网安备 33010602011771号