在FPGA中简单的建立一个工程,并编写测试文件

本人觉得写博文是一件很累人的事!尤其是写一些总结性的博文!不过好的博文可以帮助很多人!比如张亚峰,萧鸿森的博客!都是很经典很受用的!

我也打算写写,当然不可能写得跟他们一样好!我只是希望借助这种方式,把平时见到的一些问题跟解决方法记录下来,等以后什么时候要用到,

就可以翻开看看。前阵子也是因为找工作的事,FPGA学习的事耽搁了。结果重新学习的时候,发现很多东西都忘了。

所以以后事无大小都要件件记录,事事总结,不然一个不小心忘了,什么都要重头再来。那就费力了,养成一个好的学习习惯总是无害的吧

先附上两位高手的博客地址

张亚峰:http://www.cnblogs.com/yuphone/

萧鸿森:http://www.cnblogs.com/oomusou/archive/2008/07/31/verilog_clock_divider.html

接下来开始总结我建立一个简单的工程文件了。表达能力有限,图说:

FPGA建立工程可以有两种方式,一种是先输入所有的硬件描述文件,然后建立工程,在工程中添加这些硬件描述文件。另一种是先建立工程,然后在建立硬件描述文件然后添加到工程中去。这里只介绍新建工程,在建立描述文件。

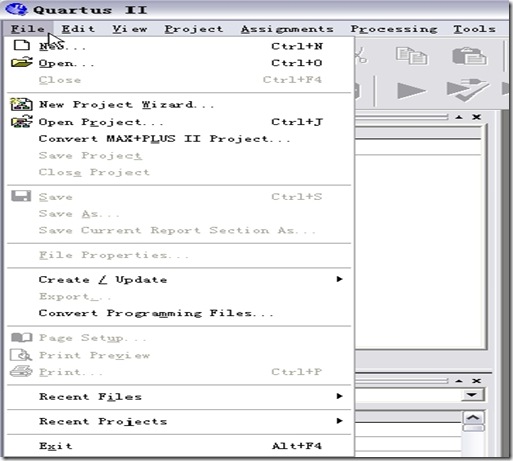

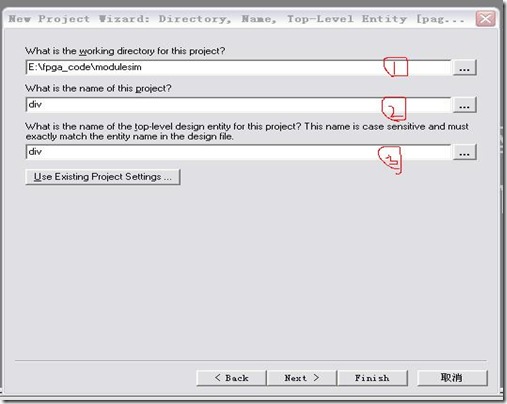

点击New Project Wizard (工程新建向导)然后弹出窗口:

- 红色圈圈1中是选择工程建立的路径,一般工程文件的路径最好不要出现中文,容易造成无法编译。

- 红色圈圈2中是工程的名称,一般工程的名称最好选择有意义的,方便以后查找代码。当然工程的名称不可以是中文或者特殊字符开头。

- 红色圈圈3中是工程的顶层文件实体名,所谓顶层文件里面的实体名就是module 后面紧跟着的那个名称(举例是以verilog语言为主)

切记一点:红色圈圈2一定要跟红色圈圈3 的一样,不过如果你在这里填写的话,一般填写一个,另外一个就跟着填写一样的名称。当然如果顶层文件是外面添加的就得注意这一点了。

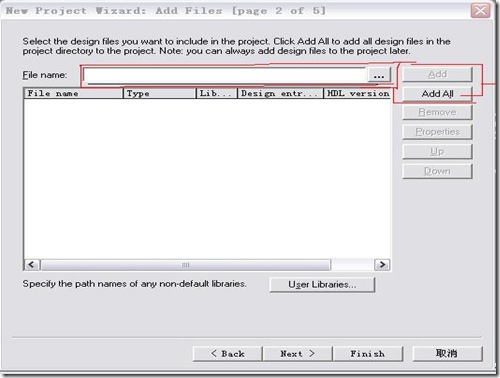

填写完毕后直接点击下一步:

在这里如果你是先建硬件描述文件的话,就可以在这里添加你所有的文件到工程中,如果你是先建工程的话,那就直接跳过这一窗口,点击下一步:

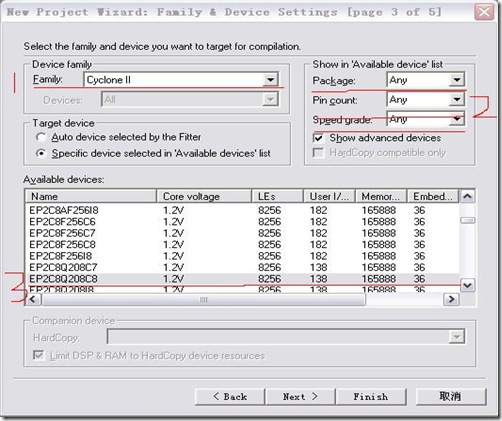

在这里主要是选择芯片类型,如果你的代码只是做一些简单的波形测试,没有涉及板级调试或者过多锁相环应用的话,这里可以随便选择,完全不影响代码的编译。因为在这里选择芯片类型,一来是为了下载时芯片匹配,二来是芯片内部资源的报告生成。

- 红色1 是选择芯片的系列

- 红色2是通过选择封装类型,管脚数目,速度等级来进一步更快锁定你想要的芯片

- 红色3当你找到芯片时,单击该芯片,该芯片变成灰色代表选定芯片

设置完毕后点击下一步:

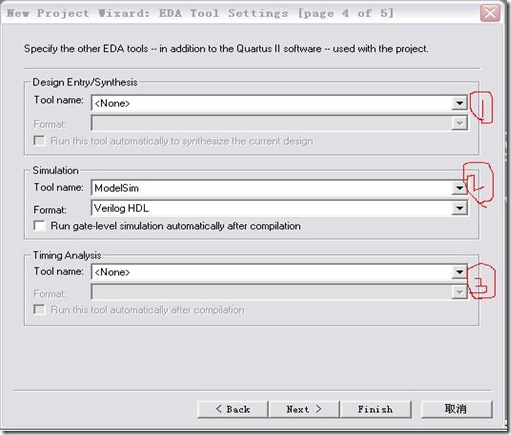

这里是设置Q2的编译软件。主要是用于仿真时候用,如果编写的代码很简单,又或者习惯用Q2自带的波形仿真软件,那这里可以不用设置直接点击下一步,

- 红色圈圈1 好像是行为仿真什么的来的,具体我也不清楚

- 红色圈圈2是时序仿真,由于我用的是第三方软件Modelsim ,所以选择Modelsim

- 红色圈圈3是时序分析,具体怎么用我也不清楚

总之很多东西一开始都默认就是了,等以后深入了或者用到的时候再去研究也不迟,(当然如果韧劲比较足的也可以尝试去看看altera公司的使用说明,那里都说得很清楚)

下一步:

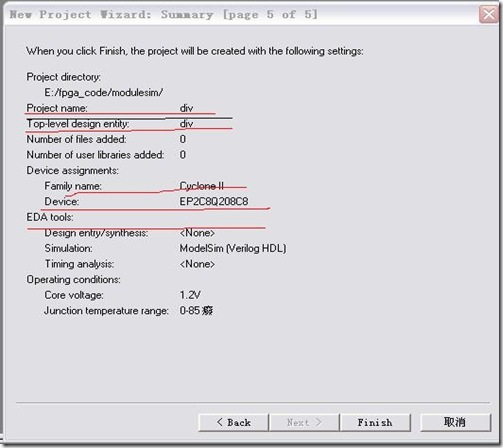

到这里整个工程就建立完成了,这个窗口会把刚刚工程设置的所有信息显示出来,比如工程名称,顶层文件实体名称,芯片型号等等,接下来就是建立硬件描述文件了:

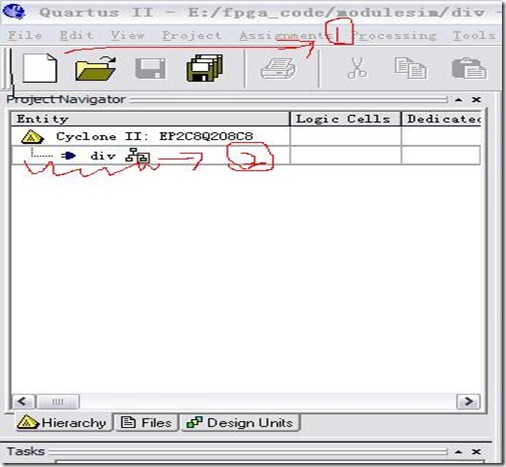

进入主界面,点击红色圈圈1,选择硬件描述文件的类型,这里可以注意以下红色圈圈2中的图标是紫色实体,说明工程中还没有顶层文件。接着弹出以下窗口:

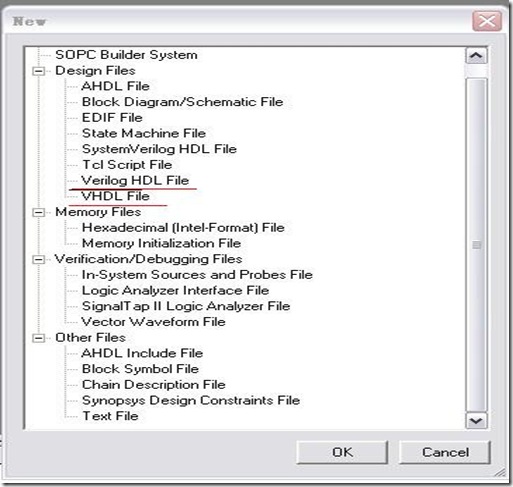

这这里选择文件的类型,我用的是verilog,所以选择verilog HDL file,其他文件各有用途,我知道的只有VHDL也是用来描述硬件组成的,还有就是一个波形仿真文件,也就是当你没有第三方仿真软件的时候,就要建立Vector WAveform file .还有BOLCK symbol file以连接电路的方式建立文件关联等。

下面附上一段简单的代码:

march_seven

这是一个简单的二分频电路,具体怎样实现就不多说了。代码输入完毕后,点击保存,保存名称最好为顶层文件的实体名,保存路径为工程文件夹下。

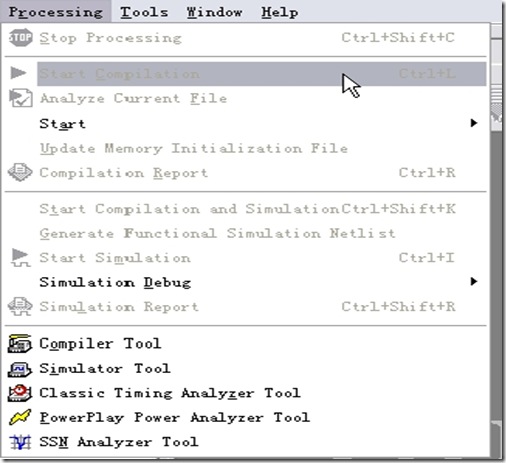

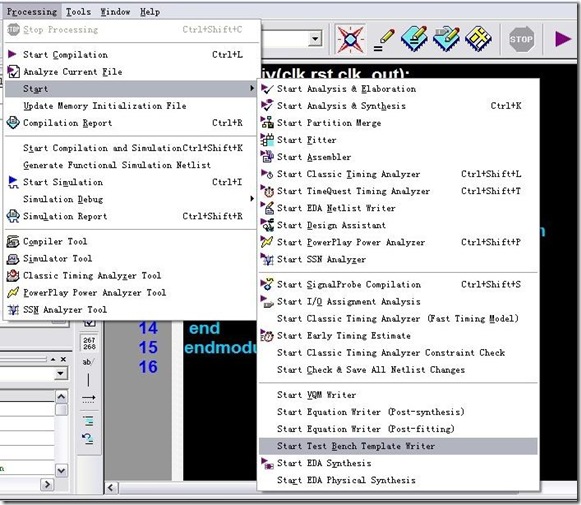

保存完毕后,如果你的Q2有编译的快捷图标(大三角图标)直接点击编译,如果没有则按上图所示点击编译。编译成功后就可以进行仿真了,至于仿真软件的安装就不在这里说明了。

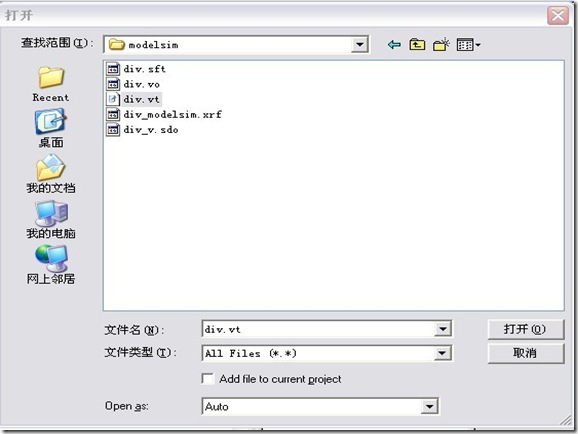

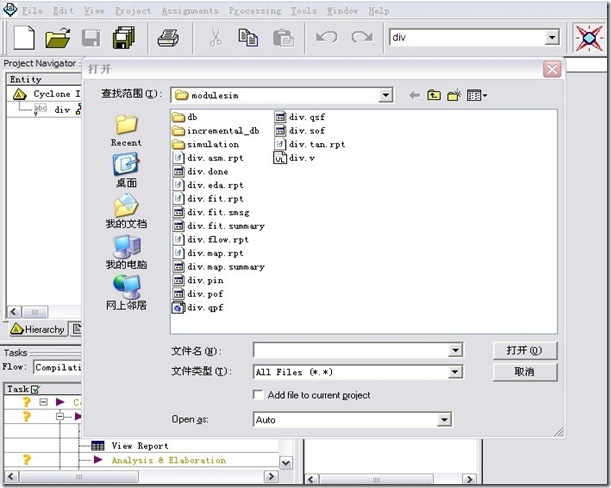

如图所示建立测试脚本,即testbench。建立成功后打开testbench,原始的testbench里面已经有默认的模板,你只需输入测试文本就是了。testbench存储在仿真文件夹里面格式为.vt的文件

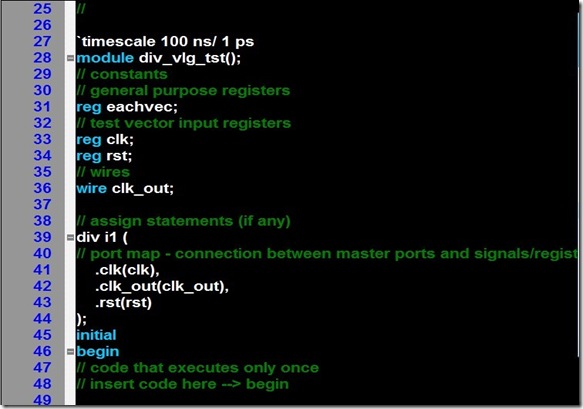

打开文件可见testbench已经默认了一些块,等待输入测试语句

下面附上一段相关的测试脚本

march_seven

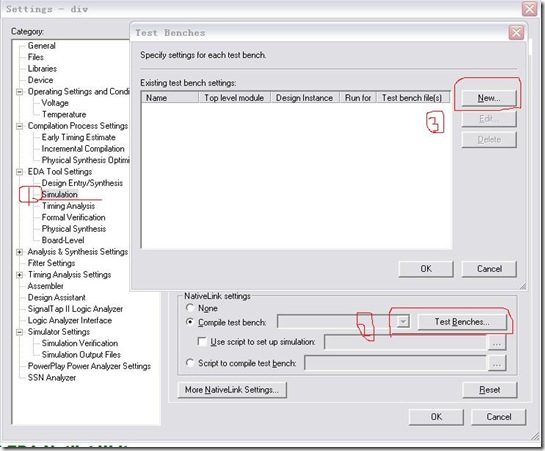

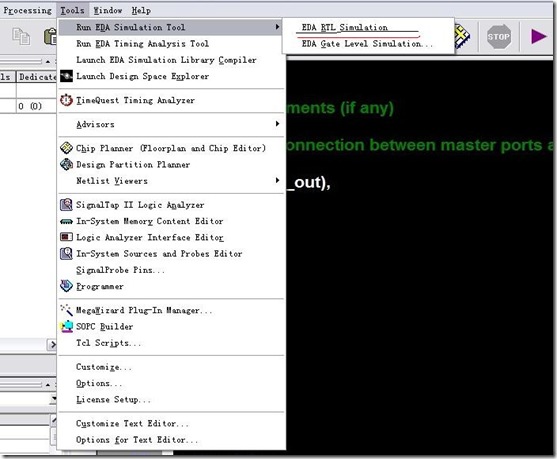

保存该文件。然后设置路径跟信息:

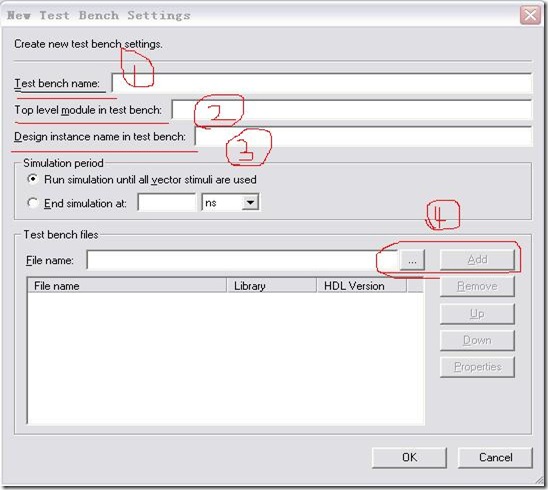

按照红色圈圈的顺序设置,当点击红色圈圈3的时候弹出以下窗口:

- 红色圈圈1 填写testbench的存储的文件的名称,就是.vt的文件名

- 红色圈圈2 填写testbench中实体名,div_vlg_tst;

- 红色圈圈3填写testbench中实体例化名,div i1

- 红色圈圈4添加testbench文件。

至此一切都全部设置完毕,然后点击OK结束设置。然后运行仿真,便可得出结果

个人觉得初学者,很多地方都默认就是了。不用处处都追根问底,这样一来增加学习的难度一来又影响学习的热情。但也不是说什么都不管,起码要留个印象。最重要还是要学会总结,总结没有分好坏,只要可以起到唤醒记忆的功能,那即便是一个字母那也是一个好的总结。。。。