AXI总线简介

AXI全称Advanced eXtensible Interface,是Xilinx从6系列的FPGA开始引入的一个接口协议,主要描述了主设备和从设备之间的数据传输方式。在ZYNQ中继续使用,版本是AXI4,所以我们经常会看到AXI4.0,ZYNQ内部设备都有AXI接口。其实AXI就是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)的一个部分,是一种高性能、高带宽、低延迟的片内总线,也用来替代以前的AHB和APB总线。第一个版本的AXI(AXI3)包含在2003年发布的AMBA3.0中,AXI的第二个版本AXI(AXI4)包含在2010年发布的AMBA 4.0之中。

AXI协议具有如下特点:

. 总线的地址/控制和数据通道是分离的;

. 支持不对齐的数据传输;

. 在突发数据传输中只需要首地址;

. 同时具有分离读/写数据通道;

. 支持显著传输访问和乱序访问;

. 更加容易进行时序收敛

AXI4包含三种接口:

. AXI4——For high-performance memory-mapped requirements.

. AXI4-Lite——For simple, low-throughput memory-mapped communication (for example, to and from control and status registers).

. AXI4-Stream——For high-speed streaming data.

从上面的描述可以看出,AXI4协议相当于原来的AHB协议,提供高速的系统内部互连通道,可以支持burst模式,主要用于处理器访问存储等需要高速数据的场合;AXI4-Lite为外设童工单个数据传输,相当于原来的APB协议,用于访问一些低速外设;AXI4-Stream接口就像FIFO一样,数据传输的时候不需要地址,而是主从设备直接连续读写数据,主要用于如视频、高速AD、PCIe、DMA接口等需要高速数据传输的场合,跟Xilinx原来的Local Link协议类似。

AXI Interconnect

AXI协议严格的讲是一个点对点的主从接口协议,当多个外设需要互相交互数据时,我们需要加入一个AXI Interconnect模块,也就是AXI互联矩阵,作用是提供将一个或多个AXI主设备连接到一个或多个AXI从设备的一种交换机制(有点类似于交换机里面的交换矩阵)。Xilinx为我们提供了实现这种互联矩阵的IP核axi_interconnect_1,在前面的例子中,我们在XPS中可以看到。这个IP核最多可以支持16个主设备、16个从设备,如果需要更多的接口,可以多加入几个IP核。关于AXI Interconnect更多的知识,可参考Xilinx官方文档DS768。

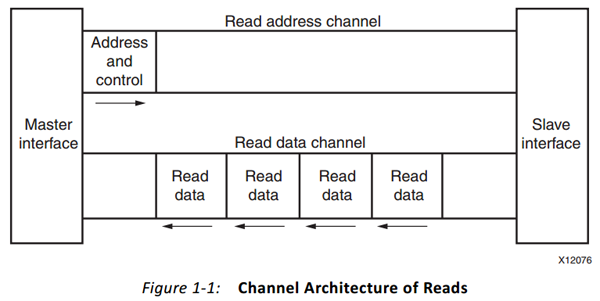

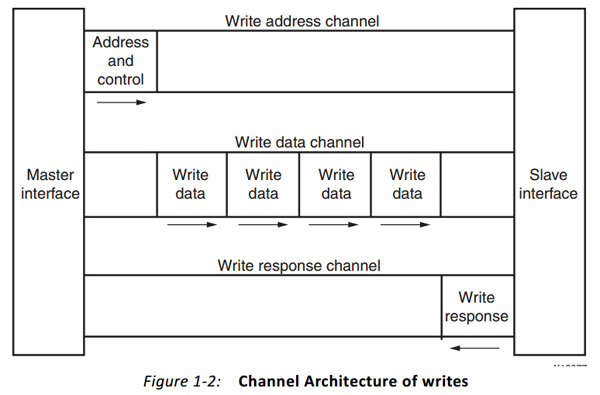

AXI4和AXI4-Lite接口包含5个不同的通道:

. Read Address Channel

. Write Address Channel

. Read Data Channel

. Write Data Channel

. Write Response Channel

其中每个通道都是一个独立的AXI握手协议。下面两个图分别显示了读和写的模型:

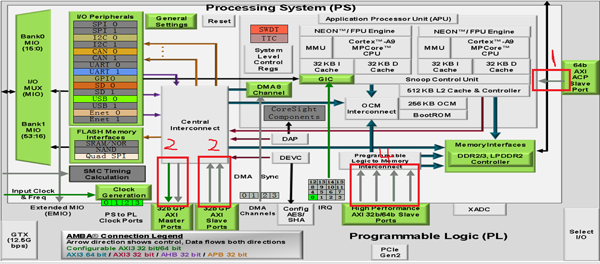

ZYNQ中的AXI接口共有9个,主要用于PS与PL的互联,包含以下三个类型:

. AXI_ACP接口,是ARM多核架构下定义的一种接口,中文翻译为加速器一致性端口,用来管理DMA之类的不带缓存的AXI外设,PS端是Slave接口。

. AXI_HP接口,是高性能/带宽的AXI3.0标准的接口,总共有四个,PL模块作为主设备连接。主要用于PL访问PS上的存储器(DDR和On-Chip RAM)

. AXI_GP接口,是通用的AXI接口,总共有四个,包括两个32位主设备接口和两个32位从设备接口。

其实,在具体设计中我们往往不需要在连接这个地方做太多工作,就像上一个例子中,我们加入IP核以后,系统会自动使用AXI接口将我们的IP核与处理器连接起来,我们只需要再做一点补充就可以了。不过,这部分概念还是了解比较好。