数字电路(一) 如何读懂时序图

1. 时序图组成元素

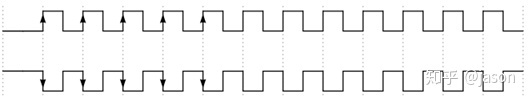

1.1 方波

这样的图形常用来表示CLOCK (时钟信号),通常见与时序图的顶部

方波还常见这种格式,在时钟上加上向上/向下的箭头,这是用于表示 是在上升沿触发还是在下降沿触发.

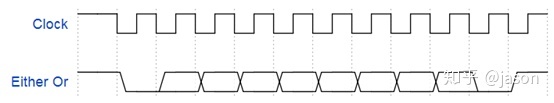

1.2 Either or 信号暂且称之为非此即彼信号吧.

非此即彼信号在时序图中纵横交错,常常让初学者搞不清楚,但是其意思是很简单的,对应上面的时钟即 表示时钟采样时 有可能为高,也有可能为低.常用在DATA 线上.比如I2C 读取设备信号时,数据信号可能为高也可能为低.而交叉处的含义是,此刻允许数据变化.对应上面CLOCK 信号可以看出.只有当clock为低时,信号线上的数据才允许变化.当clock 为高时,数据线上要么是高,要么是低. 如果你使用过I2C ,你会知道,I2C的读数据时就是这个样子的.

1.3 灰色区域

灰色区域表示此处为三态,即 高电平,第电平,高阻态,或者简单说,这段区域是啥都行,并不需要关心,这个上面的非此即彼信号不同的是,非此即彼要么是高,要么是低,不可以出现高阻态.

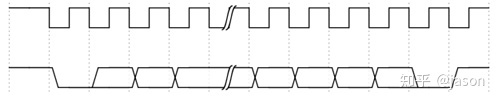

1.4 省略符号

以上 类似f 的图形表示省略符号,例如我读取falsh RAM数据,一次允许你读出 256个字节,但时序图上肯定放不下这么长的内容,就用省略符号来表示.

以上 类似f 的图形表示省略符号,例如我读取falsh RAM数据,一次允许你读出 256个字节,但时序图上肯定放不下这么长的内容,就用省略符号来表示.

1.5 地址&数据表示

时序图上常用A 来表示Address, D来表示Data.这个应该很好理解.

时序图上常用A 来表示Address, D来表示Data.这个应该很好理解.

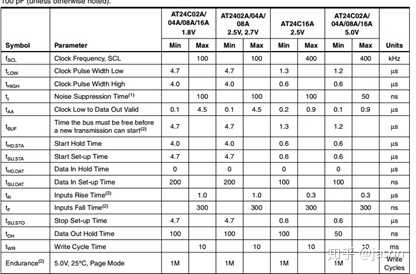

1.6 时序需要控制时间说明

在通讯协议中,常常标注,上升沿,下降沿,高电平,一个信号需要在另一个信号后延时多少才可以改变状态.以上应该是涵盖了比较常见的时序图中的图形.

2.实例

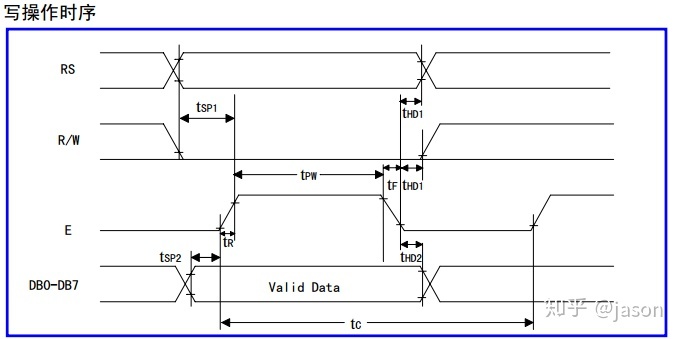

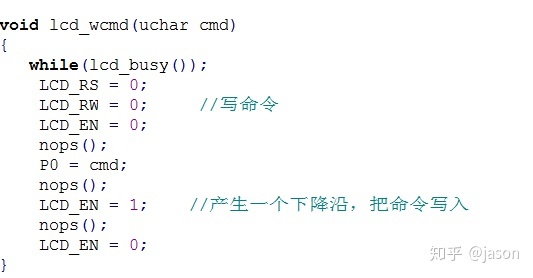

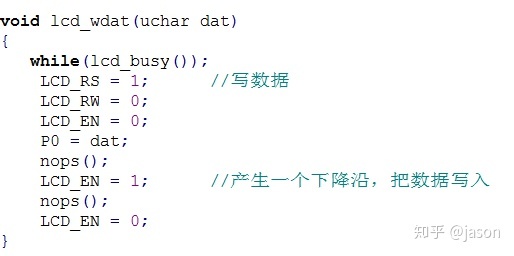

2.1LCD1602时序图

规格书中直接就给出了操作时序的说明,大家可以按照这个来理解时序图

下面几个假设性问答有可能帮助到你:

- A. 写或读时,为什么 RS 是既可以高又可以低,不应该一种状态吗?

取决于读或写的是数据还是指令,如果是指令,则为低,如果是数据则为高 - B. 时序图中如何表现出 数据被读出/写入呢?

时序图中DB0—DB7 出现交叉的地方,表示允许数据变化,即写入/读出. - C. 时序图中,箭头上的tsp,tpw 表示什么意思?

例如tsp1 表示RS R/W 变化后,需要等待tsp1 时间,才允许E变化,tsp1 数值在规格书中一定会有表格说明的,但此处因为==这些数值只有ns,写程序时通常不会加延时==.

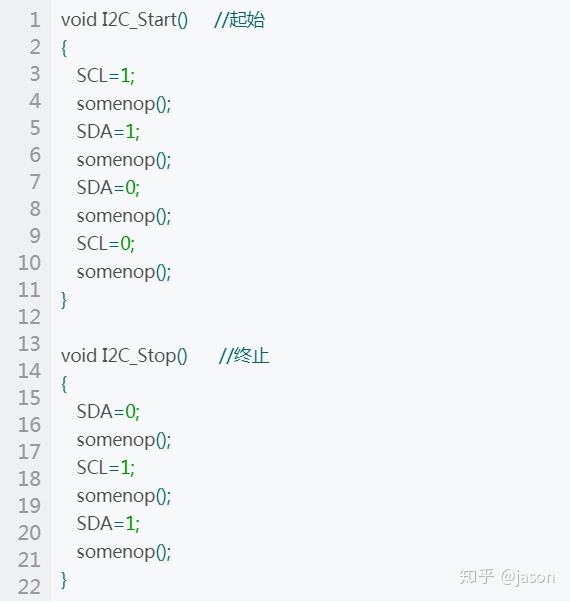

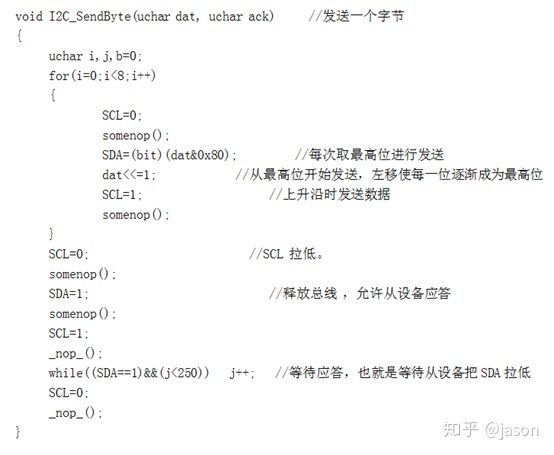

2.2 IIC时序图

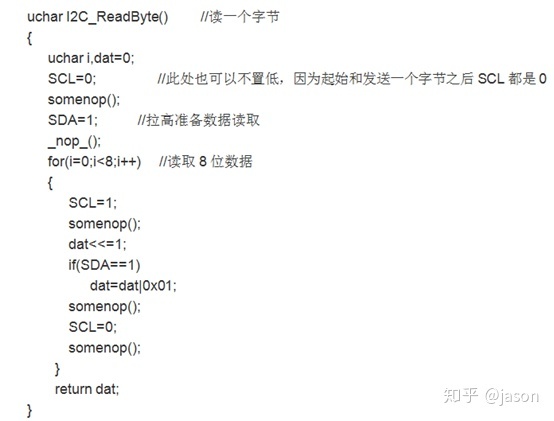

- 起始位和停止位

![]()

从图上可以看出,Start 的条件是: 在SCL 高电平期间,SDA 从高到低变换,Stop 的条件是: 在SCL 高电平期间,SDA 从低到高变换

-

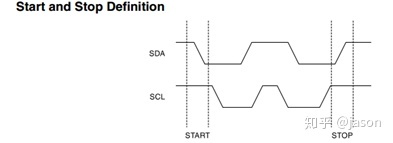

发送数据时序图

![]()

发送数据数据传输时最主要记住的是: 数据在低电平期间允许改变,而在高电平期间必须保持稳定. -

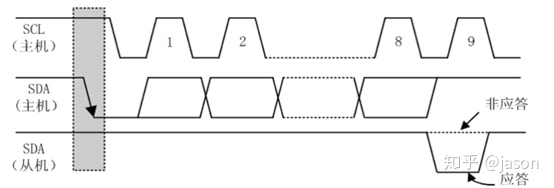

数据有效位定义.

![]()

![]()

-

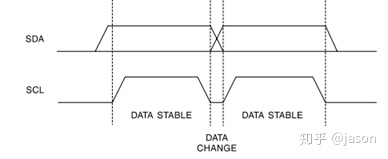

读数据

读数据和写是很类似的,从设备在CLK低时改变SDA 值,这样主设备在高电平时将这个值读回来.

3. 注意

- 一个时序图中可能包含多个命令,在读的时候最好独立出来,不要被干扰。

- 读同步时序电路时,以时钟信号为单位将书序图进行划分.

本文来自博客园,作者:曼路的个人博客,转载请注明原文链接:https://www.cnblogs.com/manlujun/p/16059964.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号