关于vhdl中integer消耗资源的一些讨论

源程序:注意红色字体为之后对比的中将做改动的语句

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity control is

port(clk:in std_logic;

dip1:in std_logic;

--bcd:out std_logic_vector(3 downto 0);

--bcd:out integer range 1 to 9 ;

bcd:out integer ;

en:out std_logic);

end entity control;

architecture behav of control is

type state_type is (s0,s1);

signal state:state_type;

signal cnt:std_logic_vector(3 downto 0):="0001";

--signal cnt:integer range 1 to 9 :=1;

--signal cnt:integer :=1;

begin

process(clk)

begin

if rising_edge(clk) then

if dip1='1' then

case state is

when s0 => if cnt>1 then cnt<=cnt-1;

else cnt<=cnt+1;state<=s1;

end if;

when s1 => if cnt<9 then cnt<=cnt+1;

else cnt<=cnt-1;state<=s0;

end if;

end case;

end if;

end if;

end process;

en <= '1';

--bcd <= cnt;

--bcd <= conv_std_logic_vector(cnt,4);

bcd <= conv_integer(cnt);

end behav;

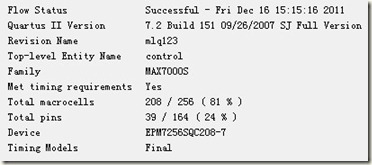

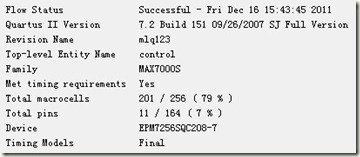

第一种: 端口处及内部信号都是用integer

--bcd:out std_logic_vector(3 downto 0);

--bcd:out integer range 1 to 9 ;

bcd:out integer ;

--signal cnt:std_logic_vector(3 downto 0):="0001";

--signal cnt:integer range 1 to 9 :=1;

signal cnt:integer :=1;

bcd <= cnt;

--bcd <= conv_std_logic_vector(cnt,4);

--bcd <= conv_integer(cnt);

编译时间最长,大概30~40秒吧,可能更长

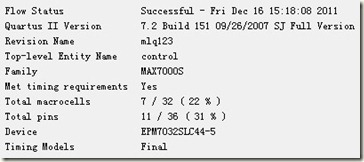

第二种: 端口处及内部信号都是用integer range 1 to 9

--bcd:out std_logic_vector(3 downto 0);

bcd:out integer range 1 to 9 ;

--bcd:out integer ;

--signal cnt:std_logic_vector(3 downto 0):="0001";

signal cnt:integer range 1 to 9 :=1;

--signal cnt:integer :=1;

bcd <= cnt;

--bcd <= conv_std_logic_vector(cnt,4);

--bcd <= conv_integer(cnt);

编译了13秒

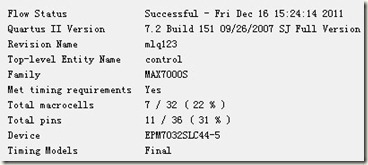

第三种: 端口处及内部信号都是用std_logic_vector(3 downto 0)

bcd:out std_logic_vector(3 downto 0);

--bcd:out integer range 1 to 9 ;

--bcd:out integer ;

signal cnt:std_logic_vector(3 downto 0):="0001";

--signal cnt:integer range 1 to 9 :=1;

--signal cnt:integer :=1;

bcd <= cnt;

--bcd <= conv_std_logic_vector(cnt,4);

--bcd <= conv_integer(cnt);

编译了11秒

结论:对比前三种情况可知使用range range 1 to 9后,编译器可以对硬件资源使用进行优化,效果相当于使用std_logic_vector(3 downto 0),其消耗的资源相同

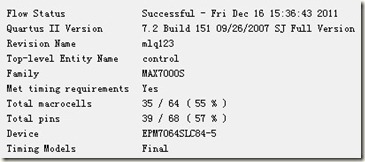

第四种: 端口处使用integer 内部信号使用std_logic_vector(3 downto 0)

--bcd:out std_logic_vector(3 downto 0);

--bcd:out integer range 1 to 9 ;

bcd:out integer ;

signal cnt:std_logic_vector(3 downto 0):="0001";

--signal cnt:integer range 1 to 9 :=1;

--signal cnt:integer :=1;

--bcd <= cnt;

--bcd <= conv_std_logic_vector(cnt,4);

bcd <= conv_integer(cnt);

第五种: 端口处使用std_logic_vector(3 downto 0) 内部信号使用integer

bcd:out std_logic_vector(3 downto 0);

--bcd:out integer range 1 to 9 ;

--bcd:out integer ;

--signal cnt:std_logic_vector(3 downto 0):="0001";

--signal cnt:integer range 1 to 9 :=1;

signal cnt:integer :=1;

--bcd <= cnt;

bcd <= conv_std_logic_vector(cnt,4);

--bcd <= conv_integer(cnt);