什么是门控时钟?如何产生门控时钟?

什么是门控时钟?

Clockgating:在数据无效时,将寄存器时钟关闭的技术,能够有效降低功耗, 是低功耗设计的重要方法之一。门控时钟其实就是一个逻辑模块,在寄存器的输入数据无效时,将寄存器的输入时钟置为0,而此时寄存器值保持不变,此时没有时钟翻转,避免了动态功耗。

如何生存门控时钟?

在IC设计中,编写RTL代码的时候,只要采用合理规范的编码风格,即可以通过EDA工具自行产生门控时钟模块。

举例如下:

推荐风格:可生成门控时钟

always@(posedge clk or negedge rst_n) if(!rst_n) data_out<=8’b0; else if(data_vld) data_out<=data_in;

不推荐:无法生成门控时钟

always@(posedge clk or negedge rst_n) if(!rst_n) data_out<=8’b0; else if(data_vld) data_out<=data_in; else data_out<=8’b0;

推荐的风格代码在else分支忽略,此时意味着在data_vld无效时data_out保持不变,此时状态与clock保持为0一致,因此具备生成门控时钟的条件,而不推荐风格代码,在data_vld无效时data_out为0,不符合门控时钟的状态,因此无法生成门控时钟。

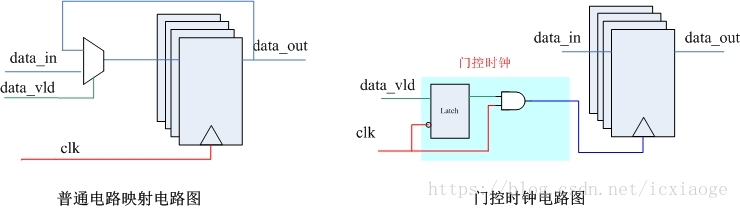

上图两个电路图均为推荐风格代码的映射电路图,右侧为采用门控时钟设计的电路图。采用推荐风格代码的代码即可以通过EDA工具自行插入门控时钟。

由于门控时钟逻辑具有一定的开销,因此数据宽度过小不适合做clockgating。一般情况下,数据宽度大于8比特时建议采用门控时钟。

实际芯片使用的门控时钟模块是后端厂家专门设计的模块单元,而不仅仅是图上的简单设计。

---------------------

作者:IC小鸽

来源:CSDN

原文:https://blog.csdn.net/icxiaoge/article/details/80792819

版权声明:本文为博主原创文章,转载请附上博文链接!

浙公网安备 33010602011771号

浙公网安备 33010602011771号