【FPGA学习笔记】VL40 占空比50%的奇数分频

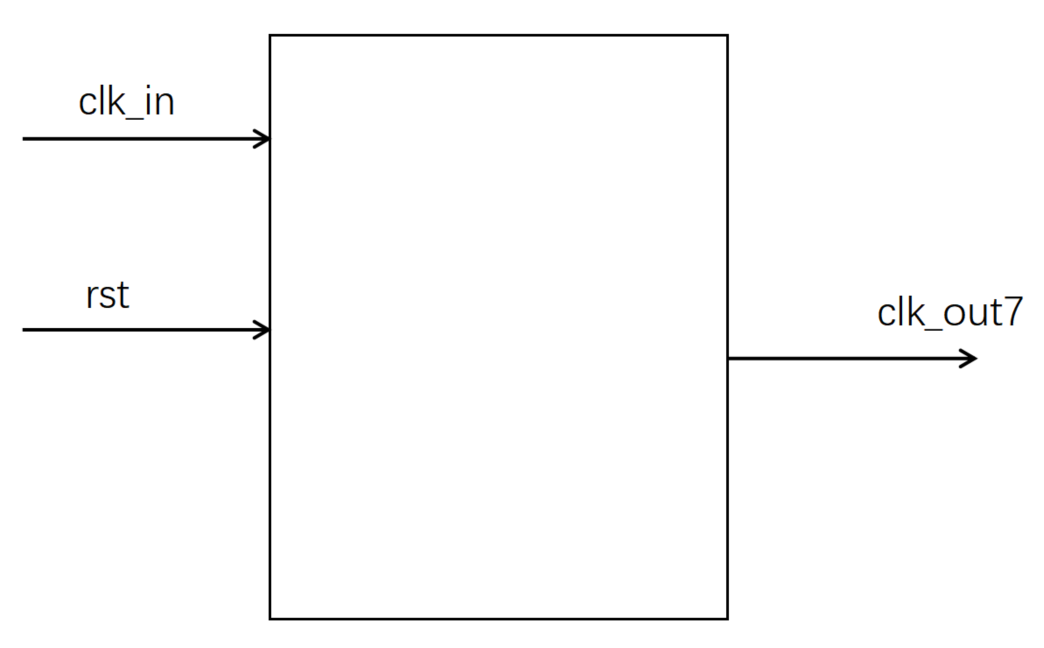

设计一个同时输出7分频的时钟分频器,占空比要求为50%

注意rst为低电平复位

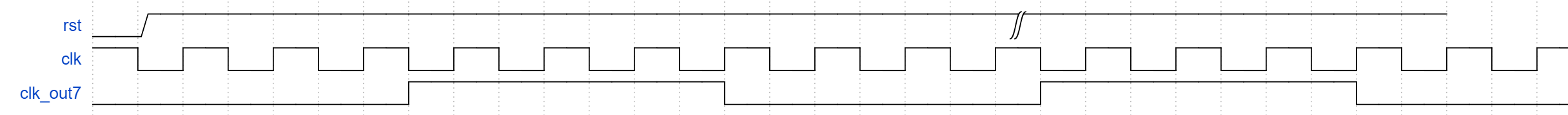

信号示意图:

clk_pos是周期为7且在clk_in上升沿翻转的信号, clk_neg是周期为7且在clk_in下降沿翻转的信号。

代码

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

|

`timescale 1ns/1nsmodule odo_div_or ( input wire rst , input wire clk_in, output wire clk_out7 );//*************code***********// reg clk_neg, clk_pos; reg [2:0] cnt; always@(posedge clk_in or negedge rst) begin if(~rst) cnt <= 0; else cnt <= cnt==6? 0: cnt+1; end always@(posedge clk_in or negedge rst) begin if(~rst) clk_pos <= 0; else clk_pos <= cnt==3||cnt==6? ~clk_pos: clk_pos; end always@(negedge clk_in or negedge rst) begin if(~rst) clk_neg <= 0; else clk_neg <= cnt==3||cnt==6? ~clk_neg: clk_neg; end assign clk_out7 = clk_neg|clk_pos;//*************code***********//endmodule |

分类:

FPGA笔试题

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 阿里最新开源QwQ-32B,效果媲美deepseek-r1满血版,部署成本又又又降低了!

· 开源Multi-agent AI智能体框架aevatar.ai,欢迎大家贡献代码

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· AI技术革命,工作效率10个最佳AI工具