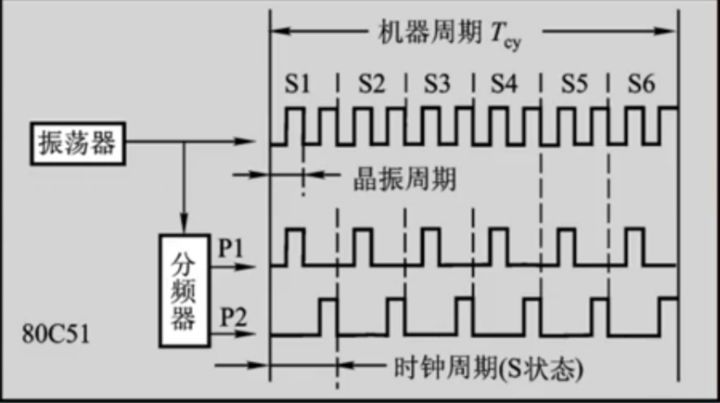

单片机时钟系统

1、晶振的工作原理

石英晶体振荡器是利用石英晶体的压电效这制成的一种谐振器件,它的基本构成大致是:从一块石英晶体上按一定方位角切下薄片,在它的两个对应面上涂敷银层作为电极,在每个电极上各焊―根引线接到管脚上﹐再加上封装外壳就构成了石英晶体谐振器﹐简称为石英晶体或晶体﹑晶振。若在石英晶体的两个电极上加一电场,晶片就会产生机械变形。反之,若在晶片的两侧施加机械压力,则在晶片相应的方向上将产生电场,这种物理现象称为压电效应。

2、晶体振荡器的分类

电脑中的晶体振荡器分为无源晶振和有源晶振两种类型。

无源晶振与有源晶振的英文名称不同,无源晶振为crystal(晶体),而有源晶振则叫做oscillator(振荡器)。

晶体是有2个引脚或者4个引脚的无极性元件,需要借助于时钟电路才能产生振荡信号,自身无法振荡起来;有源晶振有4个引脚或者6个引脚,是一个完整的振荡器,其中除了石英晶体外,还有晶体管和阻容元件﹐因此体积较大。

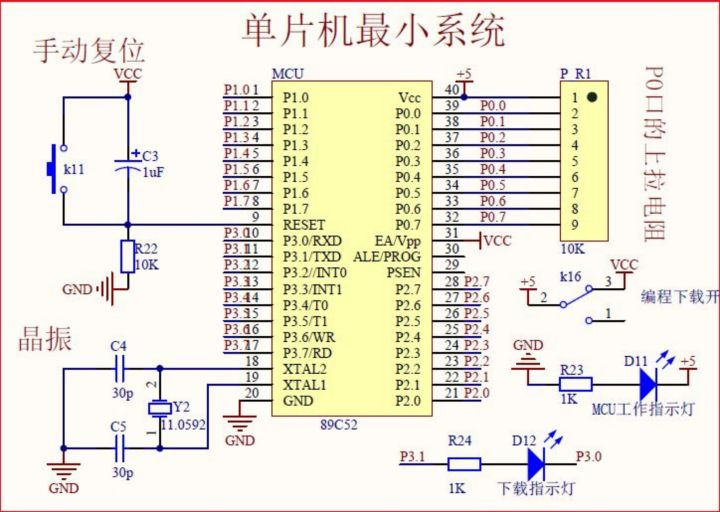

3、单片机的内部时钟与外部时钟

单片机有内部时钟方式和外部时钟方式两种:

( 1)单片机的XTAL1和XTAL2内部有一片内振荡器结构,但仍需要在XTAL1和XTAL2两端连接一个晶振和两个电容才能组成时钟电路﹐这种使用晶振配合产生信号的方法是内部时钟方式;

( 2)单片机还可以工作在外部时钟方式下,外部时钟方式较为简单,可直接向单片机XTAL1引脚输入时钟信号方波,而XTAL2管脚悬空。

外部时钟方式相对内部时钟较为方便,大多数单片机系统还是选择内部时钟方式。这是因为单片机的内部振荡器能与晶振、电容构成一个性能非常好的时钟信号源,而如果要产生这样的信号作为外部时钟信号输入到单片机中,则需要添加的器件远不止一个晶振和两个电容这么简单。

晶振是给单片机提供工作信号脉冲的,这个脉冲就是单片机的工作速度。比如12M晶振单片机工作速度就是每秒12M。当然,单片机的工作频率是有范围的不能太大一般。24M就不上去了,不然不稳定。

晶振与单片机的脚XTALО和脚XTAL1构成的振荡电路中会产生偕波(也就是不希望存在的其他频率的波)这个波对电路的影响不大。但会降低电路的时钟振荡器的稳定性。为了电路的稳定性起见ATMEL公司只是建议在晶振的两引脚处接入两个10pf-50pf的瓷片电容接地来削减偕波对电路的稳定性的影响。所以晶振所配的电容在10pf-50pf之间都可以的,没有什么计算公式。

4、时钟电路设计要点

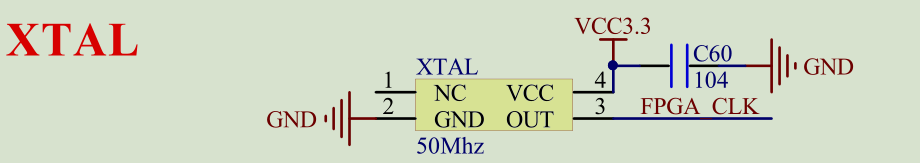

FPGA顶层时钟一般是板载时钟,由外部晶振提供,一般10M到100M ,还有的时钟由时钟芯片提供,单端或差分时钟。

FPGA的顶层设计中模块的时钟大小怎么确定﹖开发版上会有自己的时钟,还可以例化一个 pll。

FPGA的顶层设计中模块的时钟大小怎么确定?

时钟大小一般都说是时钟颡率或者时钟周期。考虑不同情况∶

1、接口类

有些标准接口,协议就定好了时钟频率﹐比如Ethernet 、 USB 、UART等,有些接口,时钟频率没有限定,就由需求来确定时钟频率,比如SPI、I2℃等。

2、系统内部

比如CPU、总线、memory等,关乎到系统的性能﹐希望性能高、时钟频窣就要高。做到尽里低、尽里少。

尽里低是指工作的时钟频率可以尽里设定的比较低,比满足需要的时钟频率略高或者相等。这样可以提高系统的稳定性并且降低功耗。时序也会更加宽松。

尽里少是指时钟域的数里尽里少。不同模块尽里使用相同的时钟频率﹐这样可以有效的减少跨时钟域的情况发生·Xilinx.的FPGA的时钟信号会使用特定的时钟资源,使用过多的时钟频率会导致布线困难。

3、时钟设计(以Xilinx为例)

一般是由FPGA板上提供源时钟,使用FPGA内部MMCM (Mixed-Mode ClockManager-混合模式时钟管理器,实现了最低的抖动和抖动滤波﹐为高性能的FPGA设计提供更高性能的时钟管理功能)。等倍频得到系统所要的时钟,比较简单的设计中,源时钟直接驱动逻辑电路也可以。

为方便约束﹑时钟逻辑最好都写在同一个 module 中﹐包括MMCM﹑BUFG 、BUFGMUX 、 clock Gating 、除频等。

时钟约束不用设计,需要设计的是系统的时钟结构,时钟约束是使用综合工具所支持的语法将时钟结构描述出来,以便工具进行综合。

FPGA设计要点:时钟树

对于FPGA来说,要尽可能避免异步设计,尽可能采用同步设计。同步设计的第一个关键,也是关键中的关键,就是时钟树。

具体设计细则如下:

1)尽可能采用单一时钟﹔

2〉如果有多个时钟域,一定要仔细划分,千万小心

3〉跨时钟域的信号一定要做同步处理。对于控制信号,可以采用双采样﹔对于数据信号,可以采用异步fifo·需要注意的是,异步fifo不是万能的,一个异步fifo也只能解决―定范围内的频差问题。

4〉尽可能将FPGA内部的PLL、DLL( Delay Lock Loop,主要是用于产生―个精准的时间延迟利用起来,这会给你的设计带来大里的好处。

5)对于特殊的Io 接口﹐需要仔细计算Tsu·Teg Th,并利用PLL、DLL、DDIO、管脚可设置的delay 等多种工具来实现。简单对管脚进行工Tsu·T9.Th 的约束往往是不行的。

可能说的不是很确切。这里的时钟树实际上泛指时钟方案﹐主要是时钟域和 PLL等的规划,一般情况下不牵扯到走线时延的详细计算(一般都走全局时钟网络和局部时钟网络,时延固定〉﹐和ASIC中的时钟树不一样。对于ASIC,就必须对时钟网络的设计、布线﹑时延计算进行仔细的分析计算才行。

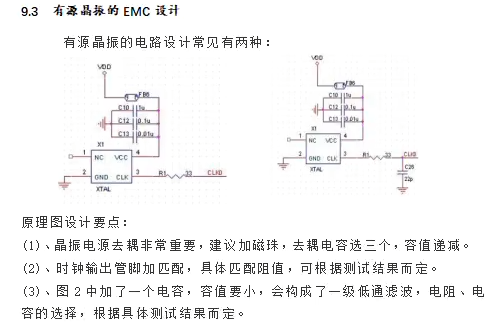

晶振电路选型注意点

1、频率大小:频率越高,价格越高。频率越高,频差越大,从综合角度考虑,一般工程师会选用频率低但稳定的晶振,自己做倍频电路。总之频率的选择是根据需要选择,并不是频率越大就越好。要看具体需求。

2、频率稳定度:ppm

3、电源电压:常用的有1.8T 、2.5V、 3.3、5V等。

STM32单片机的时钟系统:

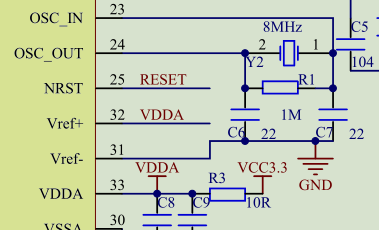

芯片的主晶振频率范围一般来说在数据手册(Datasheet)和技术参考手册(Technical Reference Manual)中都有介绍,对应引脚OSC_IN和OSC_OUT.

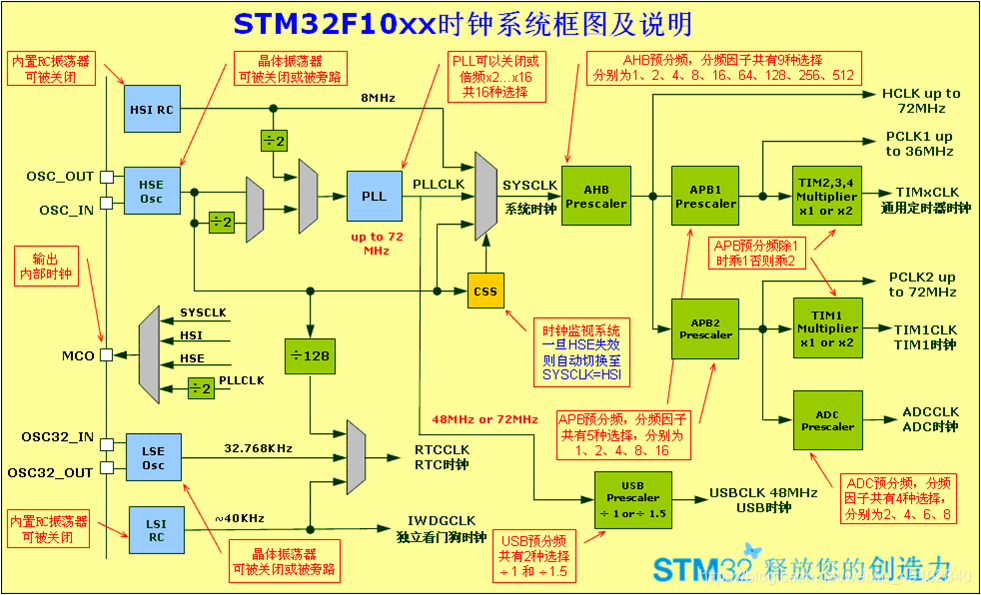

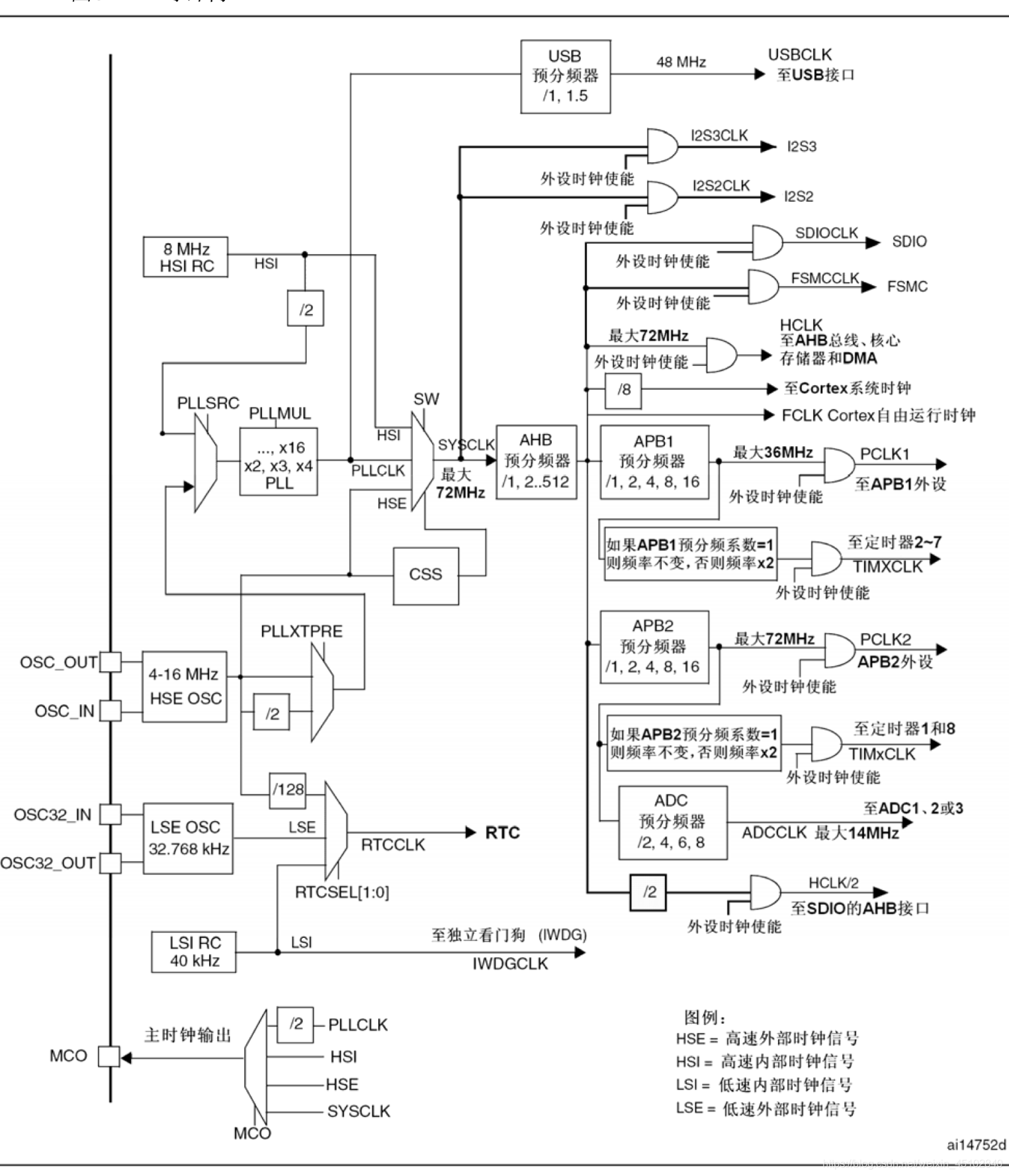

HSI:高速内部时钟,RC振荡器,频率8MHz,精度不高。

HSE:高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz,一般我取8M。

LSI:低速内部时钟,RC振荡器,频率40kHz,低功耗时钟,至WDG独立看门狗。

LSE:低速外部时钟,接频率为32.768kHz的石英晶体或陶瓷谐振器,RTC实时时钟。

PLL:锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。 倍频可选择为2~16倍,其输出频率最大为72MHz。

在这个图的正中央,有一个核心时钟:SYSCLK,它最大频率是72MHz,它的时钟信号通过选择器SW可以由PLLCLK提供(也可由HIS、HSE提供)。

PLL,毫无疑问,它是用来倍频的,可以*2,*3,*4……*16,它的时钟信号通过选择器PLLSRC可以由8MHz的高速内部RC振荡器经过二分频提供,也可由PLLXTPRE的选择器输出提供,

而PLLXTPRE的选择器就接的是我们的8MHz的高速外部时钟(直接接入或二分频接入)。

总的来说,对于我们这个板子,若使用高速外部时钟给STM32内核提供时钟源,一般以下两条路:

① [高速外部时钟:8MHz]>>>[不分频:8MHz]>>>>[PLL倍频,2到16倍]>>>[SYSCLK,16MHz-128MHz]

②[高速外部时钟:8MHz]>>>[二分频:4MHz]>>>>[PLL倍频,2到16倍]>>>[SYSCLK,8MHz-64MHz]

我们注意到,在8MHz外部时钟给PLL之前若分频的话,那么最大(×16)才64MHz,因此,我们都会给PLL以8MHz的时钟源让其倍频,这样能使它发挥到72MHz的高频率

正因如此,系统时钟总是8的倍数。

我们看这个芯片的数据手册,立刻就能明白,不是必须得接8MHz的晶振的

① 高速外部时钟源频率范围(P55-P58):1MHz~25MHz(有源);4MHz~16MHz(无源)

② PLL输入时钟源频率范围(P62):1MHz-25MHz

③ PLL输出时钟源频率范围(P62):16MHz~72MHz

我们自己设计板子的时候只要满足它的范围就可以了。

例如:我们可以选择一个12MHz的无源晶体接到STM32芯片上。

在给STM32进行时钟配置的时候,

① 选择PLLXTMRE的输入源为12MHz/2 = 6MHz

② 选择PLLSRC的输入源为PLLXTMRE的输出6MHz,

③ 在PLL内进行3到12倍的倍频(最小16MHz,最大72MHz),

最终我们可选择的频率就有:18MHz、24MHz、30MHz、36MHz、42MHz、48MHz、54MHz、60MHz、66MHz、72MHz

参考https://blog.csdn.net/weixin_42341666/article/details/108526787

51单片机:

链接:https://www.zhihu.com/question/30930577/answer/2365562178

FPGA时钟:

FPGA的晶振是50MHz,50MHz = 50_000_000Hz = 1/50_000_000s = 20ns

即每次时钟(clk)上升沿(posedge)每50Mhz(20ns)到来一次。属于有源晶振

always@(posedge clk)

浙公网安备 33010602011771号

浙公网安备 33010602011771号