Cadence Sigrity仿真--Power Si 特征阻抗和耦合检查

高速信号在传输的过程中由于layout走线的不良会导致反射串扰等信号完整性问题,可以在布完线之后使用Power Si进行分析。

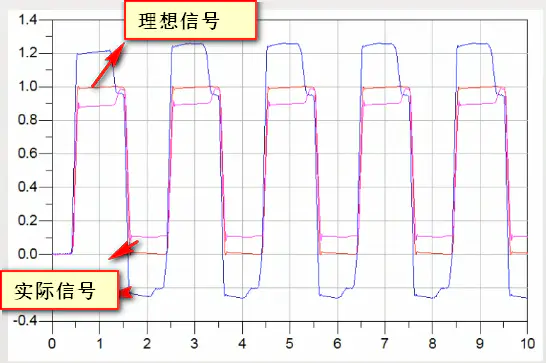

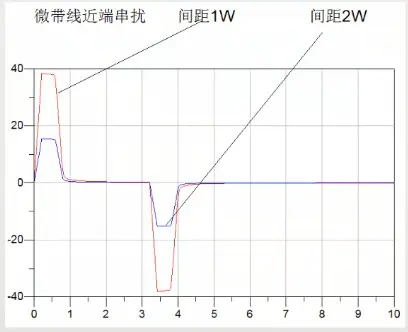

阻抗不匹配导致的反射失真

串扰

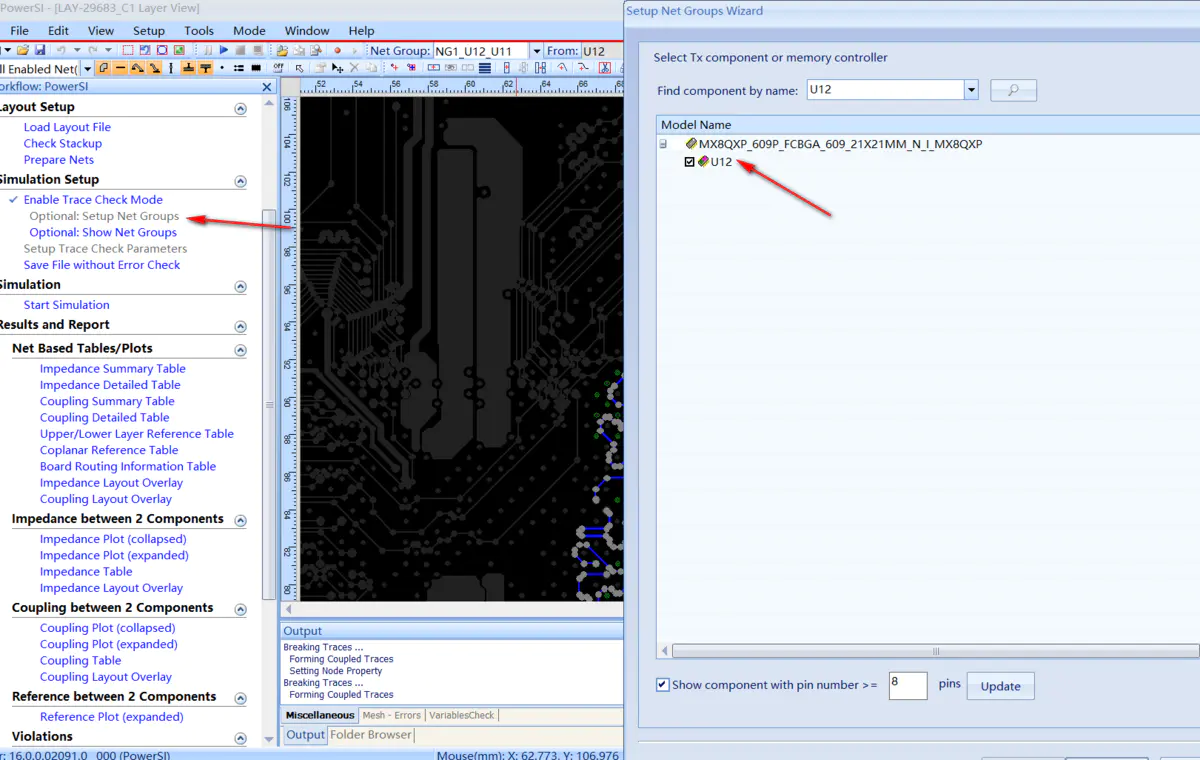

1. 打开PowerSI,load layout file

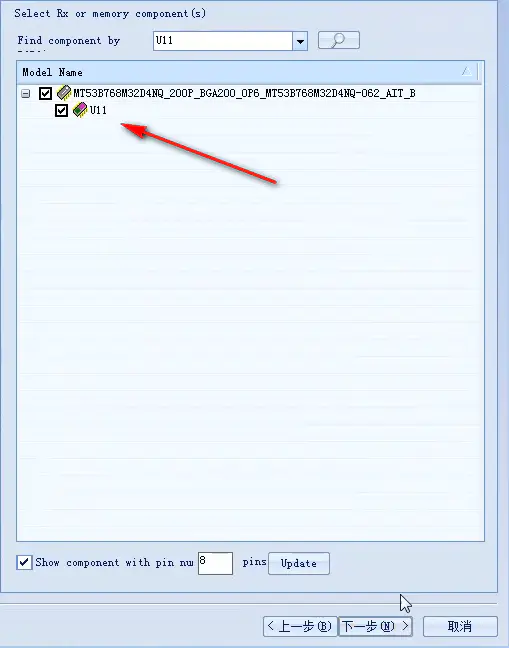

2. 点击“Setup Net Groups”,选择信号的发送和接受器件,这里勾选这个线路的CPU U12,DDR颗粒U11,点击下一步。

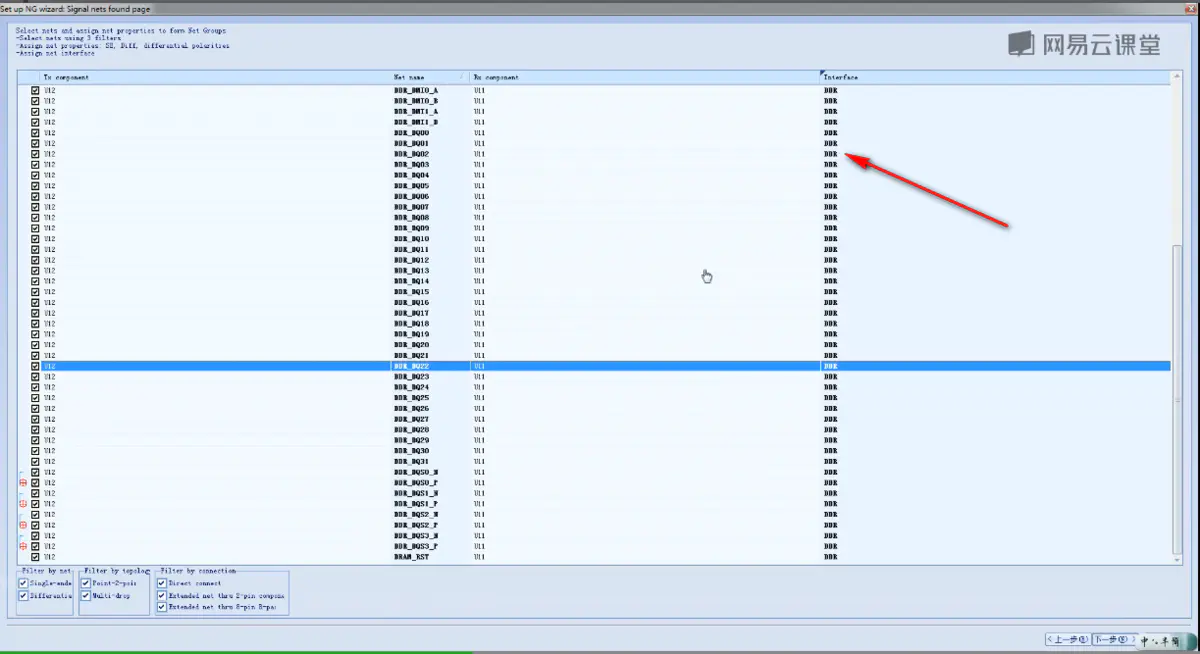

3. 确认电源网络/GND网络,直接点击下一步到分组界面,因为只是练习,我们把DDR的地址和数据等信号都分为一个组,真正项目需要分清楚;点击第一个,再shift点击最后一个,全分为一个组,命名为DDR,然后直接到finish。

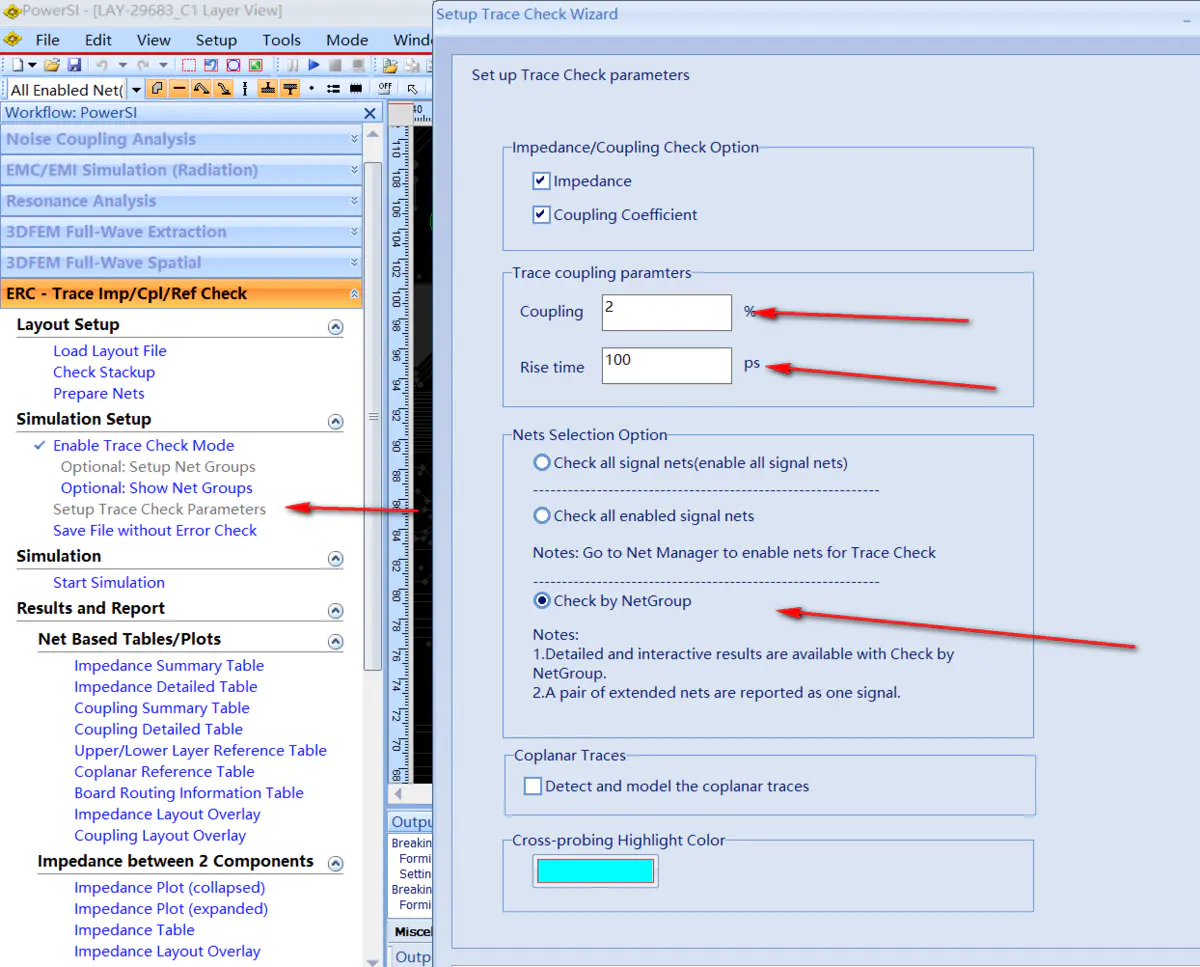

4、点击“Setup Trace Check Parameters”设置检查参数,默认是勾选阻抗和耦合,设置显示耦合2%以上,选择“根据group检查”,点击OK,开始仿真。

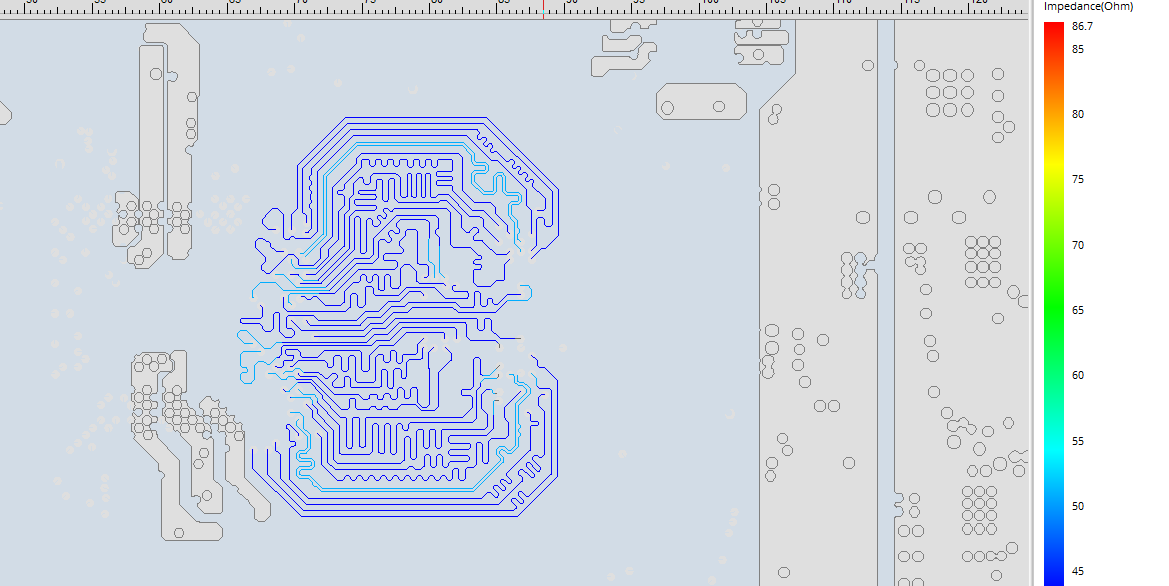

impedance layout overlay会将CPU和DDR的走线以layout的形式显示出来,根据颜色区分。

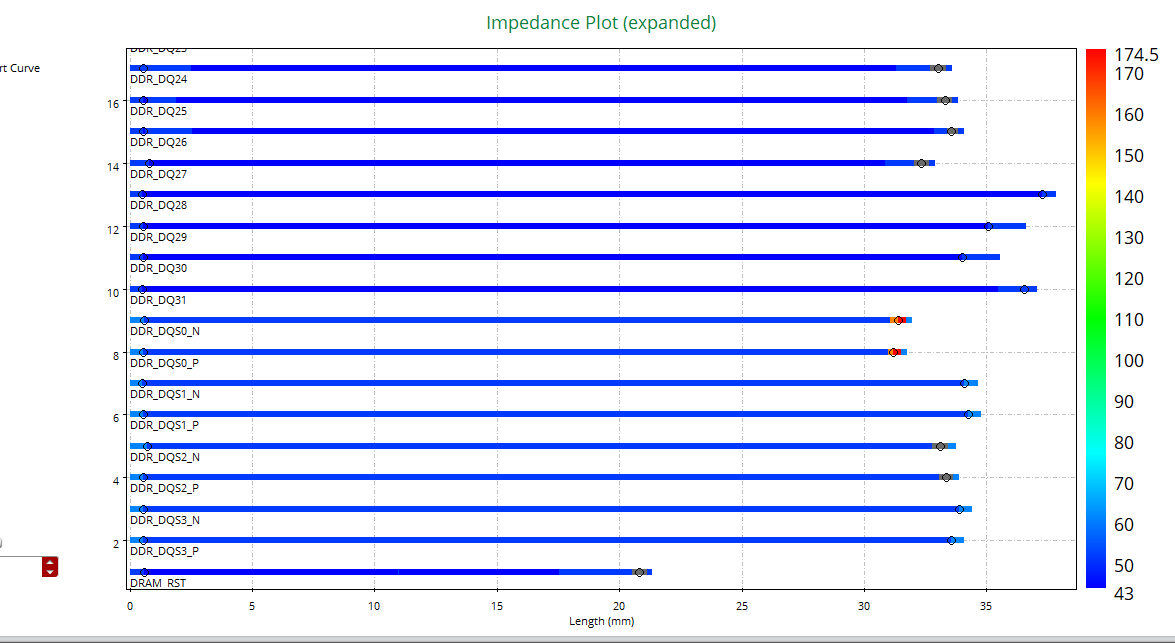

阻抗柱状图也比较直观,每条线摘出来,这里不仅可以看到哪个地方阻抗偏高偏低,还可以看到走线长度。

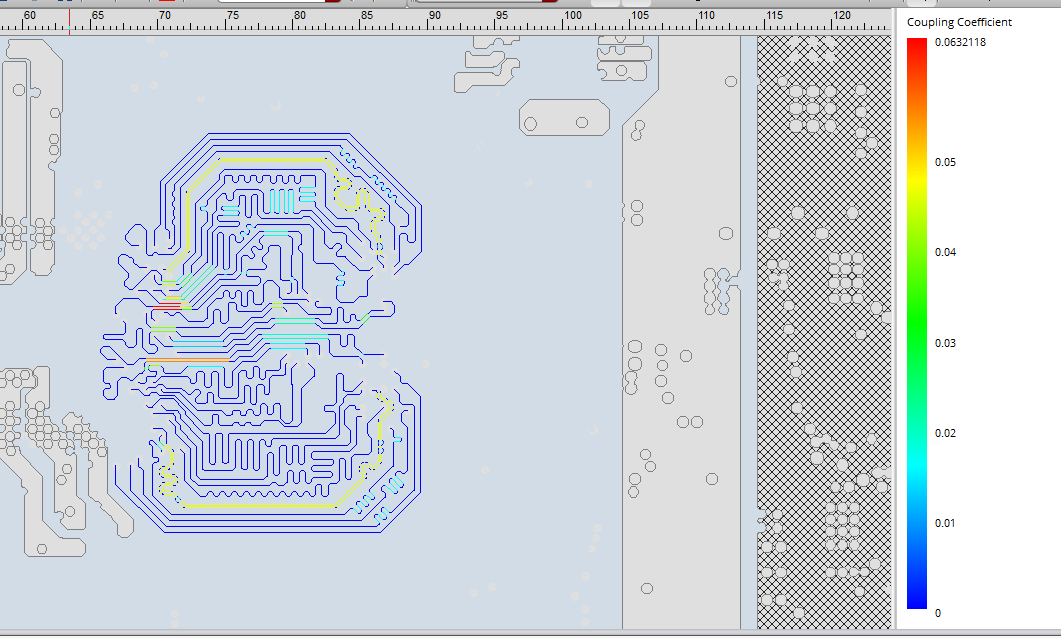

coupling layout overlay通过颜色深浅将串扰强度表现出来,可以看出走线越近的地方串扰越大,一般低于5%信号质量不会受到太大影响。