【牛客】8 企业真题

VL59 根据RTL图编写Verilog程序

这题比较简单,照着写就好了。

`timescale 1ns/1ns module RTL( input clk, input rst_n, input data_in, output reg data_out ); reg data_in_reg; always@(posedge clk) begin if(~rst_n) begin data_in_reg <= 1'b0; data_out <= 1'b0; end else begin data_in_reg <= data_in; data_out <= data_in&~data_in_reg; end end endmodule

VL60 使用握手信号实现跨时钟域数据传输

题目只给了一个模块的接口,实际看testbench要写两个模块。

一开始用状态机写的,实在和答案对不上,还是照着题解写了。单bit数据跨时钟域常用方法:打两拍。

`timescale 1ns/1ns module data_driver( input clk_a, input rst_n, input data_ack, output reg [3:0]data, output reg data_req ); reg data_ack_reg_1; reg data_ack_reg_2; always @ (posedge clk_a or negedge rst_n) begin if (!rst_n) begin data_ack_reg_1 <= 1'b0; data_ack_reg_2 <= 1'b0; end else begin data_ack_reg_1 <= data_ack; data_ack_reg_2 <= data_ack_reg_1; end end always@(posedge clk_a or negedge rst_n) begin if(~rst_n) data <= 'd0; else if(~data_ack_reg_2&data_ack_reg_1)//每次传输结束数据+1 data <= data + 1'b1; end reg [3:0]count; always@(posedge clk_a or negedge rst_n) begin if(~rst_n) count <= 'd0; else if(~data_req) count <= count + 1; else count <= 0; end always@(posedge clk_a or negedge rst_n) begin if(~rst_n) data_req <= 'd0; else if(count == 4) data_req <= 1'b1; else if(~data_ack_reg_2&data_ack_reg_1)//传输结束,data_req清零 data_req <= 1'b0; end endmodule module data_receiver( input clk_b, input rst_n, input [3:0]data, input data_req, output reg data_ack ); reg data_req_reg_1; reg data_req_reg_2; always @ (posedge clk_b or negedge rst_n) begin if (!rst_n) begin data_req_reg_1 <= 0; data_req_reg_2 <= 0; end else begin data_req_reg_1 <= data_req; data_req_reg_2 <= data_req_reg_1; end end always@(posedge clk_b or negedge rst_n) begin if(~rst_n) data_ack <= 1'b0; else if(data_req_reg_2 == 1'b1) data_ack <= 1'b1; else data_ack <= 1'b0; end endmodule

VL61 自动售卖机

感觉用计数器会很简单,状态机复杂一点,不过题目要求用状态机那就用吧。

看了一下,感觉两个状态应该就够了,一个状态代表售卖机内没钱,一个状态代表售卖机内有5元钱。

`timescale 1ns/1ns module sale( input clk , input rst_n , input sel ,//sel=0,5$dranks,sel=1,10&=$drinks input [1:0] din ,//din=1,input 5$,din=2,input 10$ output reg [1:0] drinks_out,//drinks_out=1,output 5$ drinks,drinks_out=2,output 10$ drinks output reg change_out ); reg state,next_state; localparam S0=0,S1=1; always@(posedge clk or negedge rst_n) begin if(~rst_n) state <= S0; else state <= next_state; end always@(*) begin case(state) S0:begin//0 if(sel==0&&din==1||sel==1&&din==2) next_state = S0; else if(sel==1&&din==1) next_state = S1; else next_state = S0; end S1:begin//5 next_state = din?S0:S1; end endcase end always@(posedge clk or negedge rst_n) begin if(~rst_n)begin drinks_out <= 0; change_out <= 0; end else begin case(state) S0:begin if(sel==0&&din==1)begin drinks_out <= 1; change_out <= 0; end else if(sel==1&&din==2)begin drinks_out <= 2; change_out <= 0; end else if(sel==0&&din==2)begin drinks_out <= 1; change_out <= 1; end else begin drinks_out <= 0; change_out <= 0; end end S1:begin if(sel==0&&din==1)begin drinks_out <= 1; change_out <= 1; end else if(sel==1&&din==2)begin drinks_out <= 2; change_out <= 1; end else if(sel==1&&din==1)begin drinks_out <= 2; change_out <= 0; end else begin drinks_out <= 0; change_out <= 0; end end endcase end end endmodule

VL62 序列发生器

直接移位寄存器秒了,不过用状态机的话所用寄存器会少一点。

`timescale 1ns/1ns module sequence_generator( input clk, input rst_n, output reg data ); reg [5:0]data_reg; always@(posedge clk or negedge rst_n) begin if(~rst_n)begin data_reg <= 6'b001011; data <= 1'b0; end else begin data_reg <= {data_reg[4:0],data_reg[5]}; data <= data_reg[5]; end end endmodule

VL63 并串转换

说是华为暑期实习的题,感觉题目出的一般,不懂是要考啥。

`timescale 1ns/1ns module huawei5( input wire clk , input wire rst , input wire [3:0]d , output wire valid_in , output wire dout ); //*************code***********// reg [3:0]data; reg valid; reg [1:0]count; always@(posedge clk or negedge rst) begin if(!rst)begin data <= 'd0; valid <= 1'b0; count <= 'd0; end else begin if(count == 'd3)begin valid <= 1'b1; count <= 0; data <= d; end else begin valid <= 1'b0; count <= count + 1; data <= data << 1; end end end assign dout = data[3]; assign valid_in = valid; //*************code***********// endmodule

VL64 时钟切换

核心是没有毛刺,我以为把sel打两拍用来控制就行了,结果发现想简单了。参考(数字 IC 设计)5.4 时钟切换 - 知乎 (zhihu.com)

为了防止两个输出产生毛刺,两个时钟不能进行相反的极性转换,由图中clk0和clk1可以看出clk0的上升沿和clk1的下降沿是重合的。为避免毛刺的产生,需要在两个时钟都为低电平的时候进行时钟切换。

反馈信号q1

`timescale 1ns/1ns module huawei6( input wire clk0 , input wire clk1 , input wire rst , input wire sel , output wire clk_out ); //*************code***********// reg q0, q1; always@(negedge clk0 or negedge rst) if(!rst) q0 <= 0; else q0 <= ~sel & ~q1; always@(negedge clk1 or negedge rst) if(!rst) q1 <= 0; else q1 <= sel & ~q0; assign clk_out = (q0 & clk0) | (q1 & clk1); //*************code***********// endmodule

VL65 状态机与时钟分频

也可以用四个状态,更简单一点。

`timescale 1ns/1ns module huawei7( input wire clk , input wire rst , output reg clk_out ); //*************code***********// reg[1:0]count; reg state,next_state; localparam S0=0,S1=1; always@(posedge clk or negedge rst) begin if(!rst) state <= S0; else state <= next_state; end always@(*) begin case(state) S0:next_state=S1; S1:next_state=(count==2)?S0:S1; endcase end always@(posedge clk or negedge rst) begin if(!rst) clk_out <= 1'b0; else begin if(state==S0) clk_out <= 1'b1; else clk_out <= 1'b0; end end always@(posedge clk or negedge rst) begin if(!rst) clk_out <= 1'b0; else begin if(state==S1) count <= count + 1; else count <= 0; end end //*************code***********// endmodule

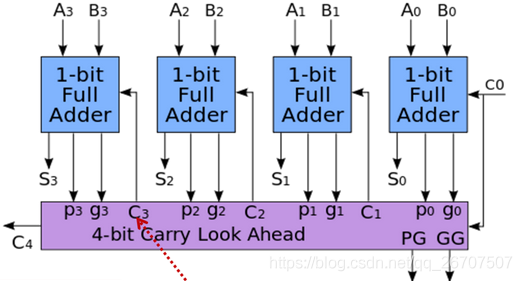

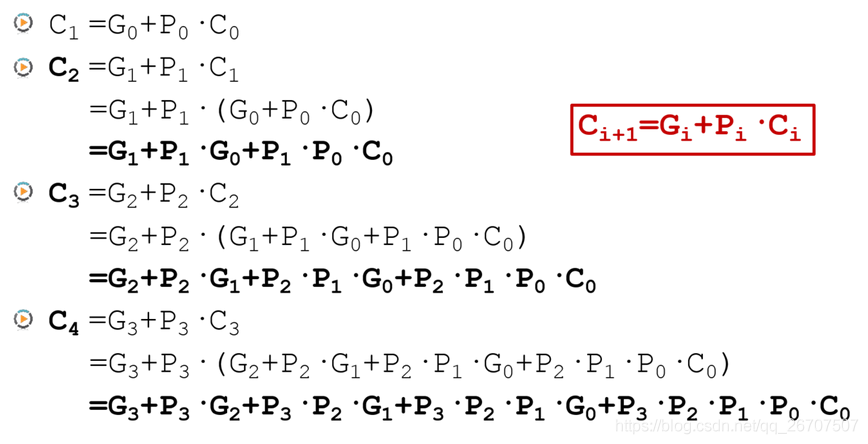

VL66 超前进位加法器

超前进位加法器原理:

注意!进位C必须要拆开划成最后那个表达式,不然Cn+1需要Cn的值的话,仍然会导致组合逻辑越来越长。划成最后的表达式,Ci始终是三级组合逻辑:1、P、G的运算 2、多输入与门 3、或门。

`timescale 1ns/1ns module huawei8//四位超前进位加法器 ( input wire [3:0]A, input wire [3:0]B, output wire [4:0]OUT ); //*************code***********// wire [3:0] G; wire [3:0] P; wire [3:0] F; wire [4:1] C; Add1 u0 ( .a(A[0]), .b(B[0]), .C_in(1'b0), .f(F[0]), .g(G[0]), .p(P[0]) ); Add1 u1 ( .a(A[1]), .b(B[1]), .C_in(C[1]), .f(F[1]), .g(G[1]), .p(P[1]) ); Add1 u2 ( .a(A[2]), .b(B[2]), .C_in(C[2]), .f(F[2]), .g(G[2]), .p(P[2]) ); Add1 u3 ( .a(A[3]), .b(B[3]), .C_in(C[3]), .f(F[3]), .g(G[3]), .p(P[3]) ); CLA_4 u4 ( .P(P), .G(G), .C_in(C_in), .Ci(C), .Gm(), .Pm() ); assign OUT={C[4],F}; //*************code***********// endmodule //////////////下面是两个子模块//////// module Add1 ( input a, input b, input C_in, output f, output g, output p ); assign f = a^b^C_in;//每一位的输出 assign g = a&b;//生成信号 assign p = a|b;//传播信号 endmodule //CLA Carry Look Ahead module CLA_4( input [3:0]P, input [3:0]G, input C_in, output [4:1]Ci, output Gm, output Pm ); assign Ci[1]=G[0]|P[0]&C_in; assign Ci[2]=G[1]|P[1]&G[0]|P[1]&P[0]&C_in; assign Ci[3]=G[2]|P[2]&G[1]|P[2]&P[1]&G[0]|P[2]&P[1]&P[0]&C_in; assign Ci[4]=G[3]|P[3]&G[2]|P[3]&P[2]&G[1]|P[3]&P[2]&P[1]&G[0]|P[3]&P[2]&P[1]&P[0]&C_in; //注意这里一定要拆开写,不然就和行波进位加法器差不多了。 //Gm和Pm是用来拓展更高位加法器的。 assign Gm=G[3]|P[3]&G[2]|P[3]&P[2]&G[1]|P[3]&P[2]&P[1]&G[0]; assign Pm=P[3]&P[2]&P[1]&P[0]; endmodule

VL67 十六进制计数器

这题放这里多少有点离谱。。

`timescale 1ns/1ns module counter_16( input clk , input rst_n , output reg [3:0] Q ); always @(posedge clk or negedge rst_n) begin if (!rst_n) begin Q <= 4'b0; end else begin Q <= Q +1'b1; end end endmodule

VL68 同步FIFO

之前写过,注意按题目给的接口,reg输出wfull和rempty会晚一个周期。实际要么在下一个读/写要空/满的时候通过reg输出,或者组合逻辑输出。

`timescale 1ns/1ns /**********************************RAM************************************/ module dual_port_RAM #(parameter DEPTH = 16, parameter WIDTH = 8)( input wclk ,input wenc ,input [$clog2(DEPTH)-1:0] waddr ,input [WIDTH-1:0] wdata ,input rclk ,input renc ,input [$clog2(DEPTH)-1:0] raddr ,output reg [WIDTH-1:0] rdata ); reg [WIDTH-1:0] RAM_MEM [0:DEPTH-1]; always @(posedge wclk) begin if(wenc) RAM_MEM[waddr] <= wdata; end always @(posedge rclk) begin if(renc) rdata <= RAM_MEM[raddr]; end endmodule /**********************************SFIFO************************************/ module sfifo#( parameter WIDTH = 8, parameter DEPTH = 16 )( input clk , input rst_n , input winc , input rinc , input [WIDTH-1:0] wdata , output reg wfull , output reg rempty , output wire [WIDTH-1:0] rdata ); parameter ADDR_WIDTH = $clog2(DEPTH); reg [ADDR_WIDTH:0]waddr,raddr;//多一位用于比较空满 always@(posedge clk or negedge rst_n) begin if(~rst_n) waddr <= 'd0; else if(winc&&~wfull) waddr <= waddr + 1; end always@(posedge clk or negedge rst_n) begin if(~rst_n) raddr <= 'd0; else if(rinc&&~rempty) raddr <= raddr + 1; end /*空满判断*/ always@(posedge clk or negedge rst_n) begin if(~rst_n)begin wfull <= 'd0; rempty <= 'd0; end else begin wfull <= (waddr[ADDR_WIDTH]==~raddr[ADDR_WIDTH])&&(waddr[ADDR_WIDTH-1:0]==raddr[ADDR_WIDTH-1:0]); rempty <= (raddr==waddr); end end dual_port_RAM #(.WIDTH(WIDTH),.DEPTH(DEPTH)) U0( .wclk(clk), .wenc(winc&&~wfull), .waddr(waddr[ADDR_WIDTH-1:0]), .wdata(wdata), .rclk(clk), .renc(rinc&&~rempty), .raddr(raddr[ADDR_WIDTH-1:0]), .rdata(rdata) ); endmodule

VL69 脉冲同步器(快到慢)

又是在前面做过的题。【牛客】6 跨时钟域传输 - Magnolia666 - 博客园 (cnblogs.com)

sig_a在时钟域a持续一个周期,在这个周期翻转toggle电平,下一个脉冲再恢复toggle低电平,把toggle信号在时钟域b打两拍,再恢复成单周期脉冲。

`timescale 100ps/100ps module pulse_detect( input clka , input clkb , input rst_n , input sig_a , output sig_b ); reg toggle; always@(posedge clka or negedge rst_n) begin if(!rst_n) toggle <= 1'b0; else toggle <= sig_a?~toggle:toggle; end reg [2:0]sig_syn; always@(posedge clkb or negedge rst_n) begin if(!rst_n) sig_syn <= 'd0; else begin sig_syn <= {sig_syn[1:0],toggle}; end end assign sig_b = sig_syn[2]^sig_syn[1]; endmodule

VL70 序列检测器(Moore型)

要求使用Moore状态机,也就是输出只和状态有关,注意是不重叠检测。

`timescale 1ns/1ns module det_moore( input clk , input rst_n , input din , output reg Y ); reg[2:0]state,next_state; localparam S0=0,S1=1,S2=2,S3=3,S4=4; always@(posedge clk or negedge rst_n) begin if(!rst_n) state <= S0; else state <= next_state; end always@(*) begin case(state) S0:next_state = din?S1:S0; S1:next_state = din?S2:S0; S2:next_state = din?S2:S3; S3:next_state = din?S4:S0; S4:next_state = din?S1:S0; endcase end always@(posedge clk or negedge rst_n) begin if(!rst_n) Y <= 1'b0; else begin if(state == S4) Y <= 1'b1; else Y <= 1'b0; end end endmodule

VL71 乘法与位运算

要求资源最少,那肯定是移位资源少了。

`timescale 1ns/1ns module dajiang13( input [7:0] A, output [15:0] B ); //*************code***********// assign B = (A<<8)-(A<<2)-A; //*************code***********// endmodule

VL72 全加器

要求使用半加器实现全加器。半加器没有低位的进位,全加器有。

我写的:

`timescale 1ns/1ns module add_half( input A , input B , output wire S , output wire C ); assign S = A ^ B; assign C = A & B; endmodule /***************************************************************/ module add_full( input A , input B , input Ci , output wire S , output wire Co ); wire S_half,C_half; assign S = S_half^Ci; assign Co = C_half | (A&Ci) |(B&Ci); add_half u0( .A(A), .B(B), .S(S_half), .C(C_half) ); endmodule

看了一下答案,其实可以用两个半加器实现全加器:

`timescale 1ns/1ns module add_half( input A , input B , output wire S , output wire C ); assign S = A ^ B; assign C = A & B; endmodule /***************************************************************/ module add_full( input A , input B , input Ci , output wire S , output wire Co ); wire S1,Co1,Co2; add_half u0( .A(A), .B(B), .S(S1), .C(Co1) ); add_half u1( .A(Ci), .B(S1), .S(S), .C(Co2) ); assign Co = Co1|Co2; endmodule

确实这样写才更合理些。

VL73 串行进位加法器

或者叫行波进位加法器,加法器级联即可。

`timescale 1ns/1ns module add_4( input [3:0] A , input [3:0] B , input Ci , output wire [3:0] S , output wire Co ); wire [3:1]C; add_full u0( .A(A[0]), .B(B[0]), .Ci(Ci), .S(S[0]), .Co(C[1]) ); add_full u1( .A(A[1]), .B(B[1]), .Ci(C[1]), .S(S[1]), .Co(C[2]) ); add_full u2( .A(A[2]), .B(B[2]), .Ci(C[2]), .S(S[2]), .Co(C[3]) ); add_full u3( .A(A[3]), .B(B[3]), .Ci(C[3]), .S(S[3]), .Co(Co) ); endmodule

VL74 异步复位同步释放

对复位信号做两级同步,消除亚稳态,具体可以参考【《硬件架构的艺术》读书笔记】02 时钟和复位(3) - Magnolia666 - 博客园 (cnblogs.com)

`timescale 1ns/1ns module ali16( input clk, input rst_n, input d, output reg dout ); //*************code***********// reg [1:0]rst_n_syn; always@(posedge clk or negedge rst_n) begin if(~rst_n) rst_n_syn <= 2'b0; else rst_n_syn <= {rst_n_syn[0],1'b1}; end always@(posedge clk or negedge rst_n_syn[1]) begin if(~rst_n_syn[1]) dout <= 1'b0; else dout <= d; end //*************code***********// endmodule

VL75 求最小公倍数

查了一下,求最大公约数用的辗转相除法,又想起了高中被数论支配的恐惧。

原理:两个数的最大公约数等于它们中较小的数和两数之差的最大公约数。

求最小公倍数则根据最小公倍数等于两数之积除以他们的最大公约数,可以直接用一个'/'表示。

不过这里标答写的两段式代码感觉有点奇怪,每次状态跳变都会多延一个周期。下面我修改之后的代码。

`timescale 1ns/1ns module lcm#( parameter DATA_W = 8) ( input [DATA_W-1:0] A, input [DATA_W-1:0] B, input vld_in, input rst_n, input clk, output wire [DATA_W*2-1:0] lcm_out, output wire [DATA_W-1:0] mcd_out, output reg vld_out ); reg [DATA_W*2-1:0] mcd,a_buf,b_buf; reg [DATA_W*2-1:0] mul_buf; reg [1:0] cur_st,nxt_st; parameter IDLE= 2'b00,S0 = 2'b01, S1 = 2'b10; always @(posedge clk or negedge rst_n) if (!rst_n) cur_st <= IDLE; else cur_st <= nxt_st; always@(*) begin case(cur_st) IDLE:nxt_st = vld_in?S0:IDLE; S0:nxt_st = (a_buf==b_buf)?S1:S0; S1:nxt_st = IDLE; default:nxt_st = IDLE; endcase end always @(posedge clk or negedge rst_n) begin if (!rst_n) begin mcd <= 0; a_buf <= 0; b_buf <= 0; mul_buf <= 0; vld_out <= 1'b0; end else begin case (cur_st) IDLE:if(vld_in) begin a_buf <= A; b_buf <= B; mul_buf <= A*B; vld_out <= 1'b0; end else vld_out <= 1'b0; S0:if(a_buf!=b_buf)begin if(a_buf>b_buf) a_buf <= a_buf - b_buf; else b_buf <= b_buf - a_buf; end S1:begin mcd <= b_buf; vld_out <= 1'b1; end endcase end end assign mcd_out = mcd; assign lcm_out = mul_buf/mcd; endmodule

VL76 任意奇数倍时钟分频

也是之前写过的,用一个上升沿计数器和一个下降沿计数器即可。

为了满足题目波形,强行把下降沿时钟提前一个周期翻转了。

`timescale 1ns/1ns module clk_divider #(parameter dividor = 5) ( input clk_in, input rst_n, output clk_out ); reg clk_pos,clk_neg; reg [3:0]cnt0,cnt1; always@(posedge clk_in or negedge rst_n) begin if(~rst_n)begin clk_pos <= 1'b0; cnt0 <= 'd0; end else begin cnt0 <= (cnt0 <dividor-1)?cnt0+1:0; if(cnt0==dividor-1||cnt0==(dividor-1)/2) clk_pos <= ~clk_pos; end end always@(negedge clk_in or negedge rst_n) begin if(~rst_n)begin clk_neg <= 1'b0; cnt1 <= 'd0; end else begin cnt1 <= (cnt1 <dividor-1)?cnt1+1:0; if(cnt1==dividor-2||cnt1==(dividor-1)/2-1) clk_neg <= ~clk_neg; end end assign clk_out = clk_pos|clk_neg; endmodule

VL77 编写乘法器求解算法表达式

主要就是要写一个4bit乘法器,用移位实现即可;

感觉自己代码没错,不知道为啥牛客一直出错

`timescale 1ns/1ns module calculation( input clk, input rst_n, input [3:0] a, input [3:0] b, output [8:0] c ); wire [8:0]c1,c2; mult4 u0( .clk(clk), .rst_n(rst_n), .a(12), .b(a), .c(c1) ); mult4 u1( .clk(clk), .rst_n(rst_n), .a(5), .b(b), .c(c2) ); assign c = c1+c2; endmodule module mult4( input clk, input rst_n, input [3:0] a, input [3:0] b, output reg[8:0] c ); wire [8:0]c_temp[3:0]; genvar i; generate for(i=0;i<4;i=i+1) assign c_temp[i] = a[i]?b<<i:0; endgenerate always@(posedge clk or negedge rst_n) begin if(!rst_n) c <= 'd0; else begin c <= c_temp[0] + c_temp[1] + c_temp[2] + c_temp[3]; end end endmodule

总算是刷完了,刷这个还是浪费了很多时间的,题目质量一般,而且还经常出错。接下来要好好准备实习了。