【《硬件架构的艺术》读书笔记】09 电磁兼容性能设计指南(3)

9.6.3 微控制器级技术

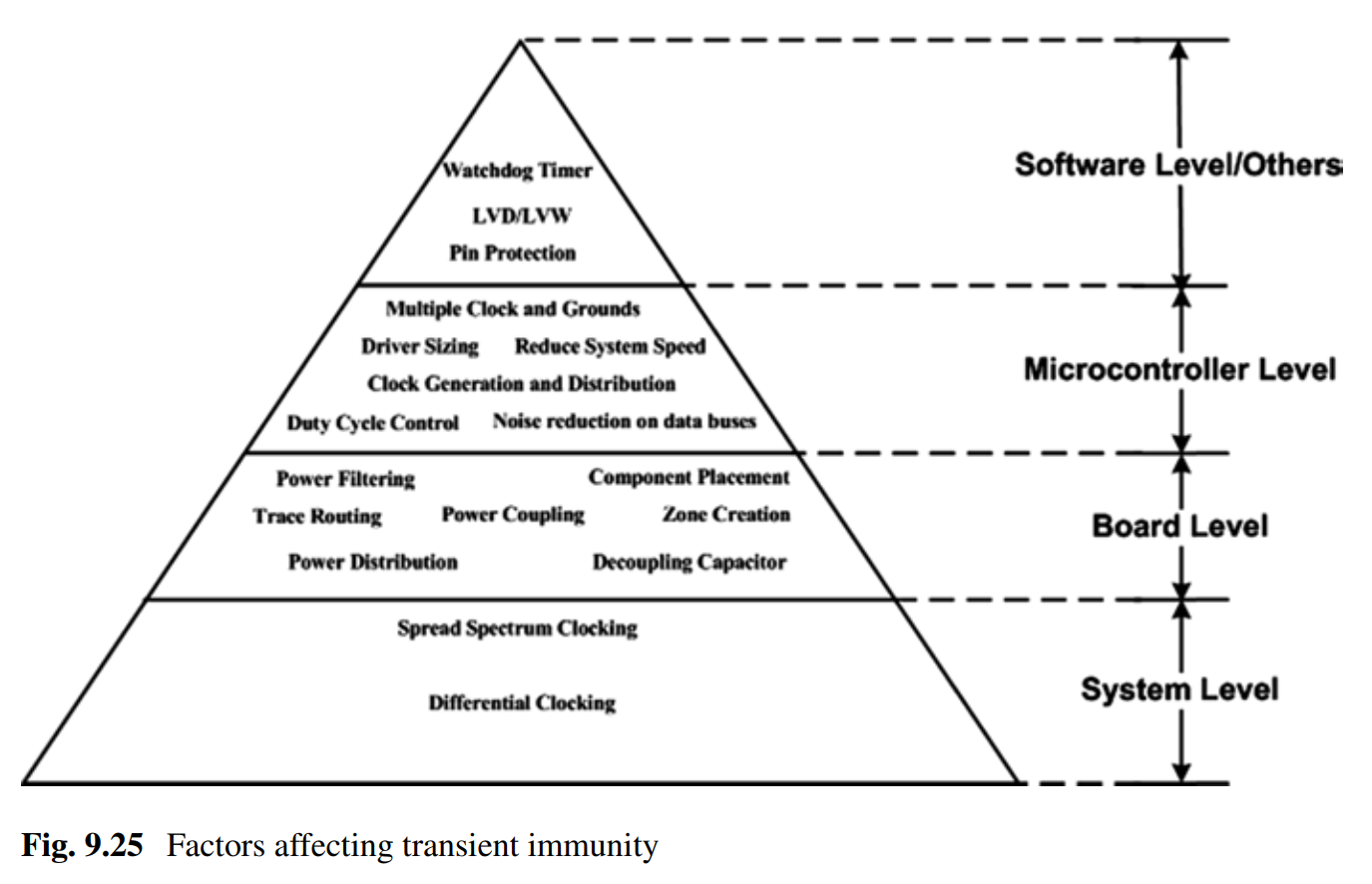

解决噪声问题的最佳途径在源头。

9.6.3.1 多时钟和接地

去耦电容:

1、容量应足够大以在转换时间内提供所需的电流。

2、应足够小以使时钟频率小于电容的谐振频率。

还应遵守:

1、所有电源/地线对中尽可能是均衡电流。

2、除ESD保护外,应避免在内部连接电源引脚和接地引脚。

3、芯片上使用独立的电源-地线对来把有噪声的电路和敏感电路隔离开。

9.6.3.2 消除竞态条件

竞态条件定义了一种条件,即:器件输出取决于输入端两个或多个事件,导致设备输出的转换。这就额外增加了系统噪声。

9.6.3.3 降低系统速度

降低系统工作频率至绝对值最小值。

9.6.3.4 驱动器规格

驱动器对于负载充电的速度快于负载所需速度时,过快的沿速度会将导致过充或下冲。快的转换速率会导致噪声以信号反射、串扰和接地反射等形式产生。

不要试图使用最快的转换速率和最大的驱动电流。减小EMI最重要的设计考虑是从输入及内部驱动器获得适当的上升时间和使峰值电流最小化。

9.6.3.5 时钟产生及分配

不需要时钟时应关闭时钟及振荡器。一个好的方法是宁可支持各种低功耗模式,而不是将时钟限制在较低的频率或完全关闭它。

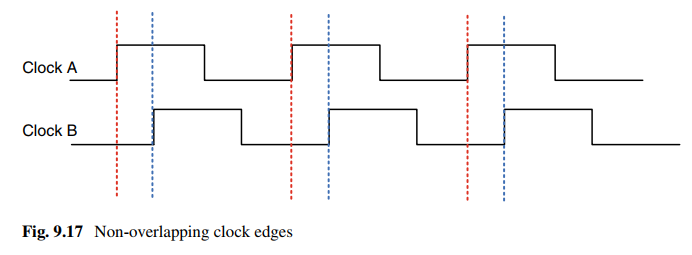

非重叠时钟:具有非一致边沿转换的时钟。非重叠时钟边沿通过多时钟系统的连续脉冲边沿之间的过渡时间,有助于消除竞态条件和亚稳态问题。

从EMC的角度看,加入时钟边沿之间的过渡时间会降低可观察道德峰值电流和电流谐波的峰值幅度。平均电流从时间跨度看保持大致相同,但幅度和频谱形状会发生变化。

另一个技术:调节时钟的上升/下降时间至最小值。

避免在常用频率下运行时钟,防止共振增加噪声。

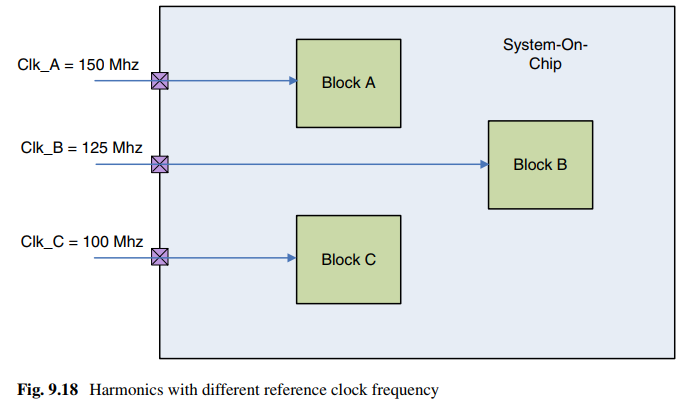

图中是具有多个基准时钟输入的SoC,每个时钟输入馈入SoC中的一个高速区域。

时钟选择不同频率,以便在1GHz以下不会出现同频的谐波。

9.6.3.6 占空比考虑

若占空比正好是50%,所有能量都在奇数谐波。这样,工作在50%的占空比通常是最坏情况。当占空比高于或低于50%,引入了偶次谐波,EMI将按正常情况分布。

9.6.3.7 降低数据总线上的噪声

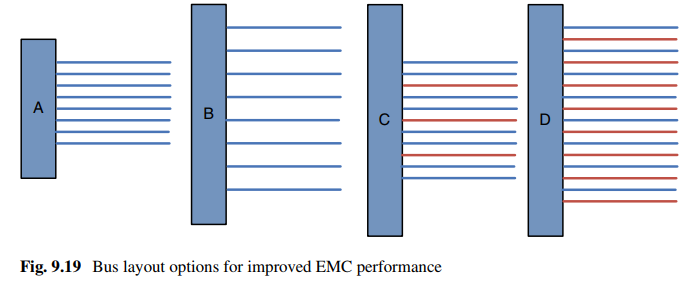

A是所有8条线紧密排列的典型总线布局,这样会引入串扰。

B则通过增加数据线之间的距离来降低噪声。

C则每隔两条数据线插入一条地线。

D接地线与每条数据线交错放置,对全面降低开关噪声非常有效。

9.6.4 软件层级技术

硬件层级完全消除瞬态效应不切实际且费用高昂。

9.6.4.1 通用I/O引脚保护

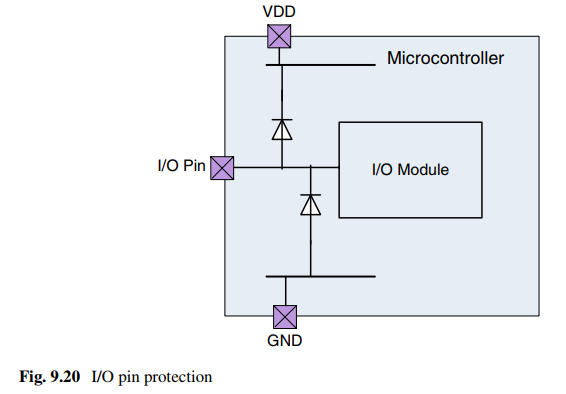

所有常规IO引脚必须在内部有到地和到电源的ESD保护二极管。

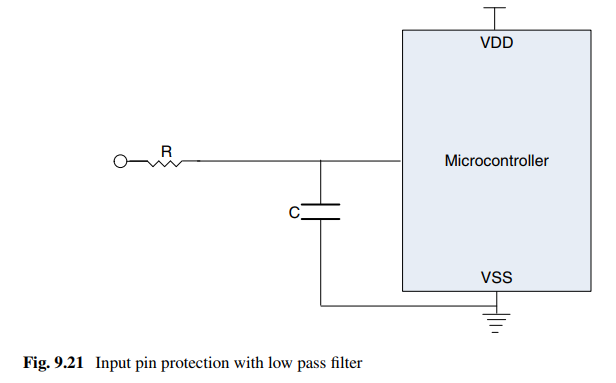

对于具有瞬态波形噪声带宽以外工作带宽的电路,可以使用低通滤波器、高通滤波器或带通滤波器来实现保护。

对于输入的标准保护是低通滤波器。

串联电阻限制了注入电流。并联电容把瞬态电流分流至接地系统,因为它要保持电压在稳态值。

9.6.4.2 数字输入引脚

针对系统中数字输入比较脆弱的情况,可以使用软件滤波消除由外部噪声导致的输入引脚短时脉冲波干扰。

参考前面消抖算法。

9.6.4.3 数字输出和关键寄存器

用户软件应当经常更新输出和关键寄存器,它们控制输出引脚以确保任何轻微故障都会纠正而不发生大问题。

9.6.4.4 复位引脚保护

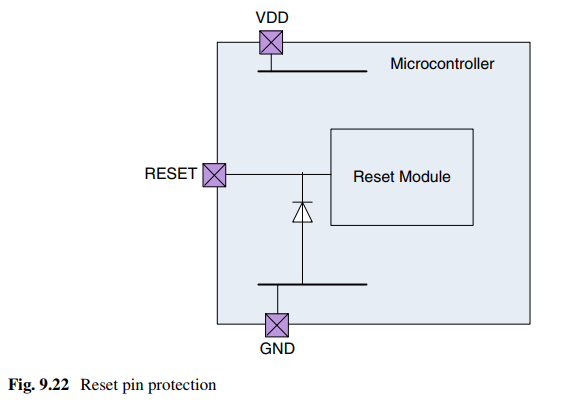

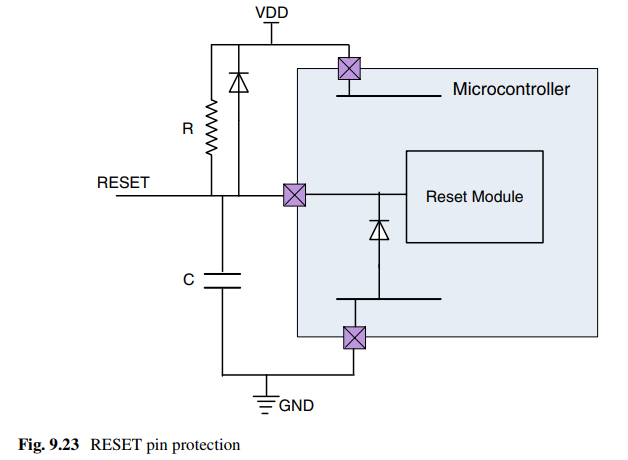

大多数MCU中,在调试或编程时复位引脚是置高的(低电平复位),因此从地到复位引脚只需要保护二极管。

复位从外部驱动,需要另一级别的保护。

电容帮助吸收瞬变电压。

两个二极管把引脚电压钳定在GND-0.7V至VDD+0.7V之间。

9.6.4.5 振荡器和其他敏感引脚

最脆弱的引脚:高阻抗模拟引脚。如用在振荡器电路、锁相环和模拟信号输入的引脚。设计PCB时让这些引脚远离噪声。可将一些数字引脚滤波技术应用到模拟信号输入引脚,如馈入ADC中。

9.6.4.6 看门狗定时器

任何受到噪声影响的系统可能代码跑飞而使系统处于未知状态。一个良好的看门狗定时器应当能够将系统带回安全状态。

1、看门狗定时器宽度应当能覆盖系统中所有可用时钟源的超时范围。尽可能保证用最短的看门狗超时周期以确保代码跑飞状态不会持续太久。

2、看门狗定时器时钟源应独立于其监控的系统的时钟源。

3、看门狗向系统发出故障信号的方法必须是能自身容错的。

4、看门狗关键控制和配置就寄存器位应当有写保护。

5、刷新看门狗的方法应当使跑飞的代码意外刷新的机会最小。

6、反应应当迅速。

7、看门狗的正常运行应当是可测试的。

8、应当能帮助诊断导致看门狗超时的故障。

9、软件实现看门狗(使用噪声关键应用不推荐),避免将看门狗刷新放在中断程序中。

10、任何服务看门狗的循环应当能在有限的时间内给出超时状态。、

9.6.4.7 非法指令和非法地址复位

迅速从跑飞代码状态中恢复系统的另一个可能途径:在出现非法指令/非法地址时产生复位。

9.6.4.8 低电压检测/低电压警告

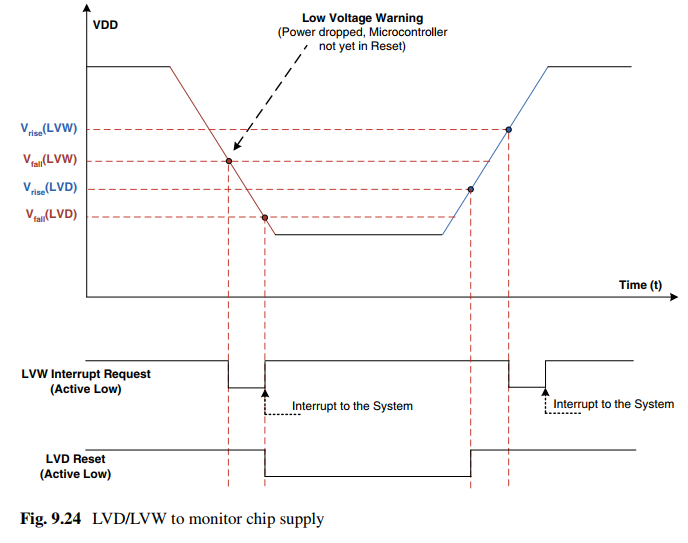

LVD(低电压检测)或LVW(低电压警告)增加了器件的敏感性,对电源线(VDD)的电气干扰和传导噪声提供了更好的抗干扰性。

低电压MCU的性能就无法保证,最坏的情况可能导致数据损坏。强烈建议MCU在这种状态下应自动重置以防止不可预测行为。

LVD应在电源低于Vfail时产生静态复位,直到电压上升到Vrise之上。

Vfail应大于Vrise

LVD应当是可编程的。

9.6.5 其他技术

9.6.5.1 多电源和接地引脚

相邻的接地和电源引脚、多个接地和电源引脚、将电源和接地引脚放在中心都有助于将电源与接地电流路径间的互感最大化,并将自感最小化,减小电源电流的回路面积,使去耦更有效。

9.6.5.2 使用最低频率的技术

频率越低越能减少EMI。

9.7 总结

PS

终于看完这本书了,本来计划上个月看完的,因为疫情(主要是因为懒)等原因,结果这个月才看完。综合来说这本书知识点还是很丰富的,也学到了很多东西,但是这本书很多知识点又不够具体,还是得自己多想多思考。接下来打算仔细看看sky的课(花了我3799大洋,心疼),学学VCS、Verdi、DC和Spyglass等新思全家桶(工作要用),再研究研究STA(非常重要,准备边看书边看邸志雄的课)。

前两天看到自己居然有三个粉丝了,小感动,接下来努力创作一些更有用的东西吧。