【《硬件架构的艺术》读书笔记】06 流水线的艺术(2)

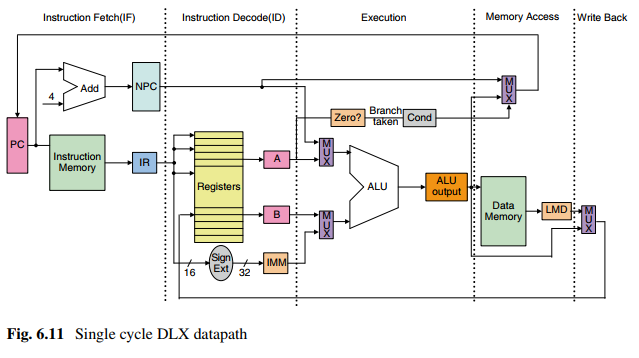

6.6 DLX指令集的实现

这节开始将指令集相关内容,没学过相关知识,看不太懂,就快速浏览一下好了。

DLX指令集包括五个部分:

1、指令获取(IF)

IR <= MEM[PC]

NPC <= PC +4

从存储器中获取指令(PC为指针)并放入指令寄存器(IR),IR保存下个时钟周期所需指令,PC值递增4,指向下个指令地址。

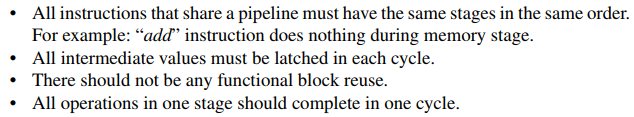

2、指令解码/寄存器获取(ID)

指令格式是固定的,所以读寄存器和解码可以同时进行。这称为固定域译码。

3、执行/有效地址周期(EX)

根据指令类型执行下面4个功能之一:

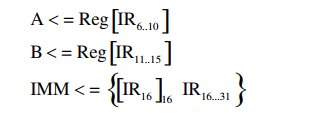

a)访问存储器

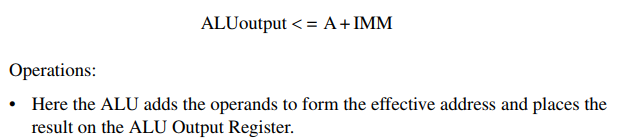

b)寄存器——寄存器ALU指令

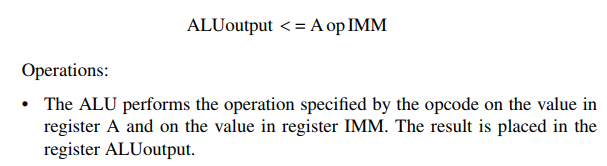

c)寄存器——立即数ALU指令

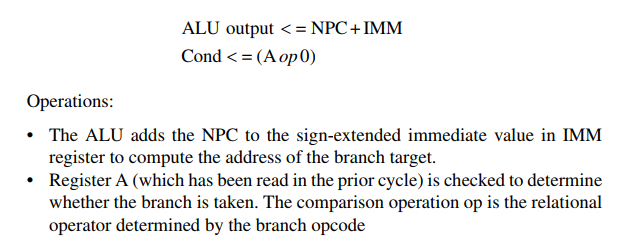

d)分支指令

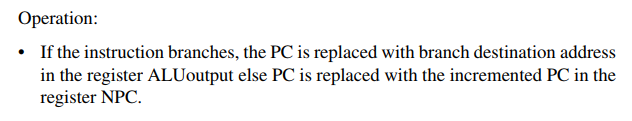

4、访问存储器/分支完成周期(MEM)

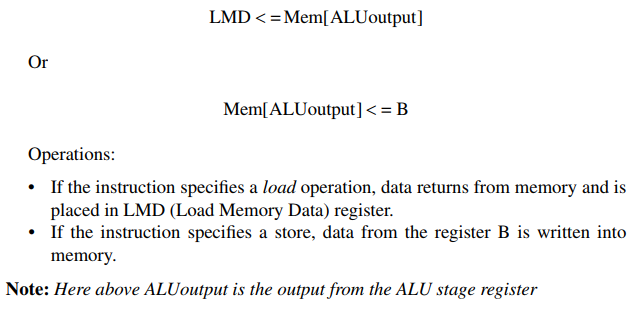

a)访问寄存器

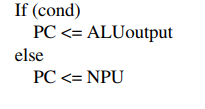

b)分支

5、写回周期(WB)

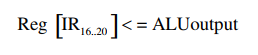

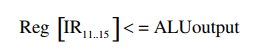

a)寄存器——寄存器ALU指令

b)寄存器——立即数周期

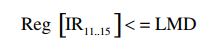

c)取指令

以上操作将结果写回入寄存器堆中,结果可能来自存储器(LMD)或者来自于ALU。

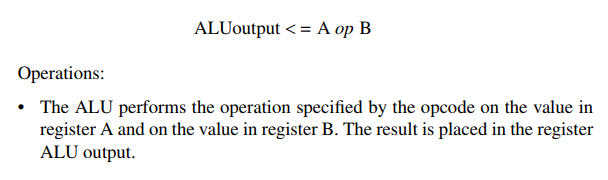

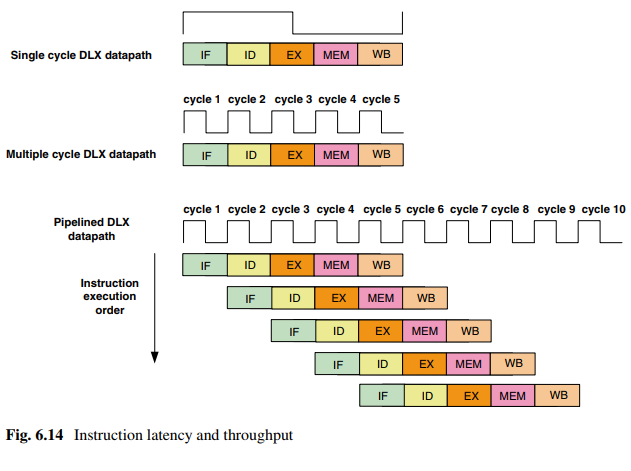

无流水线DLX数据通路上的5个步骤:

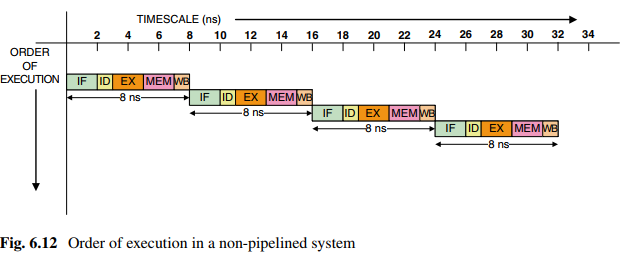

无流水线无法并行执行指令,只有当第一条指令执行完才开始执行第二条指令。

6.7 流水线对吞吐率的影响

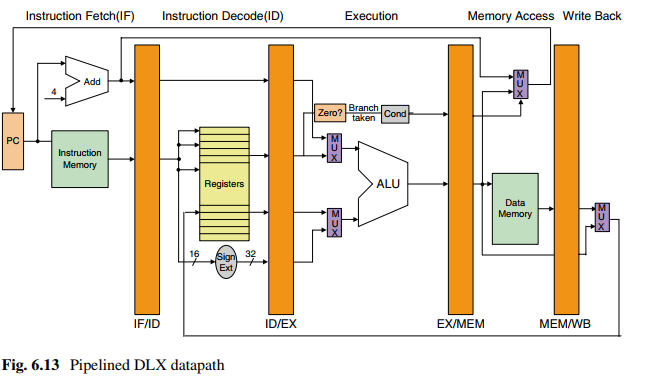

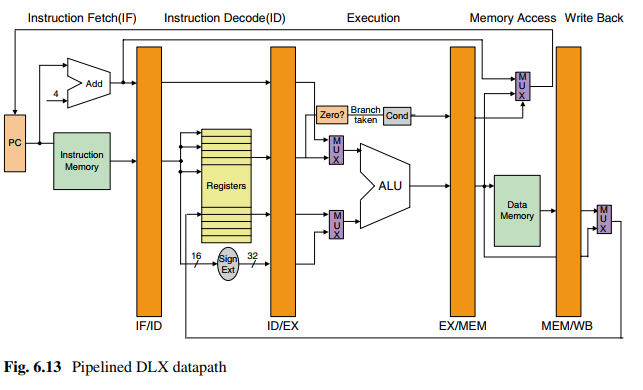

在每个阶段加一级流水线:

如图,不加流水线消耗时间5(5条指令)*5(每条指令消耗周期数)*2(周期)=50ns,加了之后9*2=18ns,性能提升了50/18=2.8倍。

但是使用流水线时会引入额外的开销,如Skew和寄存器延迟,这种开销限制了流水线所能达到的加速值。

6.8 流水线原理