【《硬件架构的艺术》读书笔记】05 低功耗设计(1)

5.1 介绍

能量以热量形式消耗,温度升高芯片失效率也会增加,增加散热片或风扇会增加整体重量和成本,在SoC级别对功耗进行控制就可以减少甚至可能消除掉这些开支,产品也更小更便宜更可靠。本章描述了减少动态功耗和静态功耗的各种技术。

5.2 功耗源

三个主要的功耗源:浪涌、静态功耗、动态功耗。

浪涌电流:器件上电时最大瞬时输入电流。浪涌电流在应用中也称为启动电流。浪涌电流与设备有关,如电机启动电流前几个周期时正常满载电流的数倍。

基于SRAM的FPGA也有很明显的浪涌电流,上电时器件没有配置,需要外部下载数据配置编程资源(查找表、布线资源)。反熔丝FPGA无需上电配置,所以没有浪涌电流。

待机电流:关断主电源或系统进入待机模式下产生的电流。待机电流产生的功耗称为待机功耗。待机功耗也与元件电气特征密切相关。待机功耗也称为静态功耗,静态功耗也包括晶体管漏电流产生的功耗。

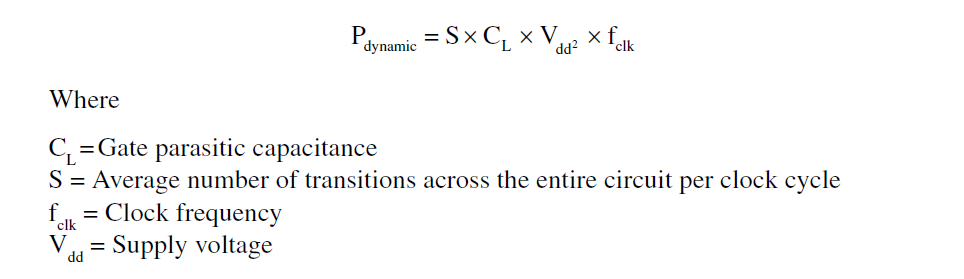

动态功耗(开关功耗)是门电路输出转换时,由逻辑转换所引起的功耗。动态功耗定义公式:

逻辑0->1,电容充电;逻辑1->0,电容放电。

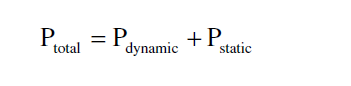

ASIC总功耗:

在典型应用中,动态功耗占到了总功耗的80%

5.3 在各设计抽象层次降低功耗

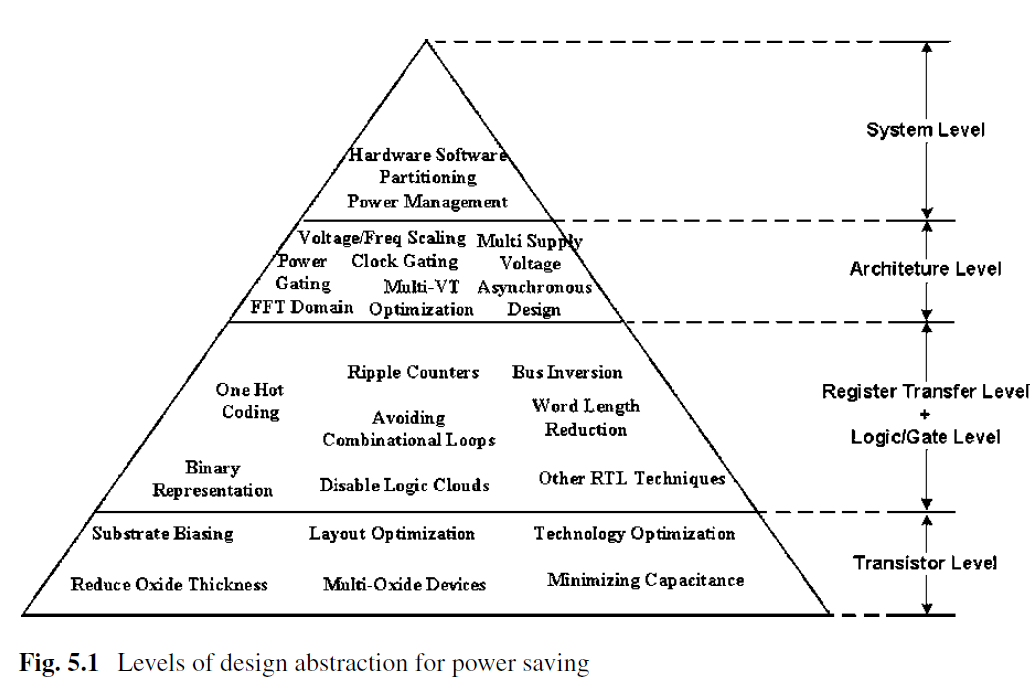

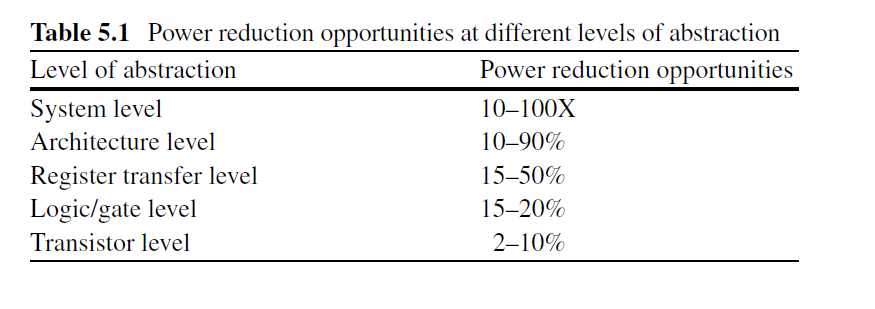

降低功耗应该在所有设计层次上进行:系统层、逻辑层、物理层。层次越高就可能越有效。

在高的抽象层次上进行功耗的优化效果更好,如在系统和体系结构级可以达到最大的降低效果。

为了最大程度降低功耗,各抽象层次在设计时就要把功耗因素考虑在内。

上面的100X打错了是100%

5.4 系统级低功耗技术

5.4.1 片上系统方法

纳米级高端芯片的IO使用比内核更高的电压供电(3V3),占总功耗的50%。如果整个系统包含多个芯片,这些芯片间的连线将产生大量功耗。片上系统方法学主要关注降低功耗,缩减面积以及降低成本的手段。

5.4.2 硬件/软件划分

嵌入式处理器在大规模数字系统中广泛使用,某些功能可以用硬件实现,其余部分可以用软件实现。

通信算法具有高度递归的性质,少量代码可以负责大量的处理任务。这些资源密集型模块用硬件识别和实现,就可以节约大量功耗。

使用硬件综合工具从Verilog或者VHDL描述的模块中提取出物理模型。编译器也可以将用高级语言编写的程序编译成嵌入式处理器所使用的原生指令集。

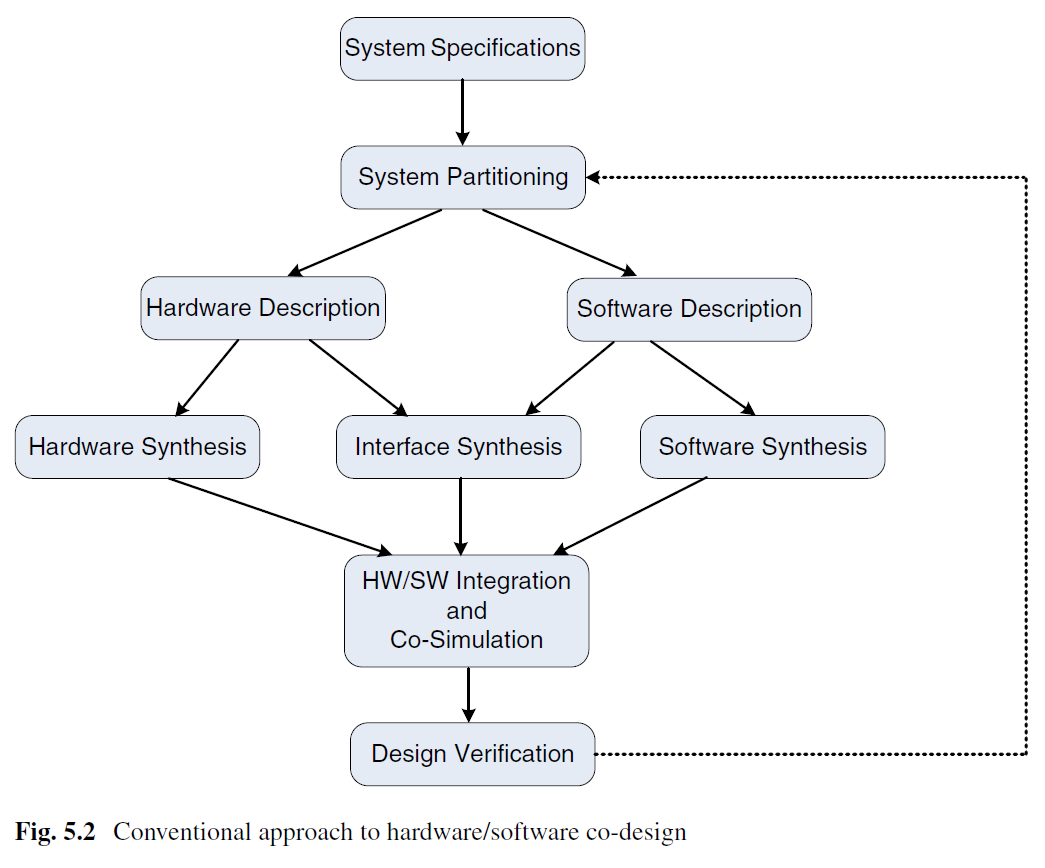

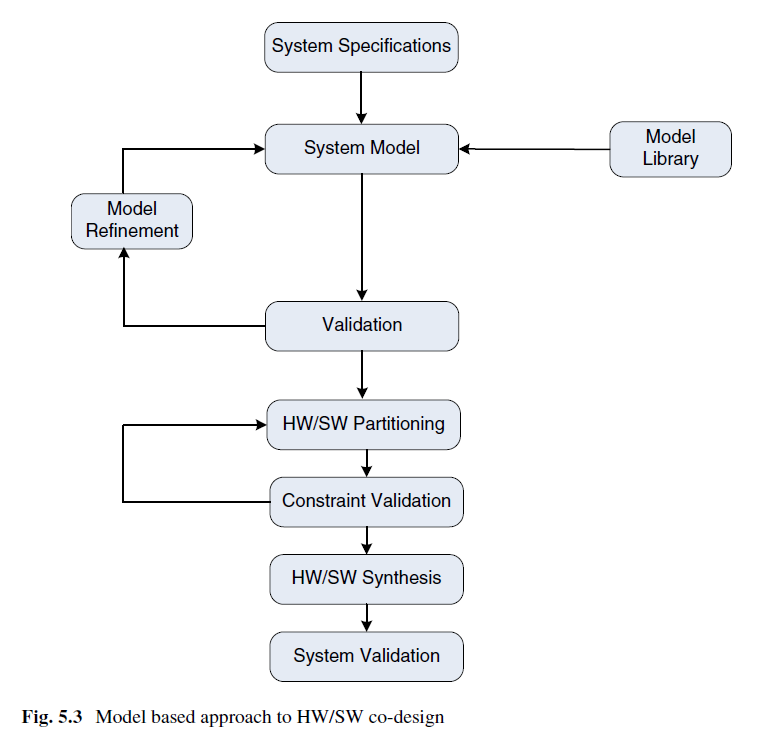

一种比常规方式更有效的HW/SW划分方法是使用基于模型的方式,如下图。

这是一种基于给定规范建立系统模型的想法。模型要么完全自己建立要么使用可复用的已有模型库。随着库的增加,可以大大缩短设计时间。

可以使用SystemC建立模型,该语言可以用于对硬件建模。

5.4.3 低功耗软件

修改应用程序可以节约大量能耗,得到“更绿色”和能效更高的系统。

高级语言便于使用,但是有些结构难以用其实现,使用高频轮询实现这样的结构,这会导致较高的能耗。所以使用高级语言时要避免使用复杂原语。

嵌入式应用使用的C代码可能会使用若干循环。一些应用中,90%的运行时间可能都在执行这些循环。

优化方法:合并循环,使执行的指令数减少。基于硬件体系结构或处理器指令和寄存器的实现。我理解的就是更高效的利用硬件,而不是通过软件程序。

5.4.4 选择处理器

首先要选择合适数据宽度的处理器。如果使用简单的MAC(Multiply Accumulate Unit)能满足运算要求,就没必要用专用的DSP处理器,这样可以显著降低功耗。

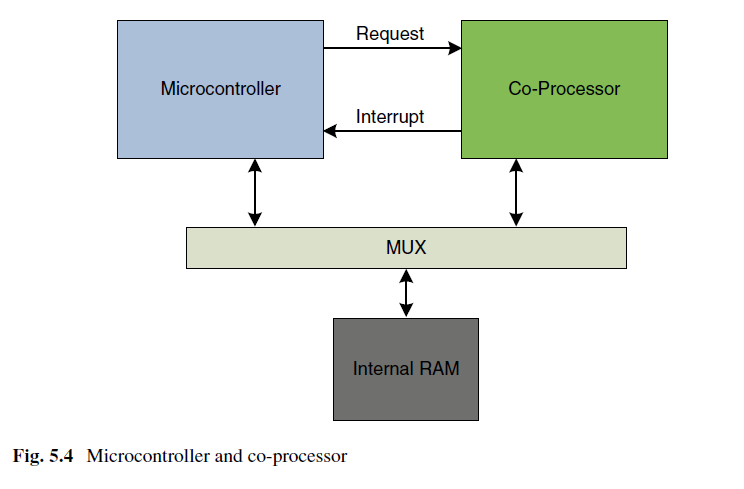

图中是一个节省功耗的系统体系结构。利用微处理器进行控制,同时用协处理器或DSP进行数据处理。最好的系统体系结构用特定的机器(协处理器)来执行这个任务,使任务在最小且能效最高的机器中完成。即特定功能使用特定硬件实现从而实现降低功耗的目的。大多数情况下,微处理器和协处理器不会并行运行。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 震惊!C++程序真的从main开始吗?99%的程序员都答错了

· 别再用vector<bool>了!Google高级工程师:这可能是STL最大的设计失误

· 单元测试从入门到精通

· 【硬核科普】Trae如何「偷看」你的代码?零基础破解AI编程运行原理

· 上周热点回顾(3.3-3.9)