NUMA架构理解

NUMA(Non-Uniform Memory Access,非一致性内存访问)和SMP(Symmetric Multi-Processor,对称多处理器系统)是两种不同的CPU硬件体系架构。

SMP的主要特征是共享,所有的CPU共享使用全部资源,例如内存、总线和I/O,多个CPU对称工作,彼此之间没有主次之分,平等地访问共享的资源,这样势必引入资源的竞争问题,从而导致它的扩展内力非常有限。

NUMA技术将CPU划分成不同的组(Node),每个Node由多个CPU组成,并且有独立的本地内存、I/O等资源。Node之间通过互联模块连接和沟通,因此除了本地内存外,每个CPU仍可以访问远端Node的内存,只不过效率会比访问本地内存差一些,我们用Node之间的距离(Distance,抽象的概念)来定义各个Node之间互访资源的开销。

NUMA架构基本概念

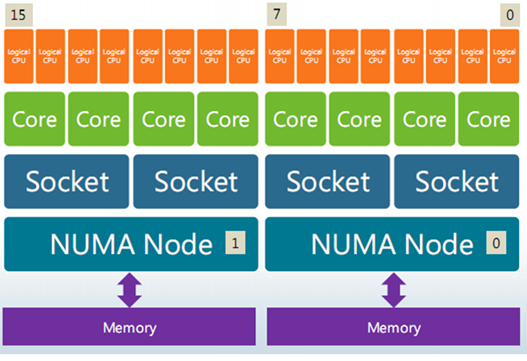

Node->Socket->Core->Processor

随着多核技术的发展,我们将多个CPU封装在一起,这个封装一般被称为Socket(插槽的意思,也有人称之为Packet,不知到哪个更加准确?),而Socket中的每个核心被称为Core。为了进一步提升CPU的处理能力,Intel又引入了HT(Hyper-Threading,超线程)的技术,一个Core打开HT之后,在OS看来就是两个核,当然这个核是逻辑上的概念,所以也被称为Logical Processor,本文简称为Processor。

综上所述,一个NUMA Node可以有一个或者多个Socket,一个多核Socket显然包含多个Core,一个Core如果打开HT则变成两个Logical Processor。Logical processor只是OS内部看到的,实际上两个Processor还是位于同一个Core上,所以频繁的调度仍可能导致资源竞争,影响性能。

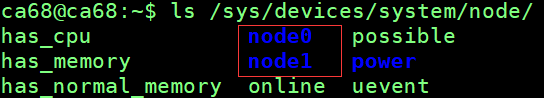

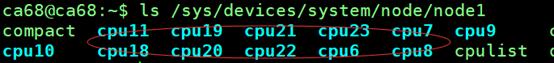

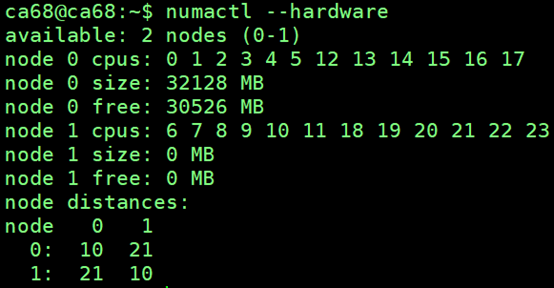

查看机器节点:可以看到机器上有两个node,分别为node0和node1

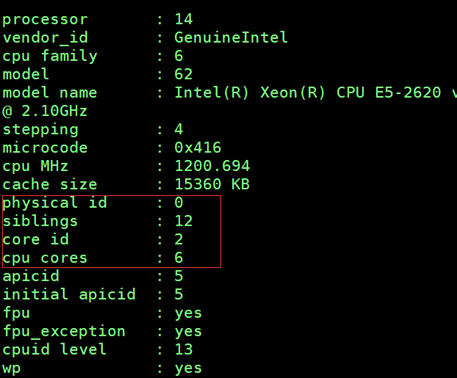

查看socket:

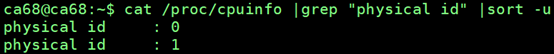

Socket的信息可以通过/proc/cpuinfo查看,里面的physical id标示的就是socket号。

可以看到机器上面有两个socket,编号分别为0和1。我的机器上一个node对应于一个scoket。

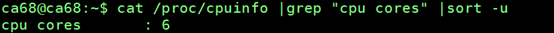

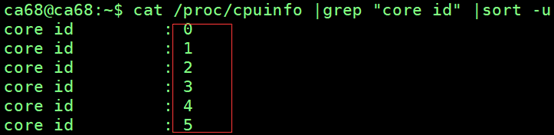

查看core:

可以看到每个socket有6个core,编号是0~5

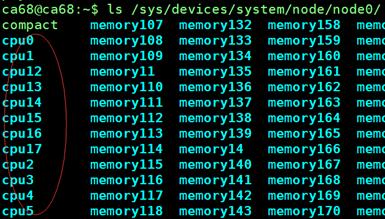

每个socket(每个node)有12CPU:

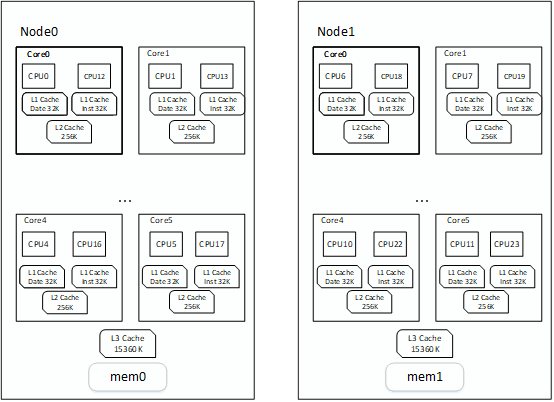

Node0的CPU编号:0~5,12~17 ;Node1的CPU编号:6~11,18~23

上面的信息可知每个Node上面有12个cpu,6个core,则每个core里面有两个cpu,也就是thread的概念。

下面来看下thread的信息,cat /proc/cpuinfo可以看到每个thread,也就是每个逻辑cpu的详细信息。

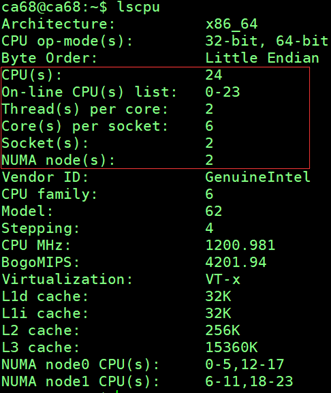

查看CPU的整体信息:

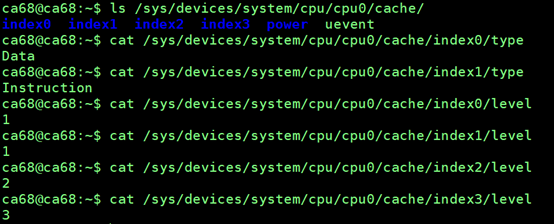

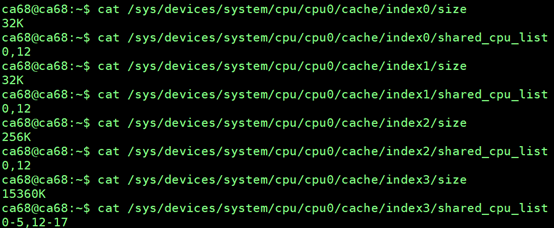

CPU0的cache信息如下图所示,index0对应的是L1 Data Cache,index1对应的是L1 Instruction Cache,index2对应的是L2 Cache,index3对应的是L3 Cache

L1 Data Cache的大小为32k字节,共享此cache的cpu有cpu0和cpu12。

L1 Instruction Cache的大小为32k字节,共享此cache的cpu有cpu0和cpu12。

L2 Cache的大小为256k字节,共享此cache的cpu有cpu0和cpu12。

L3 Cache的大小为15360K字节,共享此cache的cpu有cpu0~cpu5和cpu12~cpu17,即node0上的所有cpu。

遍历所有的cpu信息,可知cpu的拓扑架构如下所示:

访问本地内存的速度要快于访问远端内存的速度。访问速度与node的距离有关系,node间的距离我们称为node distance。

浙公网安备 33010602011771号

浙公网安备 33010602011771号