面向综合优化的Verilog代码风格

用于记录学习数字前后端中总结得到的对verilog代码编写的注意事项

良好的运算顺序

a <= bd + cd + eb;

尽量不要写这种运算表达式,最好经过化简:

a <= b(d + e) + c*d

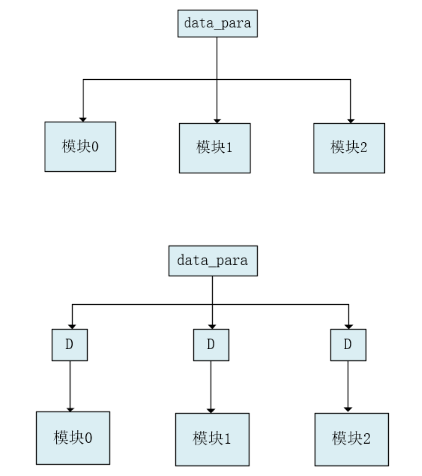

减少寄存器连线

一个寄存器设计很多逻辑时可能会导致负载太大。同一个信号在很多地方使用,布线也会变复杂,比如最常见的是参数信号,在很多模块都会有用到的情况,用寄存器复制的方法。

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

data_para0 <= 4'b0;

data_para1 <= 4'b0;

data_para2 <= 4'b0;

end

else begin

data_para0 <= data_para;

data_para1 <= data_para;

data_para2 <= data_para;

end

end

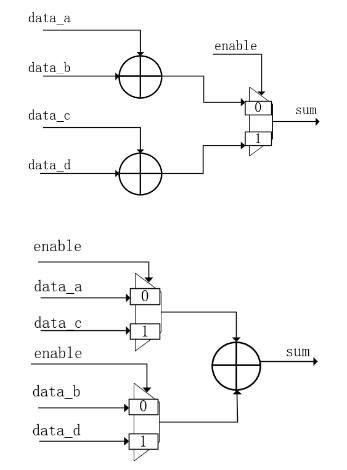

先选后比再加

面积:加法器 > 比较器 > 选择器

乘法器本质上也是全加器。

所以就有先选后比,先选后加,先选后乘。

assign sum[4:0] = enable ? (data_a + data_b) : (data_c + data_d);

//换一种实现方式:

assign add_a[3:0] = enable ? data_a : data_c;

assign add_b[3:0] = enable ? data_b : data_d;

assign sum[4:0] = add_a + add_b;

数据通路与控制通路

数据通路打拍可以不带复位,带着使能信号去打拍,减少信号翻转,减少功耗。保证数据用的时候不是X态,

组合逻辑路径是否需要插入pipeline,插入pipeline的位置需要注意。寄存器能少用就少用。

尽量不要用除法,首先除法器面积更大,除法也会有余数,余数是否需要保留就很麻烦。除以常数可以做成乘以定点常数的方法。

乘以常数用移位加,也可直接用*号。例如a * 2‘d3,工具会帮你优化成 a << 2’d1 + a。甚至可能优化得更好。(杠:不要过度依赖工具)。关于用移位加还是*号的问题,博主做过综合后的面积对比,相对来说,工具还是优化那么一点点。直接用 * 号吧。

尽量不要用减法,减法要考虑到减翻的问题,尽量用加法。

浙公网安备 33010602011771号

浙公网安备 33010602011771号