小梅哥 FPGA

vivado中整体排版 按Tab

1.500ms的灯闪烁 (周期20ns,怎么衡量500ms,则需要计数器)若计数器计数4次,范围应该是0-3

2.跑马灯,设计让8个LED灯以每个0.5s的速率循环闪烁 (计数器自动计满的时候会溢出自动归零)

方法一:循环移位 <<1 左移移位 方法二:优化一,用循环移位,不用设置跳转 方法三:调用3-8译码器

3.让8个led灯以不同的频率闪烁,复杂的方法是分别写八个模块,然后例化即可,

简单的方法是写一个底层模块用参数定义,再写一个模块用于例化底层,在例化后修改参数即可

如:defparameter + 例化名 + MCNT(参数) = (可修改)

defparameter 不能写在tb中,方法二:在文件中调用时led led0 def... 可以改写为 led #( .MCNT(可变得数字)) led0(...);

头文件中parameter定义参数后,在例化时要例化参数。 若#(parameter = )不用例化

4.从计数器到可控线性序列机

1)让LED灯亮0.25s灭0.75s循环,直接计数到1s,

3)让LED灯以指定亮灭模式亮灭,每个周期0.25s 一个循环8个周期

4)让LED灯以指定模式指定周期亮灭,一个循环8个周期 和3)区别是周期可变。

5)多LED同4) 区别在于在一个时刻有多个LED和多个输入对应,

应用于spi iic 先给定一个时钟频率,在某个时刻,四个信号的值如何变化

半小时想不出来就看答案~!!!

状态序列机搞定。。

时序逻辑中用非阻塞赋值!!!

阻塞赋值和非阻塞赋值仅限于在时序逻辑中存在。

时序逻辑中用的都是D触发器,

输入a,b结果并非d而是D触发器的输入端口 d<=a+b, out<=d+c

若用阻塞赋值,就要考虑代码先后执行顺序,综合出来的代码不一样,

非阻塞赋值原理:a+b的值下一个时钟到来时给d 而d+c的值下一个时钟到来时给out,但第一个d的结果并不是第二个d的输入,而第二个的输入用的是前一个时钟周期的d

D触发器细节原理,在时钟上升沿采集前面的数据(因为会有不可避免的延迟)

1.发模块搞定,但连续发多字节有问题 (解决!!!!!)

2.uart收模块待定:(解决!!!!!) 问题出在没有加bit_flag 例:导致在counter1为4时赋值两次,加了bit_flag,就赋值一次结果正确

1)下降沿判断模块,需要用两个触发器

2)取样时直接赋值即可

3)reg [2:0] r_data[7:0] 二维数组(二位寄存器) 前面定义位宽,后面个数

若要将二位寄存器归零需要一个一个来,reg[0]<=0;reg[1]<=0;....

若default什么都不做就default: ;

任务:如果定义了任务,但是在整个过程中都没有调用它,那么这个任务是不会执行的。

调用某个任务时可能需要它处理某些数据并返回操作结果,所以任务应当有接收数据的输入端和返回数据的输出端。另外,任务可以彼此调用,而且任务内还可以调用函数。

- 1) 函数只能与主模块共用同一个仿真时间单位,而任务可以定义自己的仿真时间单位。

- 2) 函数不能启动任务,而任务能启动其它任务和函数。

- 3) 函数至少要有一个输入变量,而任务可以没有或有多个任何类型的变量。

- 4) 函数返回一个值,而任务则不返回值。

task task_id;

[declaration]

procedural_statement

endtask

注意:

(1)在第一行“task”语句中不能列出端口名称;? ahb_slave_if可以

(2)任务的输入、输出端口和双向端口数量不受限制,甚至可以没有输入、输出以及

双向端口。

(3)在任务定义的描述语句中,可以使用出现不可综合操作符合语句(使用最为频繁

的就是延迟控制语句) ,但这样会造成该任务不可综合。

(4)在任务中可以调用其他的任务或函数,也可以调用自身。

(5)在任务定义结构内不能出现 initial和 always过程块。

(6)在任务定义中可以出现“disable 中止语句” ,将中断正在执行的任务,但其是不

可综合的。当任务被中断后,程序流程将返回到调用任务的地方继续向下执行。

在调用任务时,需要注意以下几点:

(1)任务调用语句只能出现在过程块内;

(2)任务调用语句和一条普通的行为描述语句的处理方法一致;

(3)当被调用输入、输出或双向端口时,任务调用语句必须包含端口名列表,且信号

端口顺序和类型必须和任务定义结构中的顺序和类型一致。需要说明的是,任务的输出端口

必须和寄存器类型的数据变量对应。

(4)可综合任务只能实现组合逻辑,也就是说调用可综合任务的时间为“0” 。而在面

向仿真的任务中可以带有时序控制,如时延,因此面向仿真的任务的调用时间不为“0” 。

task+名字

input[7:0]tx_data;

begin

uart_rx=1;....

end

endtask

3.按键消抖不会超过20ms(按下时会从高电平到低电平)

需要将抖动的波形过滤掉或者说不能让抖动的波形影响最终的结果。

按下过后,如果没有达到20ms就出现高电平,就认为低电平持续持续20ms,才认为按键稳定下来

4.自己学一下random随机函数

5.+:[起始地址和位宽] -:的用法[结束地址和位宽]

data[0 +: 8] <--等价于--> data[7:0]

data[15 +: 2] <--等价于--> data[16:15]

data[7 -: 8] <--等价于--> data[7:0]

data[15 -: 2] <--等价于--> data[15:14]

reg[1:0]r_key; 时钟到来时将key给r_key,reg[1]先进

新问题:亚稳态 上升沿或下降沿时可能会存在亚稳态导致检测不到(数据至少打两拍)

数码管学习:

1.共阴极 高电平亮 2.共阳极 低电平亮

数码管动态扫描是切换太快导致的,动态扫描节约了管脚

三八译码器切换数码管位,20ms每个都扫到,即2.5ms换一次(人眼看到) 假设1ms换一次,而FPGA50M时钟,所以先分频

1.分频写错方法了,搞成计数了(搞混了) 50M分成1K,500um翻转一次。

2.查找表用组合逻辑 查找表LUT

3.时序有问题的时候,即不在同一时间段考虑用组合逻辑

FPGA设计中,尽量使用使能时钟不要使用门控时钟,时序电路优于组合电路

原理:D触发器的输出作为时钟会降低时钟质量,默认不作为高速时钟,同时内部时钟到另一个触发器的驱动时钟会有很久(有可能为ns级别)的延迟,而且会导致触发器不同步,若高质量时钟,每个触发器都是同步

1.时钟延迟不确定比较大,

2.使得时钟的波形变差,

3.驱动能力(工艺上总clk驱动能力强,触发器输出作为时钟驱动能力弱)

一,理解认识FPGA中的存储器

1)数据较多,数据值已知,整个过程都是已知的

只需要一个存储器将数据读存起来,到时候只读即可 即ROM

2)

数据量相对较大

数据要求被更改

数据要能重复使用

可读可写,RAM(random access memory) BRAM and DRAM,BRAM一定有时钟,存储较大空间的数据,DRAM(LUT)通过组合逻辑实现,无时钟,不过可以加寄存器从而加时钟存储较小空间的数据

应用,DDS信号发生器(可调波形)

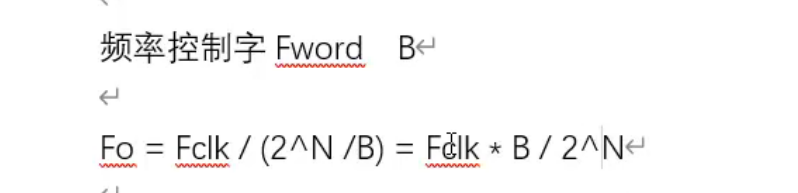

原理:

B为取样点间隔即频率控制字,N为相位累加器的位数(N取的越大 ,精度越高,步进越短一般取24-32),定义正弦信号在相位上的精度。

相位控制字:给rom的地址加偏移值即可

结构:

3)

数据速率不匹配,消耗速率慢于生产速率,总的数据量有限,数据的生产消耗不一样

,FIFO

高速数据采集系统(ADS)

4.数据消耗速率快与数据生产速率

通过以太网或USB传输数据的应用

Vivado IP核:ROM中DMG生成的ROM/RAM core 占用的资源师LUT,现成的FPGA中BROM生成占用的资源师Block Memory(嵌入式的硬件RAM)

①若用32或128字节ROM,用LUT即可②若用块RAM

时钟管理单元应用

想得到125MHZ频率,开发板只有一个50MHZ(倍频),Verilog只能实现分频:使能时钟!可以使用FPGA内部专用电路锁相环实现

PLL是非常有用的同步技术,将电路内部的时钟与外部某一时钟的相位同步

时钟管理器功能:通过GUI的界面形式,帮助用户创建自己的时钟网络

50MHZ到125MHZ 找最小公倍数,先5倍频后2分频,最后得到想要的时钟

MMCM数字锁相环 PLL时钟质量高 locked单元 为锁定信号,标志信号,产生后,输出的时钟信号要求就是满足要求的(相当于复位信号,经常用作整个系统的复位信号)

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· TypeScript + Deepseek 打造卜卦网站:技术与玄学的结合

· 阿里巴巴 QwQ-32B真的超越了 DeepSeek R-1吗?

· 如何调用 DeepSeek 的自然语言处理 API 接口并集成到在线客服系统

· 【译】Visual Studio 中新的强大生产力特性

· 2025年我用 Compose 写了一个 Todo App