复微杯

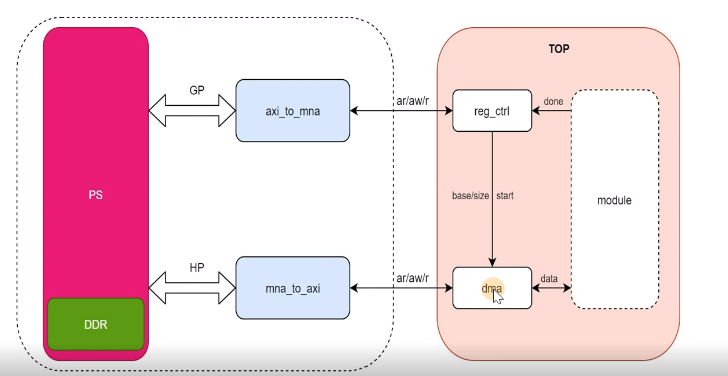

对神经网络进行硬件加速愈发成为一个必要环节” 这一现实需求,要求制定一套完整的语音关键词识别算法方案,采用Verilog语言设计硬件加速器的核心数字电路模块,并将这个软硬件系统的功能在PSOC芯片上实现

对于复微杯,还有一个重点是数字方向要求大家采用UVM的验证平台来验证设计的IP或系统。因此对于UVM大家需要分配好任务,再去搭建UVM平台进行验证测试,我们团队,当时是设计优化完最后的电路,然后利用最后一个月的时间主攻UVM验证平台的搭建,这一部分得到的队友的大力帮助;

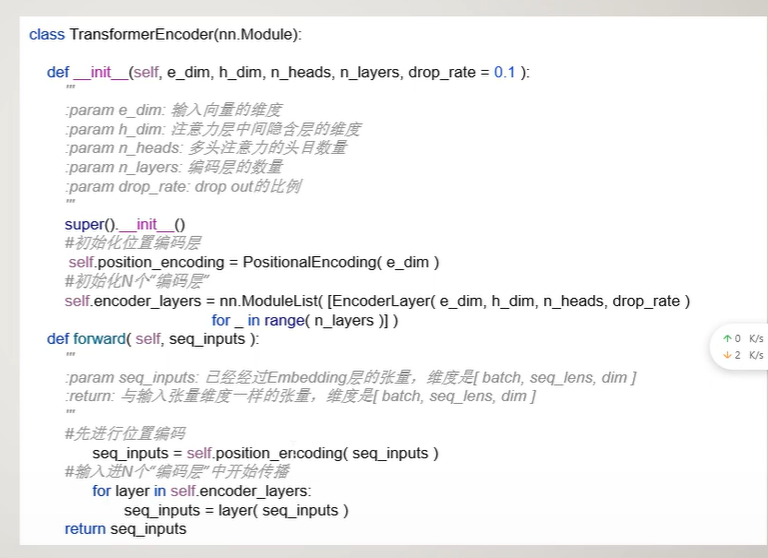

需要完成软硬件划分问题, 只需要改PL累加模块即可,用PS和PL共同完成Encoder结构功能

本次接口均采用握手机制,master 和 slave

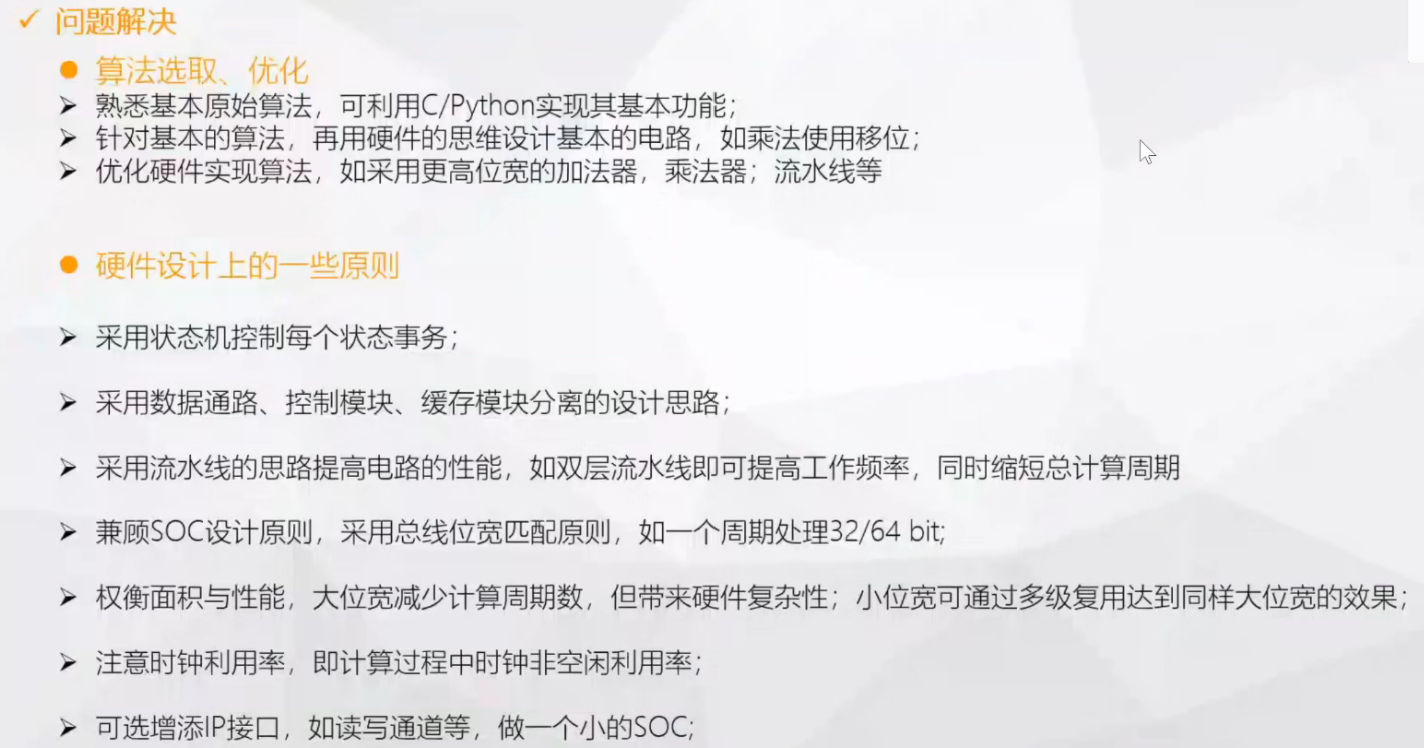

常用多种加法器,乘法器以及优缺点

流水线技术

功耗看pt

ram

赛灵思zink7045 看规模设计