2020-2021-1学期 2024“神舟317号”小组《网络空间安全专业导论》第二周小组学习讨论总结

2020-2021-1学期 2024“神舟317号”小组《网络空间安全专业导论》第二周小组学习讨论总结

小组名称:神舟317号

小组成员:20202423陈驭骐、20202405李昕亮、20202414黄若宇、20202427张启辰

主要议题:加法器的逻辑框图的基本原理

在学习第四章《门和电路》的过程中,我们认真学习了六种“门”的相关知识,梳理了组合电路和时序电路的内容,也了解了门的构造,但是对于4.4.2“加法器”这一知识点仍然抱有较大疑惑,为了解决疑惑以便于更加深入的学习思考,我们“神舟317”小组进行了细致的探讨,最后得到了问题的结论。

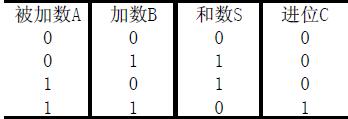

首先研究一下半加器的真值表:

所以看出我们不仅要计算出“和”,还要计算出“进位”,所以我们的电路需要两条输出线。

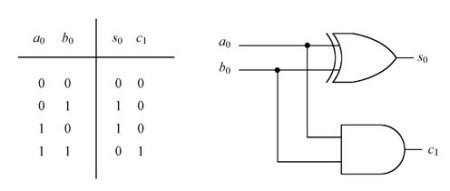

那么不同的输出结果分别对应什么门呢?

经过讨论真值表中的数据,我们得出:

和对应的是 异或门,而进位对应的是 与门

所以到这里我们就已经弄清了“半加器”的逻辑框图啦!

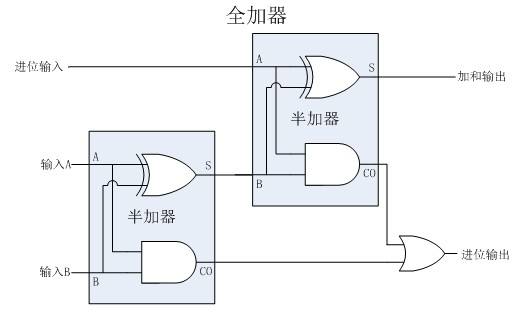

探索永不止步,乘着成功的喜悦,我们紧接着就开始了对全加器的研究。全加器显然要复杂很多,因为半加器不会把进位考虑到计算之内,所以半加器只能计算两个数位的和,而不能计算两个多位二进制的和,为了解决这个问题,才有了全加器。可以用两个半加器构造一个全加器,也就是说,全加器自然会比半加器“高级”一些啦。

我们对照着真值表,才弄明白全加器逻辑框图的真实原理。

举个例子,当输入的A=1,B=1,进位=1时,那么AB通过异或门会变为0,然后通过与门变为1,0与进位1通过与门变为1,二者通过或门就会使进位输出为1,而进位1与0通过异或门,又能使和为1,从而达到了我们的目的;

再举个例子,当输入的A=1,B=1,进位为0时,那么AB通过异或门变为0与进位0通过异或门再一次令和为0,而AB通过与门变成1后与0一起通过或门,从而就能使进位输出为1,与真值表中所显示的恰好一致!

这样下来,我们便彻底弄懂了关于加法器的逻辑框图的相关知识,也对本章的内容有了更加深入的了解!

本次小组讨论的内容就到此结束,但是探索的脚步不会结束。我们针对讨论过程中的问题给出了相应的答案,也希望这种探索精神能够一直支撑着我们学好这门科学。

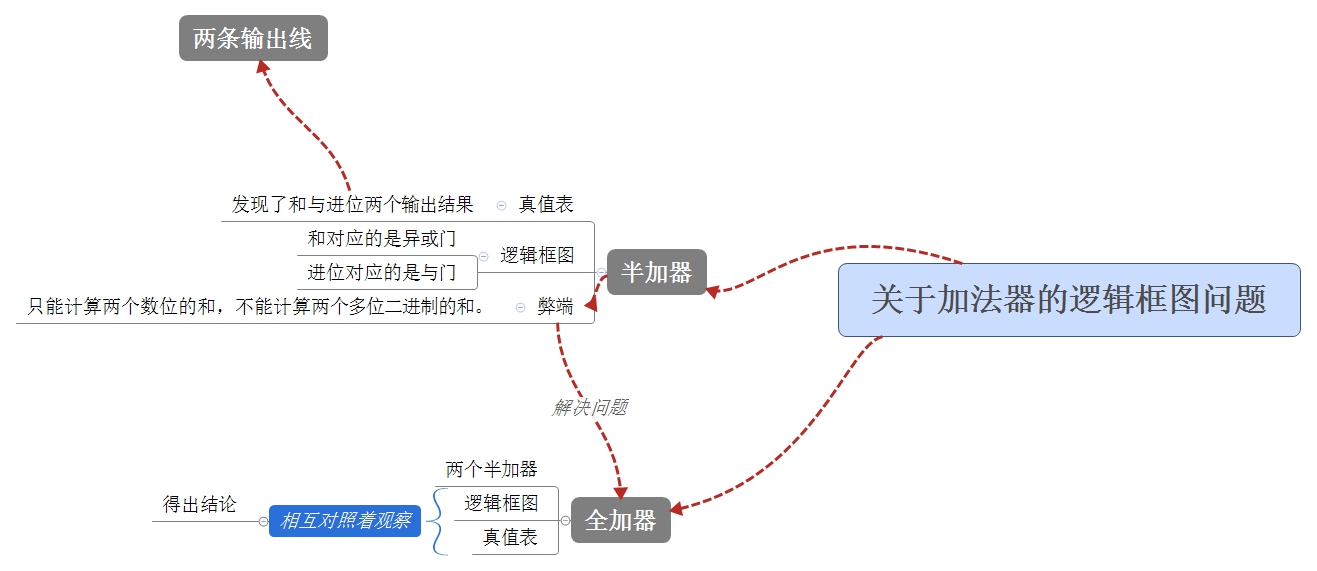

最后,用脑图来梳理一下讨论过程中的知识点吧~

浙公网安备 33010602011771号

浙公网安备 33010602011771号