Clock Switch,芯片时钟切换的毛刺是什么,如何消除

背景

芯片运行过程中需要时钟切换时,要考虑到是否会产生glitch,小小的glitch有可能导致电路运行的错误。所以时钟切换时需要特别的处理。

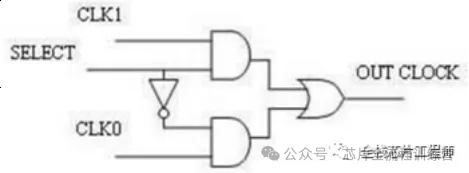

直接使用MUX进行时钟切换或者采用如下电路结构进行时钟切换:

assign outclock = (clk1 & select) | (~select & clk0);

或

assign outclock = select? clk1: clk0; (直接采用MUX实现)

但以上两种做法都会产生时钟切换毛刺的,芯片系统很容易进入亚稳态的情况。如下图,由于是纯组合逻辑,select信号变化可能发生在任何时刻,很容易发生时钟切换毛刺,我们需要使用无毛刺的时钟切换电路,即Glitch-free clock switching circuit。

为了解决时钟切换的毛刺问题,对于时钟源分为同步和异步的情况,分为如下两种解决方案:

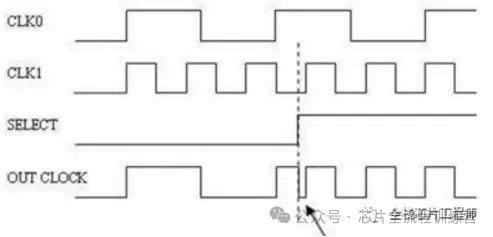

CLK0与CLK1为同步时钟源,即CLK0与CLK1成整数倍关系

插入下降沿触发的D触发器,当前已打开的时钟路径上的时钟会在其下降沿之后先关闭,然后待打开时钟路径上的时钟在其下降沿之后即打开。如下所示:从下图第二个箭头开始,实际发生时钟切换,两个触发器都是下降沿触发。

当select信号为0时:

此时选择的时钟为CLK0,DFF1 Q端输出始终为0,QN端输出1并反馈至DFF0。当CLK0的下降沿采样后,DFF0的Q端输出1,QN端输出0并反馈至DFF1,从而不会在与门处产生毛刺。此时输出的OUT_CLK为CLK0。

当select信号切换为1时:

只有当CLK0的下降沿到来后,DFF0的Q端输出才会是0,其QN端输出才会是1,随后DFF1的D端的输入才会是1,然后还要等,当CLK1的下降沿到来后,DFF1的Q端输出变为1,QN输出变为0,但由于此时CLK1为低电平,因此OUT_CLK仍然为0。然后还要等,当CLK1出现高电平后,OUT_CLK才会切换到高电平。

注意时序约束关系:

select控制信号到DFF0、DFF1的D端;

DFF0的QN端输出到DFF1的D端;

DFF1的QN端输出到DFF0的D端;

这四条路径中,任何一路径上的信号与目标时钟域的采样时钟同时发生变化,则该寄存器的输出可能变为亚稳态。因此上述两个下降沿触发器结构要求两个时钟是同步时钟,且频率成倍数关系,这样就能始终满足时序约束关系,不会出现毛刺和亚稳态。

请问CLK0与CLK1为异步时钟时,电路如何设计?

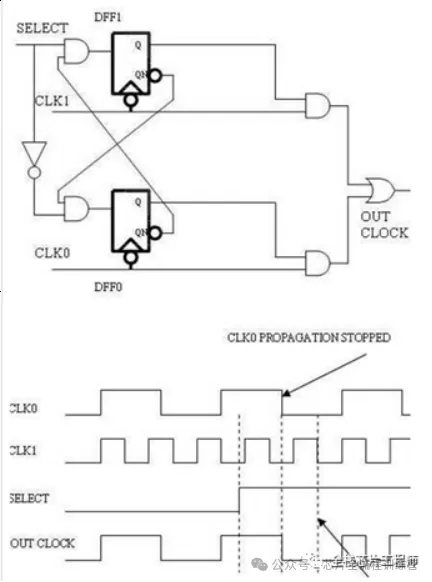

CLK0与CLK1为无关时钟源,即异步时钟源

在第一种方法的基础上,在选择路径上再插入一个上升沿触发D触发器,这是对异步信号进行同步处理,这样即使是两个异步的时钟源进行切换,也可以避免亚稳态的产生。从下图中第二个箭头开始,实际发生时钟切换。

select为0时,OUT_CLOCK选择CLK0。

select切换为1时,CLK0的上升沿打一拍,下降沿打一拍,才能关闭CLK0时钟,此时OUT_CLOCK输出为0,然后还要等,等CLK1的上升沿打一拍,下降沿打一拍,才能打开CLK1,此时OUT_CLOC输出为0,等到CLK1上升沿到了OUT_CLOCK才有上升沿。

总结,通过在负沿触发器前添加了1个正沿触发器,使得:

select控制信号到DFF0、DFF1的D端;

DFF0的QN端输出到DFF1的D端;

DFF1的QN端输出到DFF0的D端;

上面四条路径的输入信号和负沿触发器的capture时钟沿之间构成两级触发器打拍,防止跨时钟域的亚稳态传递和毛刺信号出现。

浙公网安备 33010602011771号

浙公网安备 33010602011771号