what is Generic Timer/Counter

what is generic timer

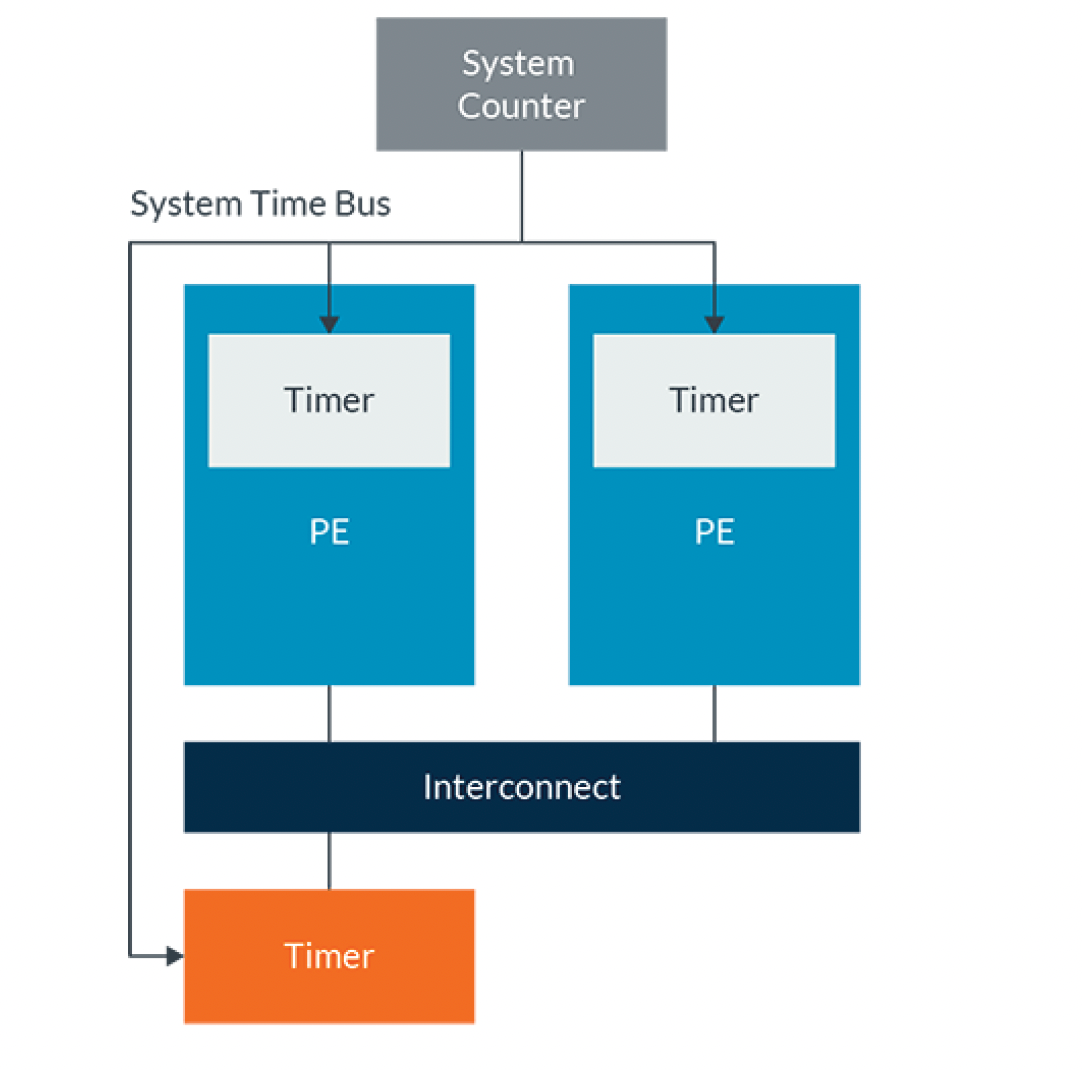

Generic Timer为ARM cores提供了一个标准的timer框架,Generic Timer包含一个System Counter和each core的一组timers,还有system level memory-mapped的timers。

- system counter作用是为整个SoC提供统一的时间戳

- generic timer是比较器,与system counter进行比较。作用是提供定时中断服务。

System Counter

System Counter位于always-on区域,它的输入频率是固定的。System Counter的value会广播给系统中所有的core,提供给它们同样的视角关于passing of time。System Counter只测量时间的流逝。它不报告时间或日期。通常,一个SoC还会包含一个用于时间和日期的实时时钟(RTC)。

通常,System Counter在系统启动时需要一些初始化。为了节省功耗,System Counter会变化更新counter的频率,比如System Counter在第10个tick到来时加上10个count,这种场景一般需要所有core都进入low power模式。

- Width

From Armv8.0 to Armv8.5 inclusive, at least 56 bits wide.

From Armv8.6, must be 64 bits wide. - Frequency

From Armv8.0 to Armv8.5,1-50MHz

From Armv8.6, increments at a fixed frequency of 1GHz. - Roll-over

翻转时间不少于40年 - Accuracy

建议24小时,不超过10秒误差 - Start-up

Starts operating from zero.

PE's Timer

每个core还会有多个timers,这些timers只是一个比较器,System Counter提供的广播value进行比较。软件可以配置计时器来在将来的设定值中生成中断或事件。

system level memory-mapped Timer

这些timers位于SoC内部,通过memory-mapped registers访问,它们的中断会接到GIC SPI中断。

timer的两种配置方式

有两种方式可以配置定时器,一种是使用比较器(CVAL)寄存器,另一种是利用定时器(TVAL)寄存器。

比较器寄存器CVAL是一个64位寄存器。软件会向该寄存器写入一个值,当计数达到或超过该值时,计时器会触发,如您所见:

Timer Condition Met: CVAL <= System Count

定时器寄存器TVAL是一个32位寄存器。当软件写入TVAL时,处理器内部读取当前系统计数,添加写入的值,然后填充CVAL, 你可以在软件中看到 CVAL 的这种填充。如果读取当前系统计数,将1000写入 TVAL,然后读取 CVAL,您将看到 CVAL 大约是1000 + 系统计数。计数是近似的,因为时间会在指令序列中移动。

读TVAL将显示其递减至0,而系统计数递增。TVAL报告一个有符号的值,并将在计时器触发后继续递减,这允许软件确定计时器触发的时间。TVAL和CVAL为软件提供了两种不同的定时器使用模型。如果软件在时钟的X个节拍中需要计时器事件,软件可以将X写入TVAL。或者,如果软件希望在系统计数达到Y时发生事件,则软件可以将Y写入CVAL。

请记住,TVAL和CVAL是对同一计时器进行编程的不同方式。他们不是两个不同的定时器。

CVAL = TVAL + System Counter

Timer Condition Met: CVAL <= System Count

注意

系统计数器实时测量。这意味着它不会受到电源管理技术的影响,如动态电压和频率缩放(DVFS)或将核心置于较低功率状态。计数必须继续以其固定频率递增。在实践中,这要求系统计数器处于常开电源域中。

为了节省电力,系统计数器可以改变其更新计数的速率。例如,系统计数器可以在时钟的每10个刻度将计数更新10。当连接的核心都处于低功率状态时,这可能很有用。系统计数仍然需要反映时间的推移,但可以通过广播更少的计数器更新来节省功率。

Register

System Counter

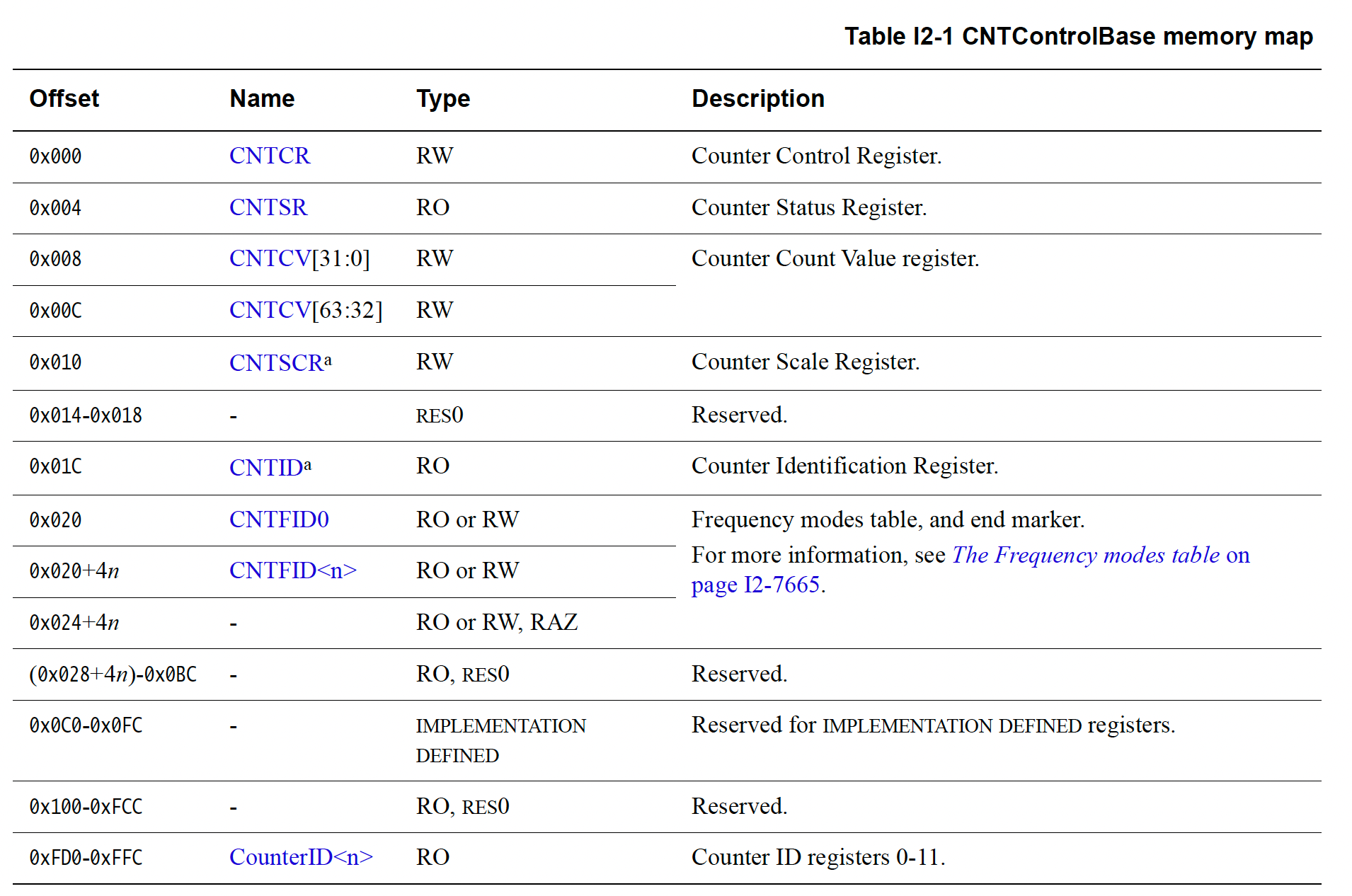

This module controls the system counter. It has two frames:

• A control frame, CNTControlBase.

• A status frame, CNTReadBase.

CNTControlBase

CNTControlBase is accessible only by Secure accesses.

- An enable bit for the system counter.

- An enable bit for Halt-on-debug.

CNTReadBase

只读状态寄存器。The CNTReadBase frame includes a read-only copy of the system counter value, CNTCV, as two contiguous 32-bit RO registers.

Timer

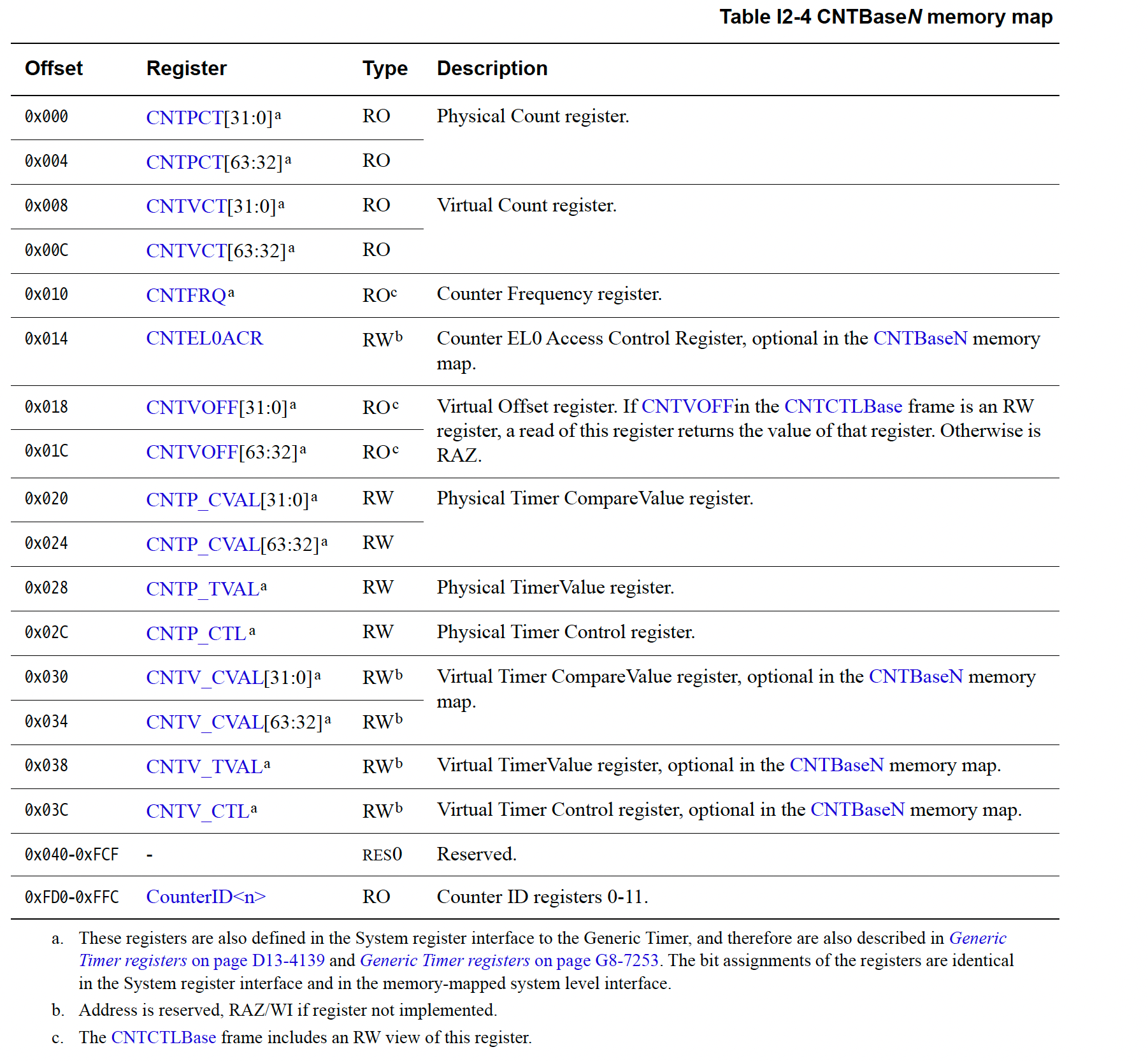

CNTCTLBase

- An identification register for the features of the memory-mapped counter and timer implementation.

- Access controls for each CNTBaseN frame.

- A virtual offset register for frames that implement a virtual timer.

CNTBASEn

Each CNTBaseN timer frame:

- Provides its own set of timers and associated interrupts.

- Is implemented in its own memory page or memory protection region.

- Is implemented at a base address, identified as CNTBaseN, that is aligned to the size of the translation granule or memory protection region.

浙公网安备 33010602011771号

浙公网安备 33010602011771号