SPI、QSPI协议总结

SPI简介

SPI 全称是 Serial Perripheral Interface,也就是串行外围设备接口。 SPI 是 Motorola 公司与1980s推出的一种同步串行接口技术,是一种高速、全双工的同步通信总线。 SPI 时钟频率相比 I2C 要高很多,最高可以工作在上百 MHz。 SPI 以主从方式工作,通常是有一个主设备和一个或多个从设备,一般 SPI 需要4根线,但是也可以使用3根线(单向传输)。

SPI接口

SPI总线有4个逻辑信号:

- SCLK: Serial Clock (output from master)

- MOSI: Master Out Slave In (data output from master)

- MISO: Master In Slave Out (data output from slave)

- CS /SS: Chip/Slave Select (often

active low, output from master to indicate that data is being sent)

有一些非标准的SPI pin名字

Serial Clock:

- SCK .

Master Output → Slave Input (MOSI):

- SIMO, MTSR - correspond to MOSI on both master and slave devices, connects to each other

- SDI, DI, DIN, SI - on slave devices; connects to MOSI on master, or to below connections

- SDO, DO, DOUT, SO - on master devices; connects to MOSI on slave, or to above connections

Master Input ← Slave Output (MISO):

- SOMI, MRST - correspond to MISO on both master and slave devices, connects to each other

- SDO, DO, DOUT, SO - on slave devices; connects to MISO on master, or to below connections

- SDI, DI, DIN, SI - on master devices; connects to MISO on slave, or to above connections

Slave Select:

- SS, SS, SSEL, nSS, /SS, SS# (slave select)

- CS, CS (chip select)

- CSN (chip select/enable)

- CE (chip enable)

操作

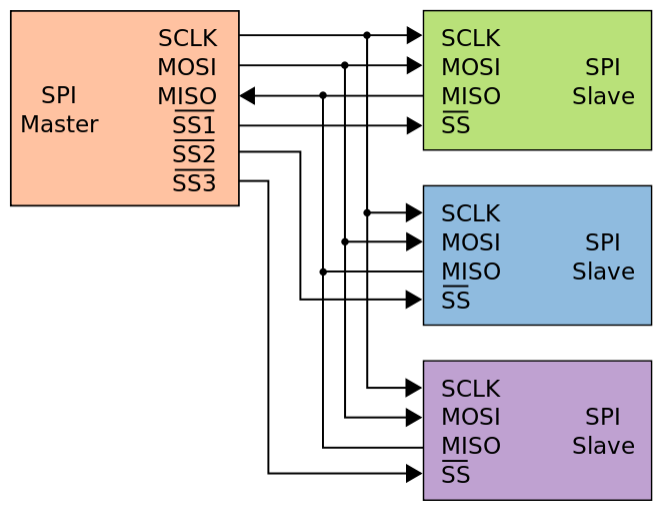

SPI的连接方式,只有一个master,有一个或多个slave。当有多个slave时,需要有多个独立的SS信号从master连接到slave。SS信号通常是低有效,但也有的实现需要有一个下降沿作为触发条件。

数据传输

开始通信前,master配置clock,使用从设备支持的频率,通常高达几MHz,然后master选择SS信号。在SPI始终周期内,可以全双工数据传输。

主从设备通常有固定位宽的移位寄存器,例如8位。数据通常先从MSB的位移出。在时钟边缘,主和从都移出一个比特,并在传输线上输出到对端。如果需要交换更多的数据,则重新加载移位寄存器并重复这个过程。

四种工作模式

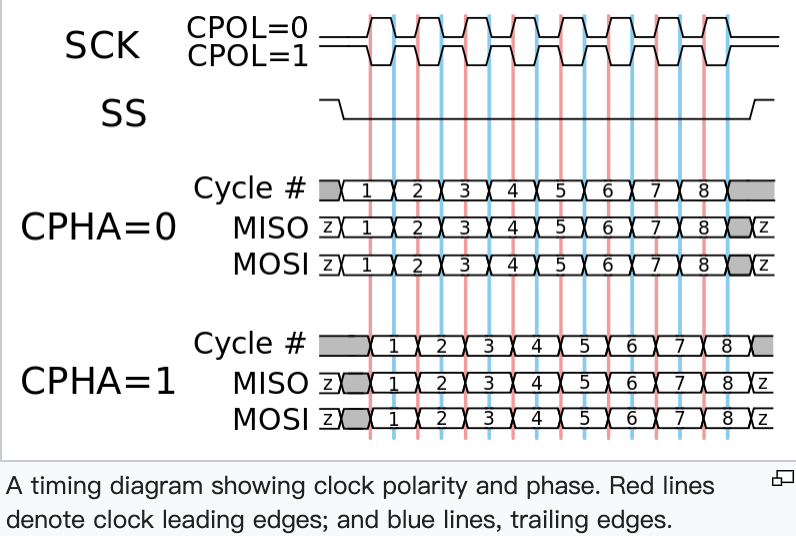

SPI 有四种工作模式,通过时钟极性(CPOL)和相位(CPHA)的搭配来得到四种工作模式:

①、 CPOL=0,串行时钟空闲状态为低电平,上升沿有效,

②、 CPOL=1,串行时钟空闲状态为高电平,下降沿有效,此时可以通过配置时钟相位(CPHA)来选择具体的传输协议。

③、 CPHA=0,串行时钟的第一个跳变沿(上升沿或下降沿)采集数据。

④、 CPHA=1,串行时钟的第二个跳变沿(上升沿或下降沿)采集数据。

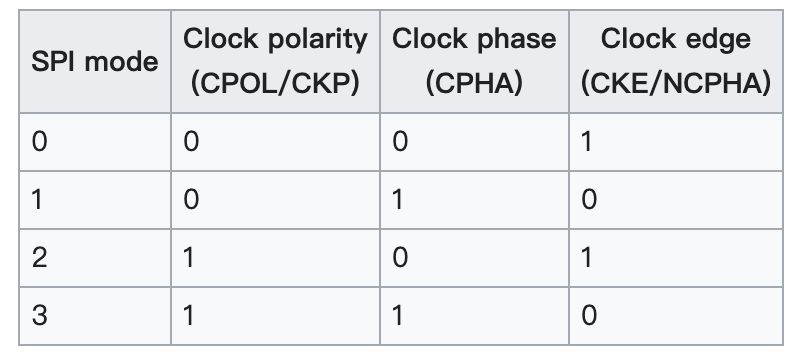

Mode numbers

QSPI

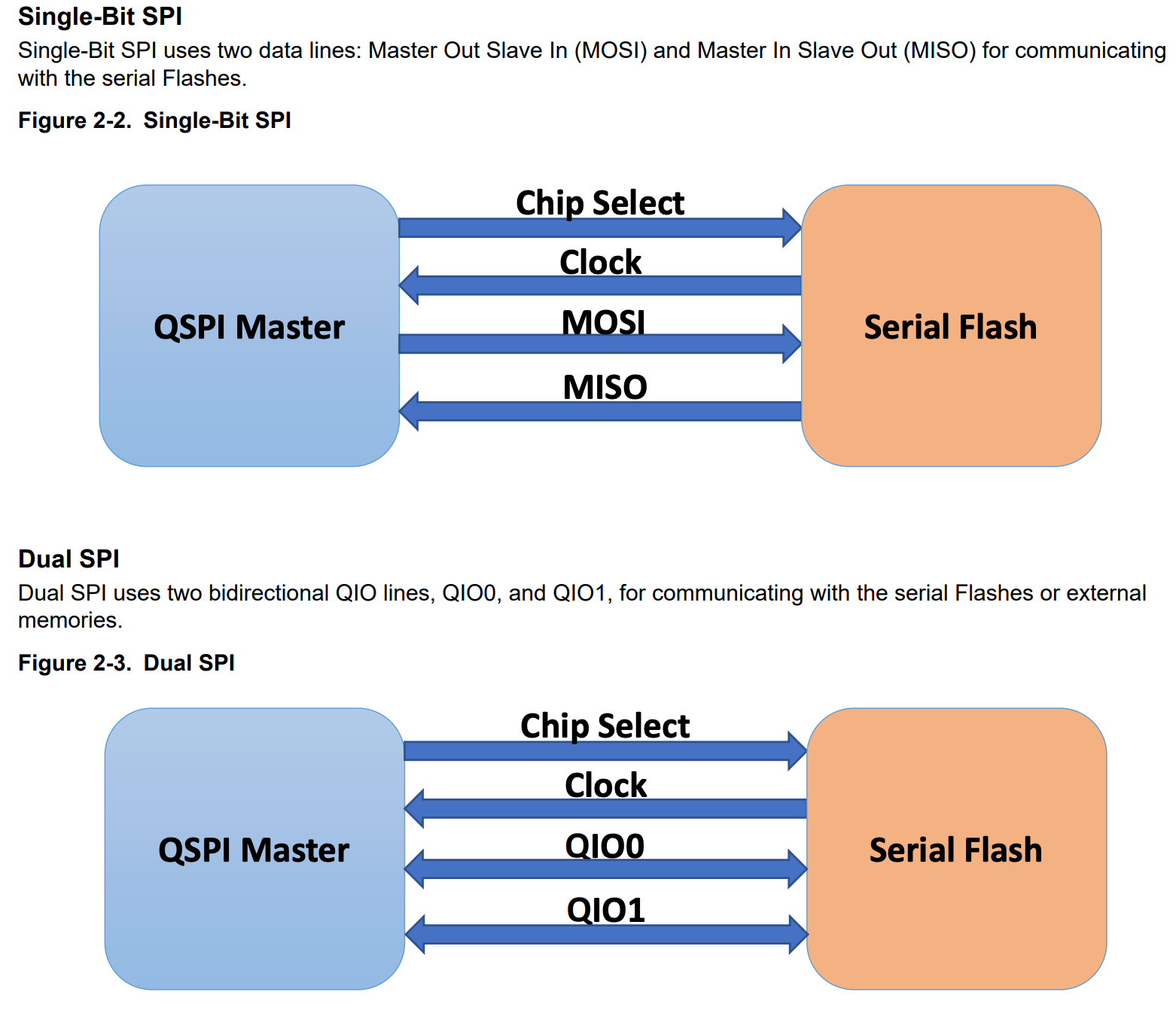

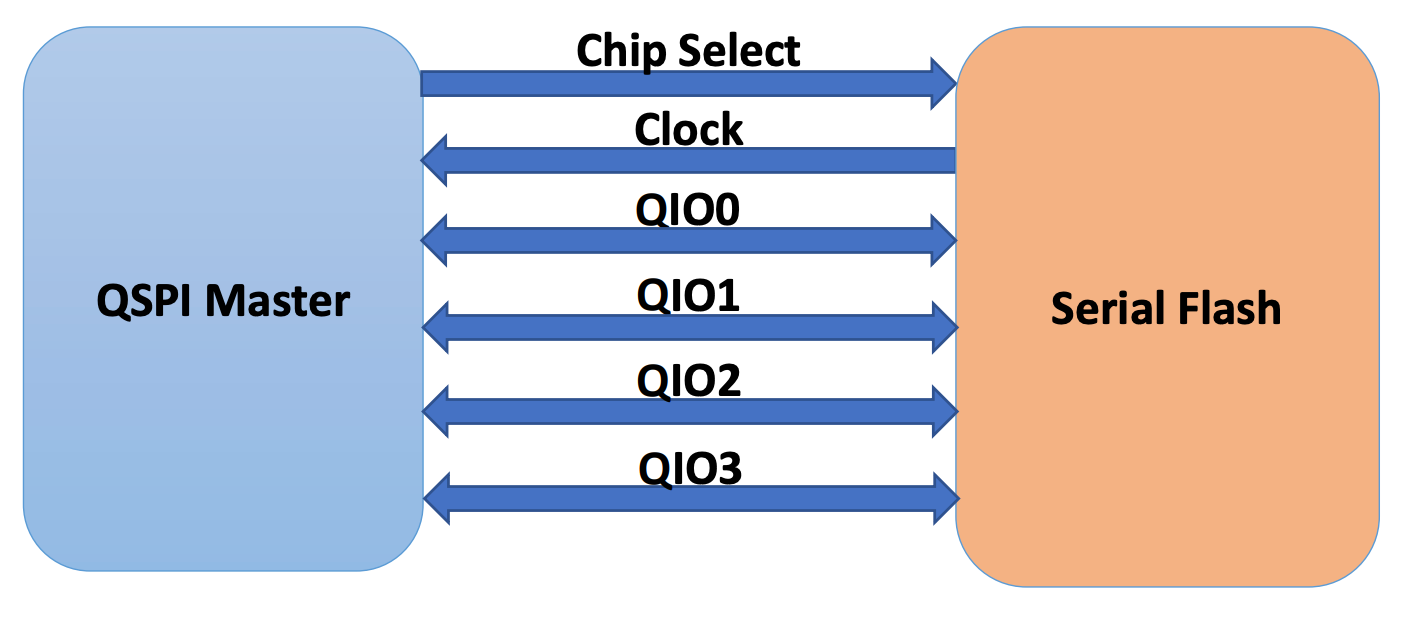

Queued SPI相对于SPI来说增加了两根I/O线(SIO2、SIO3),提供了每次传输的bit数。QSPI可以的工作模式Single-Bit SPI、Dual SPI、Quad SPI。

Quad SPI mode uses four bidirectional QIO lines for communicating with the serial Flashes or external memories.

浙公网安备 33010602011771号

浙公网安备 33010602011771号