02.Cortex-M3内核概述--从0学RTOS

Cortex-M3简介

Cortex-M3是一个32位处理器内核。内部的数据路径是32位的,寄存器是32位的,存储器接口也是32位的。CM3采用了哈佛结构,拥有独立的指令总线和数据总线,可以让取指与数据访问并行不悖。这样一来数据访问不再占用指令总线,从而提升了性能。为实现这个特性,CM3内部含有好几条总线接口,每条都为自己的应用场合优化过,并且它们可以并行工作。但是另一方面,指令总线和数据总线共享同一个存储器空间(一个统一的存储器系统)。换句话说,不是因为有两条总线,可寻址空间就变成8GB了。

比较复杂的应用可能需要更多的存储系统功能,为此CM3提供一个可选的MPU,而且在需要的情况下也可以使用外部的cache。另外在CM3中,Both小端模式和大端模式都是支持的。

CM3内部还附赠了好多调试组件,用于在硬件水平上支持调试操作,如指令断点,数据观察点等。另外,为支持更高级的调试,还有其它可选组件,包括指令跟踪和多种类型的调试接口。

主要特性

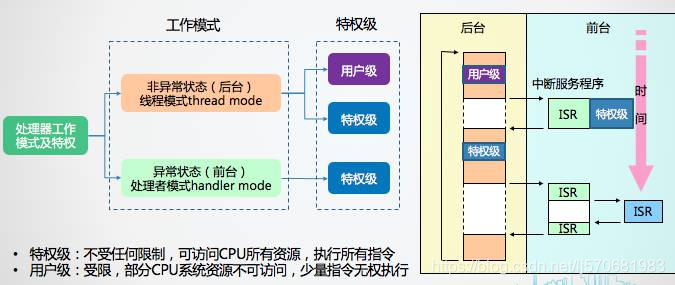

- 工作模式及权限级别

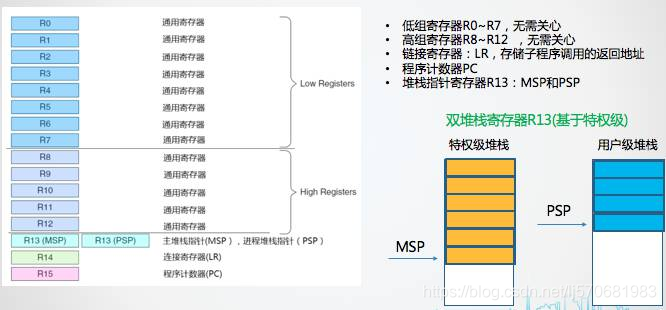

2. 内核寄存器

- R14用于存储子程序调用的返回地址

- R15指明了当前任务执行的指令位置

- R13指明当前任务所用的堆栈位置

- R0~R3主要用于程序调用时,参数的传递;执行程序时局部变量的存储

程序状态寄存器

3. 存储器映射

4. 堆栈

M3使用的是 向下生长的满栈 模型,采用双堆栈机制。

5. 异常和中断处理

M3支持的中断向量表

PendSVC异常

在执行具体的任务切换时,我们在设计中是通过向PendSVC异常发起请求,然后在PendSVC异常处理程序中具体执行任务切换的操作。

异常处理流程比较复杂,我们只需要记往以下几点:

进入异常

刚进入异常时,硬件自动会将以下寄存器压入当前堆栈(我们当前用的是PSP)。压入哪些内容以及他们的次序非常重要!

之后硬件自动跳转到PendSVC异常处理程序中运行。

退出异常

退出异常时,硬件会自动出栈,这个次序与进入异常时压栈的顺序刚好相反。可以理解为进入异常时保存了部分寄存器状态,退出时正好恢复。

此外,在退出异常时,我们还会用到EXC_RETURN,其中只用到了0xFFFF_FFFD(即返回异常时进入线程模式,使用PSP堆栈)。

注意,进入异常和退出异常时自动的出入栈会在后面的课时中视为任务部分状态的保存。

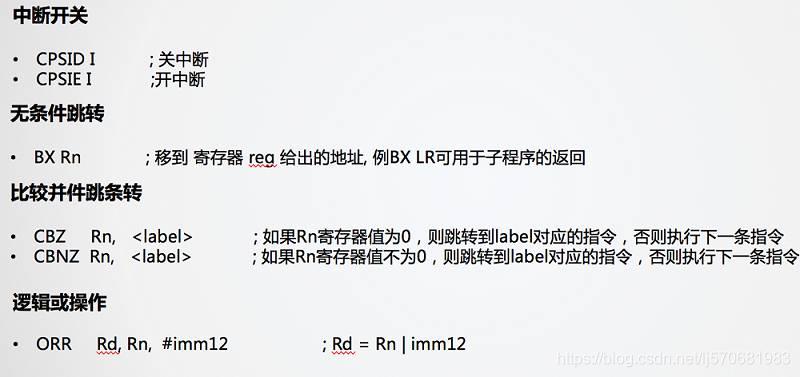

6. 汇编指令

在PendSVC中实现任务切换时,必须要用到一些汇编指令进行状态保存。课程中只介绍了用到的部分指令。

任务切换的原理

任务的切换主要就是利用系统的PendSV异常。在PendSV中执行RTOS的任务切换。

PendSV异常是作为优先级最低的,即任务切换的优先级低于其他中断优先级,这样任务切换要等到其他中断处理完成后才能处理,并且可以被其他的异常或中断抢占。

浙公网安备 33010602011771号

浙公网安备 33010602011771号