Xilinx开发板信息

自己的100Mhz时钟

自己的FPGA时钟管脚为C8,电平为LVCMOS15

set_property PACKAGE_PIN C8 [get_ports clk_i]

set_property IOSTANDARD LVCMOS15 [get_ports clk_i]

主时钟位于bank34,电压标准为1.5V,C8引脚。

开发板型号:

xc7z030-ffg676,-2,157200,78600,

DDR型号:

DDR: MT41K256M16RE-125

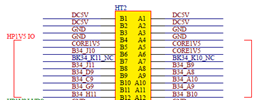

Bank配置

Bank0: 3.3V Bank1: 1.8V

QSPI配置

QSPI:MIO1--6 FC: 8

SD0配置:

SD0: 40:45 CD:47

UART1配置:

UART1: 48:49

F_CLK:

100Mhz

自己的HDMI时钟

74.25&371.25

系统时钟

管脚为C8

set_property IOSTANDARD LVCMOS15 [get_ports Clk]

set_property PACKAGE_PIN C8 [get_ports Clk]

复位引脚

管脚为H13

set_property IOSTANDARD LVCMOS18 [get_ports Rst_n]

set_property PACKAGE_PIN H13 [get_ports Rst_n]