数电研讨

! https://zhuanlan.zhihu.com/p/625343800

数电研讨

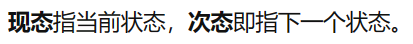

1 触发器波形图

1.1 讨论

1.1.1 脉冲触发方式的动作特点

脉冲触发方式是一种触发器的触发方式,它是由两个电平触发器串联构成的,一个是主触发器,一个是从触发器,它们的时钟信号是互补的。脉冲触发方式的动作特点有以下几点:

- 触发器的翻转分两步进行

- 第一步是在时钟信号为有效电平期间,主触发器接收输入信号并改变状态,从触发器不动;

- 第二步是在时钟信号变为无效电平时,从触发器按照主触发器的状态翻转,输出端的状态变化也发生在这一时刻。

- 触发器的输出状态只可能在时钟信号的约定跳变(正跳变或负跳变)时刻改变一次(一次变化效应),不会出现空翻现象。

空翻就是指在时钟信号CP=1的时间间隔内,输出结果Q会随着激励���号比如R和S的变化而变化。

1.1.2 与电平和边沿触发方式的比较

| 触发方式 | 动作特点 | 优缺点 |

|---|---|---|

| 电平触发 | 在时钟信号为有效电平期间,输出状态随输入状态变化;在时钟信号为无效电平期间,输出状态保持不变。 | 优点:结构简单,易于实现。缺点:容易受到干扰,出现空翻现象,抗干扰能力差。 |

| 边沿触发 | 在时钟信号的约定跳变(正跳变或负跳变)时刻,输出状态根据输入状态改变;在其他时间,输出状态保持不变。 | 优点:抗干扰能力强,不会出现空翻现象,工作可靠性高。缺点:结构复杂,难以实现。 |

| 脉冲触发 | 在时钟信号为有效电平期间,主触发器接收输入信号并改变状态;在时钟信号为无效电平期间,从触发器按照主触发器的状态翻转,输出端的状态也在这一时刻改变。 | 优点:结构相对简单,抗干扰能力较强。缺点:比边沿触发更容易受到干扰,比电平触发更复杂。 |

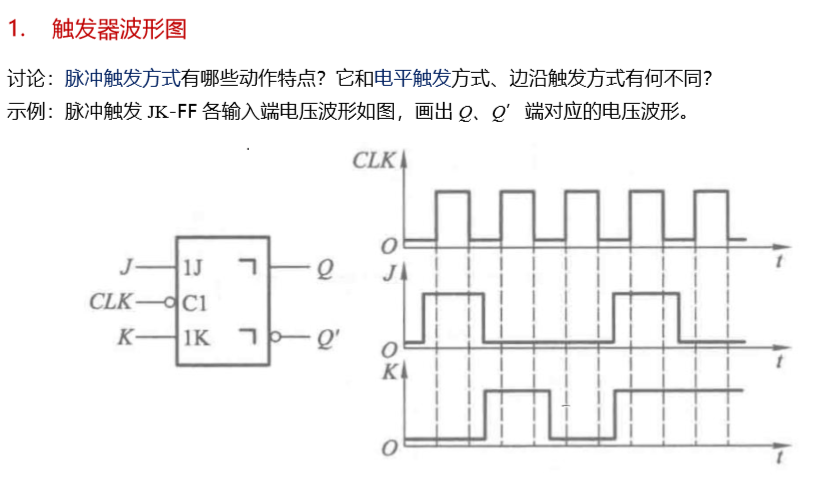

1.2 示例

时钟端低电压接入,上升沿触发。电压波形图如下所示

此图使用WaveDrom绘制,代码如下

{signal: [

{name: 'CLK', wave: 'lhlhlhlhlhl'},

{name: 'J', wave: 'lh.l...h.l.',phase:0.5},

{name: 'K', wave: 'l..h.l.h...',phase:0.5},

{name: 'Q', wave: 'lh.l...h.l.'},

{name: '!Q', wave:'hl.h...l.h.'}

]}

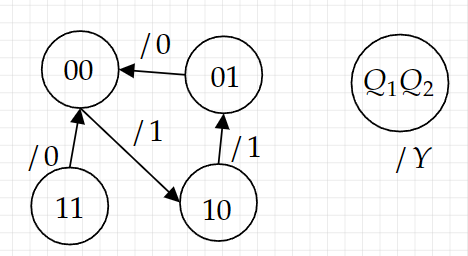

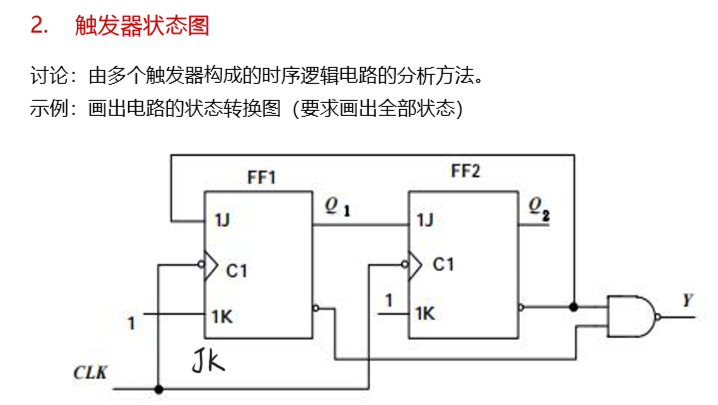

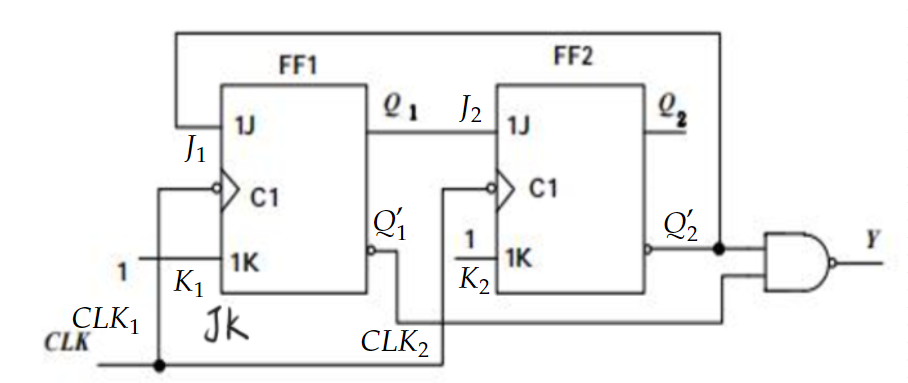

2 触发器状态图

2.1 讨论

分析由多个触发器构成的时序电路的一般步骤如下:

- 确定电路中各触发器的类型和触发方式,以及输入信号、输出信号和状态变量的数量和符号。

- 根据电路图,写出存储电路中每个触发器的驱动方程,得到整个电路的驱动方程

- 根据各触发器的特性表或特性方程,得到状态方程;写出输出方程。

- 根据驱动方程、状态方程和输出方程,绘制状态转换图或编写状态转换表,分析逻辑功能。

2.2 示例

- 图中为两个负边沿JK触发器,均为下降沿触发,输入信号为\(K_1,K_2,CLK\),输出信号为\(Y,Q_2\),状态变量有4个,分别是\(Q_1,Q_2,Q_3,Q_4\)

- 驱动方程为

- 代入JK触发器特征方程\(Q^*=JQ'+K'Q\)

- 输出方程

这里如果搞混了次态和现态就会做成下面这样:

- 输出方程

\[Y=((Q_1^*)'(Q_2^*)')'=Q_1^*+Q_2^* \tag{2.3} \]显然可得\(Y=Q_2'Q_1'+Q_1Q_2'=Q_2'\)

%

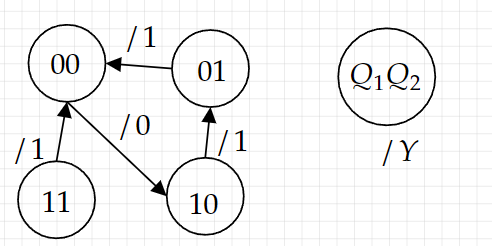

3 触发器动态特性

3.1 讨论

首先clk触发信号和每个门的延时有关,其次又跟电路的结构有关(可能到达的路径不同,导致时间不同)

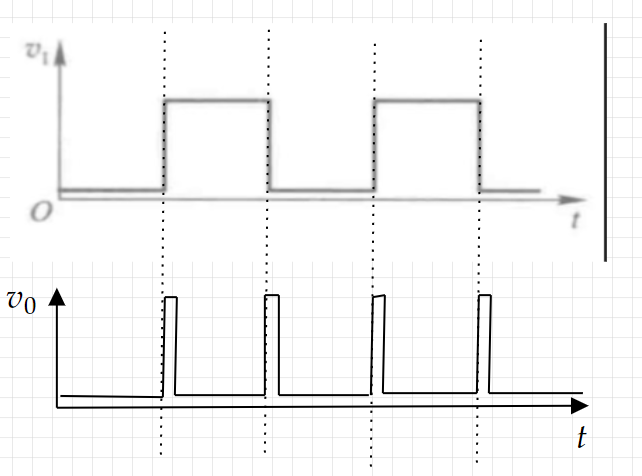

3.2 示例

开始是\(V_I=0,Q=0\),异或门输出等于0,当\(V_I\) 变成高电平的时,\(V_0\)输出为\(1\), 然后\(Q\)取反,异或完\(V_0\)再变成0.所以设延时时间为\(T\)

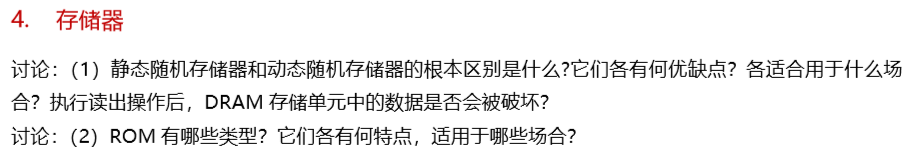

4 存储器

4.1 讨论1

SRAM和DRAM的根本区别是:存储单元不同。SRAM用触发器作为存储单元,DRAM用电容作为存储单元。SRAM用触发器作为存储单元,可以保持数据不变,只要不断电。DRAM用电容作为存储单元,需要周期性地刷新电荷,以维持数据。

其其他区别如下:

- SRAM的存取速度快,但集成度低,功耗高,成本高。DRAM的存取速度慢,但集成度高,功耗低,成本低。

- SRAM适合用于高速缓存、寄存器等需要快速访问的场合。DRAM适合用于主存、显存等需要大容量的场合。

- 执行读出操作后,DRAM存储单元中的数据会被破坏,因为电容上的电荷会流失。因此,需要在读出后立即写回电容,以恢复数据。

4.2 讨论2

ROM有以下几种类型:

| 类型 | 特点 | 适用场合 |

|---|---|---|

| MROM(掩膜ROM) | 由厂家按用户要求预先写入数据,不可修改 | 存放固定程序或数据 |

| PROM(可编程ROM) | 由用户一次性写入数据,不可擦除或修改 | 存放少量或临时程序或数据 |

| EPROM(可擦除可编程ROM) | 由用户多次写入数据,可通过紫外线擦除 | 存放经常更新的程序或数据 |

| EEPROM(电可擦除可编程ROM) | 由用户多次写入数据,可通过电信号擦除 | 存放频繁更新的程序或数据 |

| Flash ROM(闪存) | 由用户多次写入数据,可通过电信号快速批量擦除 | ���放大容量的程序或数据 |

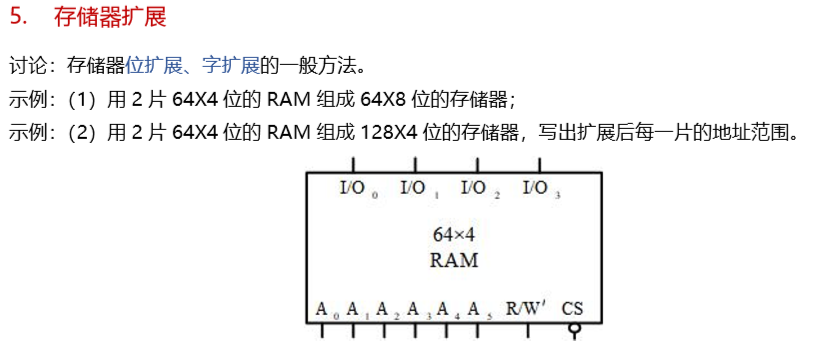

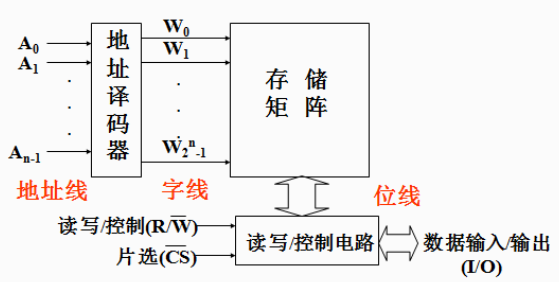

5 存储器拓展

5.1 讨论

5.1.1

存储单元:可存储一个二进制数位(bit),1或者0存储容量:存储单元的总数,存储容量常用“N(个字)×M(位)”表示。- 1024位的存储器,若字长为8,则存储128个字(128×8)

- 位扩展:只加大字长,而存储器的字数与存储器芯片字数一致,对所有片子使用共同片选信号。例如,用两片1K×4位的芯片可以组成1K×8位的存储器,将两片芯片的地址线、控制线并联,数据线分别引出。

- 字扩展:仅在字向扩充,而位数不变。需要由片选信号来区分各片地址。例如,用两片1K×8位的芯片可以组成2K×8位的存储器,将两片芯片的数据线、控制线与部分地址线并联,剩下地址线通过译码器获得片选信号²。

- 字位扩展:同时在字向和位向进行扩展。例如,用四片1K×4位的芯片可以组成4K×8位的存储器,利用译码器扩展地址线,同时扩展数据线。

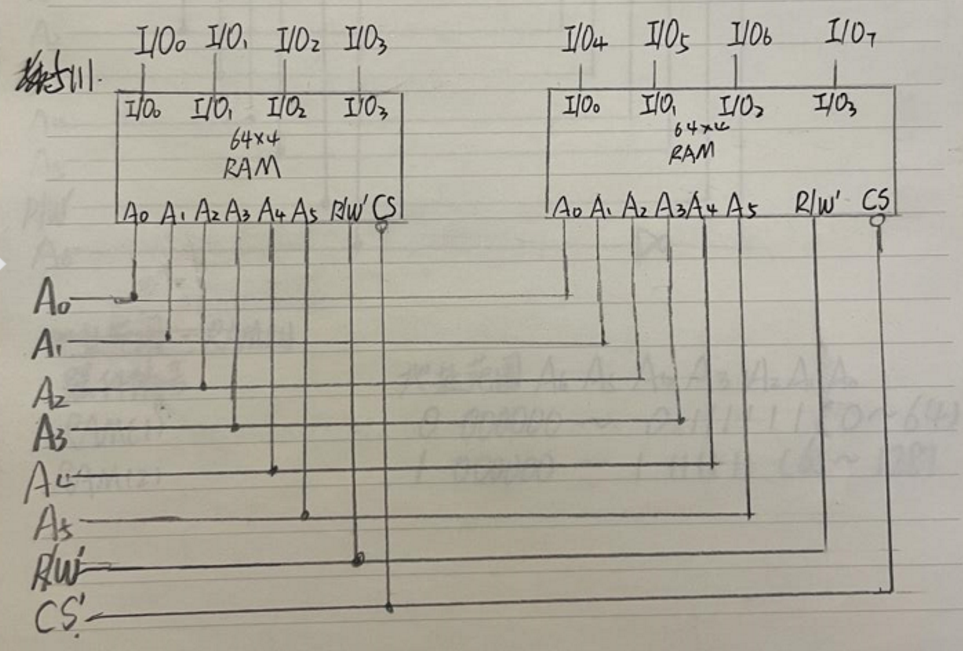

5.2 示例(1)

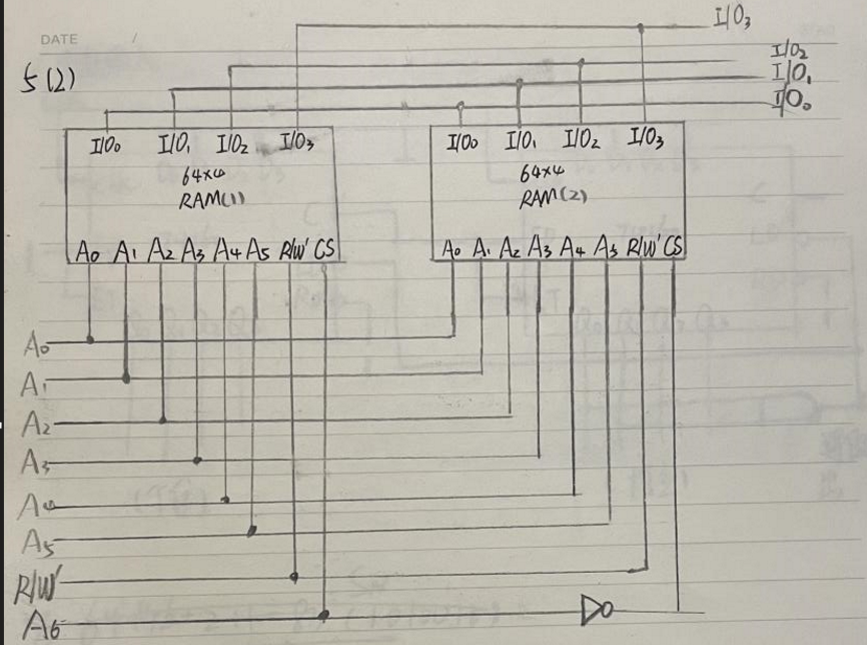

5.3 示例(2)

扩展后两片的地址范围:

6 任意进制计数器

6.1 讨论

任意进制计数器是一种可以实现任意模数(计数范围)和任意计数方式(顺序或逆序)的计数器。

任意进制计数器有以下几种设计方法,各有不同的特点:

- 反馈复位法:利用计数器的异步清零端或同步清零端,通过组合逻辑电路产生反馈信号,使计数器在达到某个状态后立即复位到初始状态,从而跳过不需要的状态。² 这种方法的优点是简单易行,缺点是可能产生过渡状态或限制了幅度特性的衰减速度。

- 反馈置数法:利用计数器的同步置数控制端和数据输入端,通过组合逻辑电路产生反馈信号,使计数器在达到某个状态后立即置入某个数值,从而跳过不需要的状态。² 这种方法的优点是灵活性高,可以置入任意数值,缺点是需要更多的逻辑电路和引脚。

- 级联法:利用多片集成计数器进行级联连接,通过控制进位或借位信号来实现任意进制计数器。 这种方法的优点是可以扩展计数范围,缺点是需要更多的芯片和线路。

为了方便比较,我用表格来总结这三种方法的特点:

| 方法 | 优点 | 缺点 |

|---|---|---|

| 反馈复位法 | 简单易行 | 可能产生过渡状态或限制了幅度特性的衰减速度 |

| 反馈置数法 | 灵活性高,可以置入任意数值 | 需要更多的逻辑电路和引脚 |

| 级联法 | 可以扩展计数范围 | 需要更多的芯片和线路 |

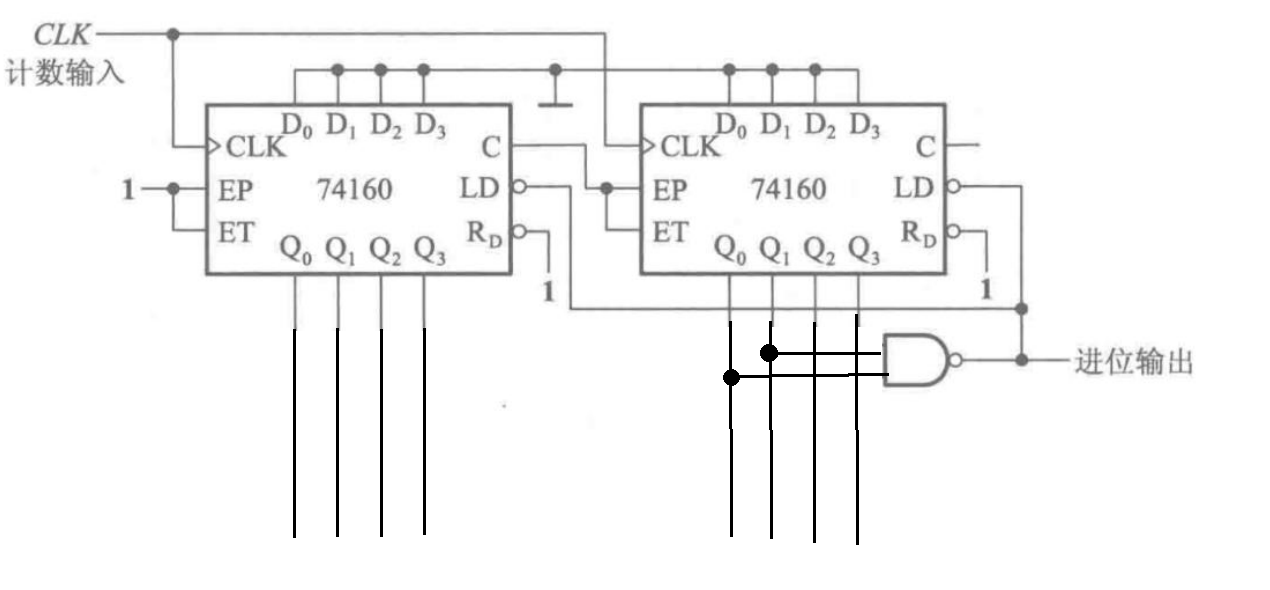

6.2 示例

7 任意进制计数器

7.1 讨论

智慧树原题

计数器的同步置零方式和异步置零方式的不同之处是:

- 同步置零方式是指计数器在接收到置零信号后,还需要等待时钟信号的有效沿(上升沿或下降沿)才能将输出状态置为零。 这种方式的优点是可以避免过渡状态的产生,缺点是需要额外的时钟信号。

- 异步置零方式是指计数器在接收到置零信号后,不需要等待时钟信号,立即将输出状态置为零。 这种方式的优点是响应速度快,缺点是可能产生过渡状态或干扰其他同步电路。

计数器的同步预置数方式和异步预置数方式的不同之处是:

- 同步预置数方式是指计数器在接收到预置数信号后,还需要等待时钟信号的有效沿才能将输出状态置为预设的数值。 这种方式的优点是可以灵活地设置任意数值,缺点是需要额外的时钟信号和数据输入端。

- 异步预置数方式是指计数器在接收到预置数信号后,不需要等待时钟信号,立即将输出状态置为预设的数值。 这种方式的优点是响应速度快,缺点是可能产生过渡状态或干扰其他同步电路。

为了方便比较,我用表格来总结这四种方式的特点:

| 方式 | 优点 | 缺点 |

|---|---|---|

| 同步置零 | 避免过渡状态 | 需要时钟信号 |

| 异步置零 | 响应速度快 | 可能产生过渡状态或干扰 |

| 同步预置数 | 灵活地设置任意数值 | 需要时钟信号和数据输入端 |

| 异步预置数 | 响应速度快 | 可能产生过渡状态或干扰 |

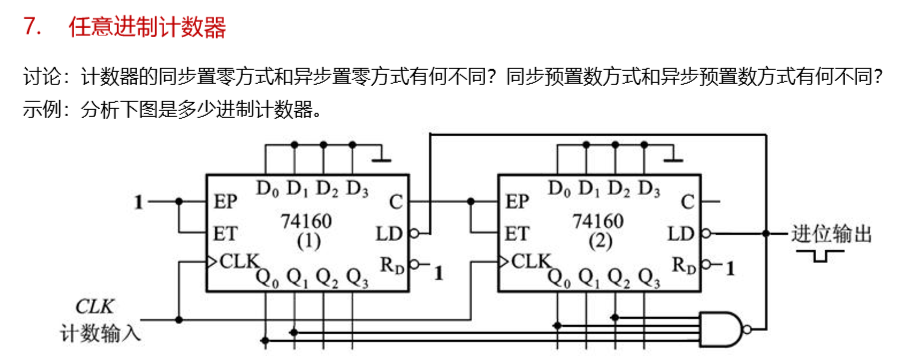

7.2 示例

0-53计数,所以图是 54 进制计数器。

8 任意进制计数器

8.1 讨论

当\(M=N_1\times N_2\)时N1和N2间的连接有两种方式:

- 串行进位方式:以低位片的进位输出信号作为高位片的时钟输入信号。这种方式适用于M=N1×N2的情况,其中M是目标进制,N1和N2是两个小于M的因数。

- 并行进位方式:以低位片的某些输出信号作为高位片的控制信号,使高位片在低位片达到某些状态时才进行计数。这种方式也适用于M=N1×N2的情况。

- 整体置零方式:以低位片的某些输出信号作为高位片的清零信号,使高位片在低位片达到某些状态时清零。这种方式适用于M>N的情况,其中M是目标进制,N是单片计数器的模。

- 整体置数方式:以低位片的某些输出信号作为高位片的置数信号,使高位片在低位片达到某些状态时置入预设值。这种方式也适用于M>N的情况。

| 方式 | 适用条件 | 特点 |

|---|---|---|

| 串行进位 | M=N1×N2 | 电路简单,但速度慢 |

| 并行进位 | M=N1×N2 | 电路复杂,但速度快 |

| 整体置零 | M>N | 电路简单,但有跳过状态 |

| 整体置数 | M>N | 电路复杂,但无跳过状态 |

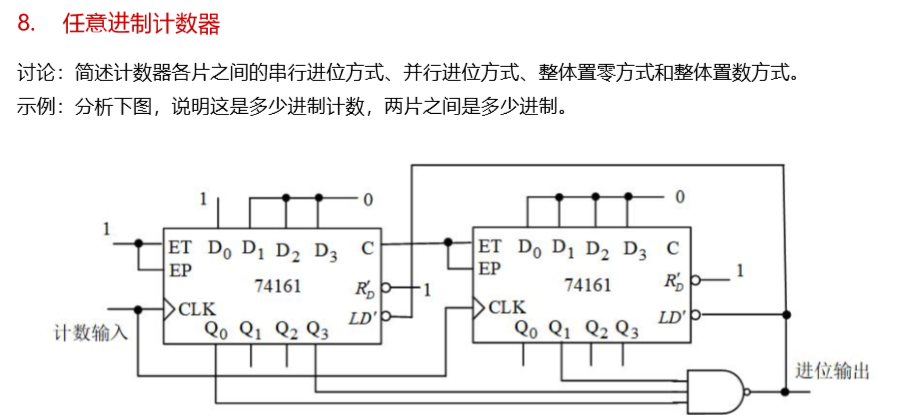

8.2 示例

第一个计数器在\(Q_3Q_2Q_1Q_0=0001-1001\) 所以是八进制计数器,第二个计数器是十六进制计数器.

图是 30位进制计数器。

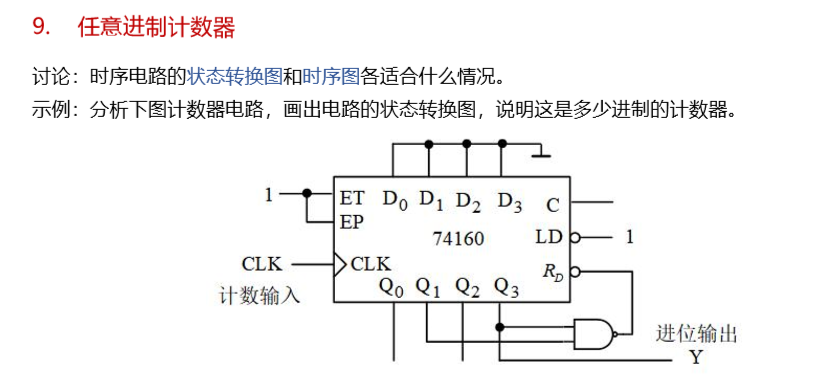

9 任意进制转换器

9.1 讨论

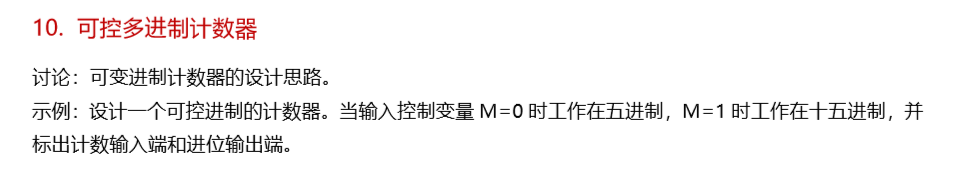

10 可控多进制计数器

10.2

电路的状态转换从 0000 至 1001,是 10 进制计数器

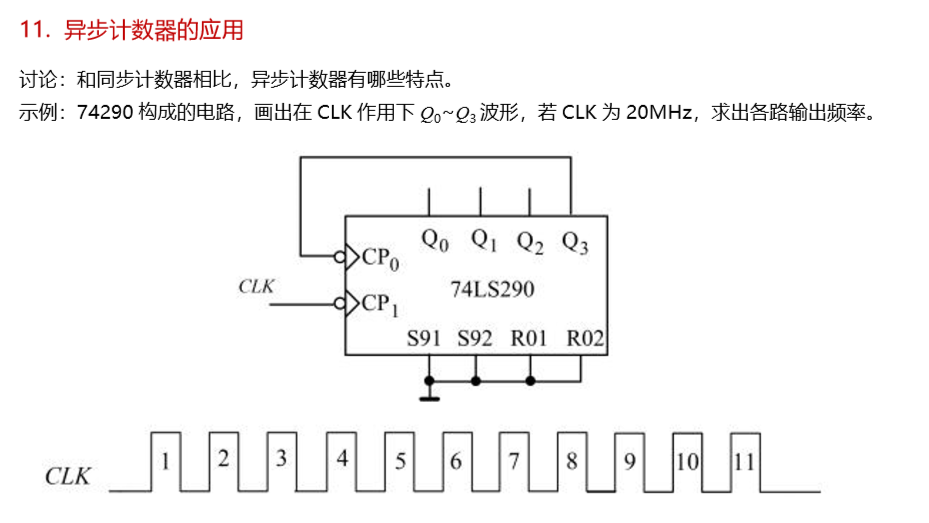

11 异步计数器的应用

12 时序电路设计

multisim仿真

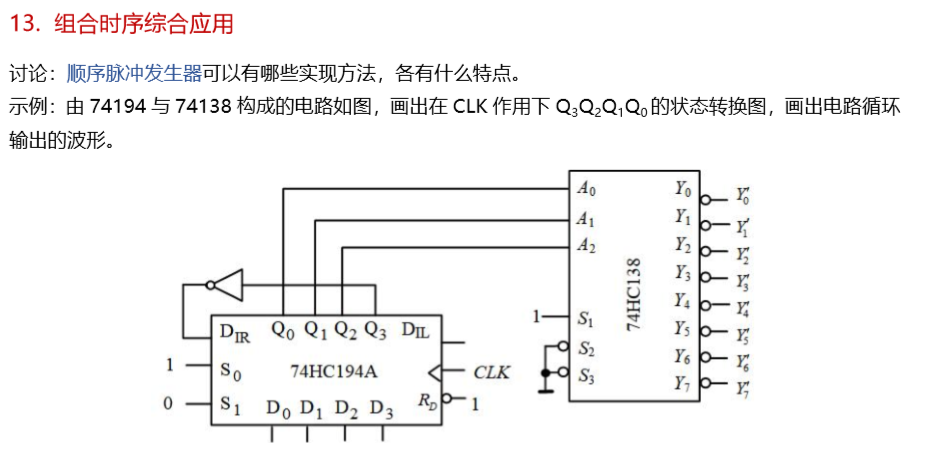

13 组合时序综合应用

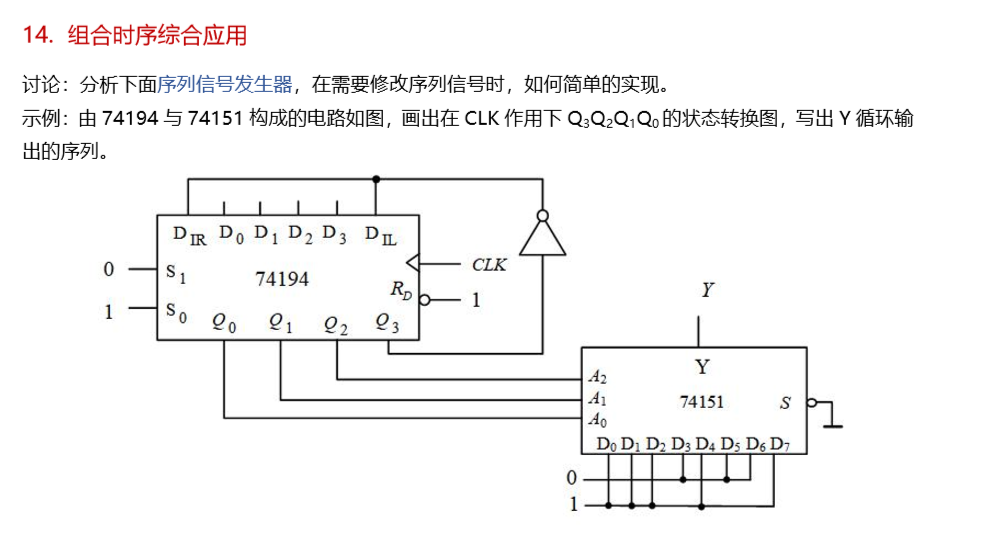

14 组合时序综合应用

数字电子技术中产生周期性序列信号的一些方法有:

- 使用计数器或移位寄存器等时序逻辑器件,通过时钟信号驱动,实现不同位数和进制的计数或移位操作,从而产生周期性的序列信号。例如,使用一个四位二进制计数器,可以产生一个16个时钟周期的序列信号。

- 使用只读存储器(ROM)或随机存取存储器(RAM)等存储器件,将预先编写好的周期性序列信号存储在其中,然后通过地址线和数据线输出相应的序列信号。例如,使用一个8位8字节的ROM,可以存储8个8位的周期性序列信号。

- 使用数字信号处理(DSP)芯片或可编程逻辑器件(PLD)等高级器件,通过软件编程或硬件描述语言(HDL),实现复杂的周期性序列信号的生成和处理。例如,使用一个DSP芯片,可以实现正弦波、方波、三角波等不同形式的周期性序列信号的生成。

示例:设计一个序列信号发生器电路,使之在一系列CLK信号作用下能周期性地输出"0010110111”的 序列信号。

这个问题可以有多种解决方案,其中一种可能的���案是:

- 使用一个10位移位寄存器(Shift Register),将其配置为串入并出(Serial In Parallel Out)模式,即每个时钟周期从最低位输入一个数据位,并从所有位同时输出一个数据位。

- 将移位寄存器的最高位Q9和最低位Q0连接到一个异或门(XOR Gate),将异或门的输出连接到移位寄存器的串行输入端S。

- 将移位寄存器的并行输出端Q0~Q9连接到一个10位数据总线上,作为序列信号发生器的输出端。

- 将移位寄存器的清零端CLR接地,将移位/加载端SL接高电平,将时钟端CP接到CLK信号源上。

- 在初始状态下,将移位寄存器加载为"0010110111"���个数据,然后开始移位操作。

- 每个时钟周期,移位寄存器会将Q9和Q0进行异或运算,并将结果输入到S端,同时将原来的Q0Q8依次右移一位,并从Q0Q9输出。

- 由于"0010110111"这个数据是一个10位循环码(Cyclic Code),即任意两个相邻的数据位进行异或运算得到的结果与下一个数据位相同,所以经过10个时钟周期后,移位寄存器会恢复到初始状态,并重复输出"0010110111"这个序列信号。

15 硬件描述语言

15.1 讨论

Verilog语言描述任意进制计数器的一种方法是:

- 使用parameter定义计数器的进制N和输出位宽DWIDTH,DWIDTH应该等于以2为底的N的对数向上取整。

- 使用一个DWIDTH位的寄存器temp作为计数器的内部状态,初始值为0。

- 使用一个输入信号clk作为时钟,一个输入信号rst作为复位,一个输出信号Q作为计数器的输出。

- 当rst为1时,将temp清零;当rst为0时,当clk上升沿到来时,将temp加1,并判断是否达到N-1,如果是,则将temp清零,否则保持temp不变。

- 将temp的值赋值给Q作为输出。

用markdown给出的Verilog代码如下:

module counter(

input clk, //时钟信号

input rst, //复位信号

output [DWIDTH-1:0] Q //输出信号

);

parameter N = 10; //计数器的进制

parameter DWIDTH = 4; //计数器的输出位宽

reg [DWIDTH-1:0] temp; //计数器的内部状态

always @(posedge clk or posedge rst) begin

if (rst) begin //复位时清零

temp <= 0;

end else begin //时钟上升沿时加1

temp <= temp + 1;

if (temp == N-1) begin //达到最大值时清零

temp <= 0;

end

end

end

assign Q = temp; //将内部状态赋值给输出

endmodule

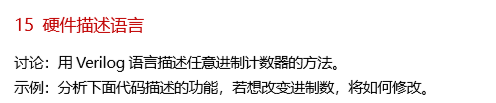

15.2

根据代码,这是一个四位十进制加减��数器的Verilog描述。它的功能如下:

- 有一个四位寄存器data_r作为计数器的内部状态,初始值为0。

- 有一个输入信号clk作为时钟,一个输入信号clr作为异步清零,一个输入信号load作为异步预置数,一个输入信号up_down作为加减控制,一个四位输入信号DIN作为预置数输入。

- 有一个输出信号c作为进位或借位,用于级联其他计数器,一个四位输出信号DOUT作为计数输出,与data_r相同。

- 当clr为1时,无论时钟如何变化,都将data_r清零;当clr为0时,如果load为1,则将data_r设置为DIN的值;如果load为0,则根据时钟和up_down的值进行加减计数。

- 当up_down为1时,进行加计数;当up_down为0时,进行减计数。加减计数都是在时钟上升沿进行。

- 加计数时,如果data_r等于1001(十进制9),则将data_r清零,并将c置为1;否则将data_r加1,并将c置为0。

- 减计数时,如果data_r等于0000(十进制0),则将data_r设置为1001(十进制9),并将c置为1;否则将data_r减1,并将c置为0。

若想改变进制数,可以修改以下几个地方:

- 修改parameter N的值为目标进制数。

- 修改parameter DWIDTH的值为以2为底的N的对数向上取整。

- 修改寄存器data_r和输入信号DIN的位宽为DWIDTH。

- 修改输出信号DOUT和c的位宽为DWIDTH和DWIDTH+1。

- 修改加减计数时的判断条件和赋值语句,使之符合目标进制数。

例如,若想改成八进制计数器,则可以修改如下:

module counter(

input clk, //输入时钟

input clr, //异步清零

input load, //异步预置数

input up_down, //加减控制

input [2:0] DIN, //预置数输入

output [3:0] c, //进位或借位

output [2:0] DOUT //计数输出

);

parameter N = 8; //目标进制数

parameter DWIDTH = 3; //输出位宽

reg [DWIDTH-1:0] data_r; //内部状态

always @(posedge clk or posedge clr or posedge load) begin

if (clr) begin //异步清零

data_r <= 0;

end else if (load) begin //异步预置数

data_r <= DIN;

end else begin //加减计数

if (up_down) begin //加计数

if (data_r == N-1) begin //达到最大值

data_r <= 0;

c <= 1;

end else begin //未达到最大值

data_r <= data_r + 1;

c <= 0;

end

end else begin //减计数

if (data_r == 0) begin //达到最小值

data_r <= N-1;

c <= 1;

end else begin //未达到最小值

data_r <= data_r - 1;

c <= 0;

end

end

16 硬件描述语言

16.1 讨论

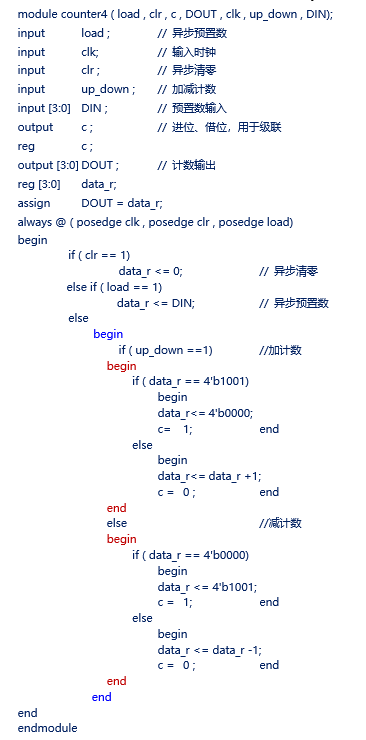

顺序脉冲发生器是一种能够按照一定的顺序和规律产生一组脉冲信号的电路。它可以用于控制电路中,实现对各种操作和运算的时序控制。例如,它可以用于数控装置中,控制机床的动作;也可以用于数字计算机中,控制指令的执行和数据的传输。

16.2 示例

这段Verilog代码描述了一个8位顺序脉冲发生器的电路。它的逻辑功能如下:

- 当clr信号为1时,异步地将寄存器temp预置为00000001,即只有最低位为1,其他位为0;同时将X置为0。

- 当clk信号上升沿到来时,如果clr信号为0,则执行以下操作:

- 将temp的最高位赋值给X,作为序列最高位输出;

- 将temp左移一位,即将原来的第二位移到第一位,依次类推;

- 将X赋值给temp的最低位,形成一个环形移位寄存器。

- 将temp的值赋值给Q,作为顺序脉冲输出。

因此,这个电路可以实现一个8位循环移位寄存器,并将其输出作为顺序脉冲。例如,当clr信号为1时,Q输出为00000001;当clk信号上升沿到来时,Q输出变为10000000;再次上升沿到来时,Q输出变为01000000;依次类推。

17 硬件描述语言

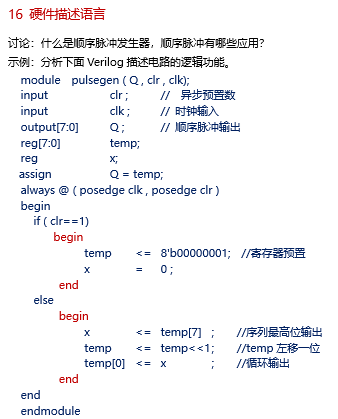

17.1 讨论

序列信号是一种离散时间信号,它只在整数时刻有定义,可以看作是连续时间信号的抽样。

序列信号的一个例子是数字信号,它是用二进制代码表示的信号,可以在数据通信系统中传输信息。

在通信系统中,序列信号有多方面的应用,例如:

调制和解调:通过改变序列信号的幅度、频率或相位来搬移信号的频谱,实现频分复用或抗干扰能力。滤波:通过使用带通滤波器或其他形式的窗函数来选择或抑制序列信号中的某些频率分量,实现信号的恢复、增强或压缩。变换:通过使用傅里叶变换、拉普拉斯变换、希尔伯特变换等方法来分析序列信号的频域特性,实现信号的分解、合成或特征提取。

17.2 示例(代码分析)

module xlgen(Q,clk,res); 有三个端口:Q,clk,res

input clk; //时钟输入

input res; //异步预置信号

output Q; //序列信号输出

reg Q; //定义Q为寄存器类型

reg[7:0] Qr; //定义Qr为8位寄存器类型

always@(posedge clk,posedge res) //上升沿触发

begin

if (res ==1)

begin

Q <=1'b0; //将Q清零

Qr <=8'b11100100; //将Qr寄存预定的序列

end

else

begin

Q <=Qr[7]; //将序列最高位输出到Q

Qr <=Qr<<1; //将Qr左移一位

Qr[0] <=Qr[7]; //将序列的最高位循环到最低位

end

end

endmodule

该代码的逻辑功能是实现一个8位线性反馈移位寄存器(LFSR),用于生成一个伪随机序列信号。当预置信号为1时,可以初始化寄存器的内容;当预置信号为0时,可以根据寄存器的内容产生序列信号,并更新寄存器的内容。该序列信号可以用于通信系统中的扩频、加密、测试等应用。

附录

参考文献

-

主从RS触发器的多次空翻现象怎么解释? - 知乎. https://www.zhihu.com/question/355666762

-

第六章·时序逻辑电路 - 知乎 - 知乎专栏. https://zhuanlan.zhihu.com/p/548544807

-

时序电路——DFF再理解 - 知乎 - 知乎专栏. https://zhuanlan.zhihu.com/p/372453668

-

什么是数据?什么是信号?在数据通信系统中有几种信号形式?_百度知道. https://zhidao.baidu.com/question/395837844.html

-

信号与系统中脉冲(pulse)和冲激(impulse)区别何在? - 知乎. https://www.zhihu.com/question/

-

任意进制计数器 || 反馈复位法 反馈置数法 || 超级重点 || 数电 - 知乎. https://zhuanlan.zhihu.com/p/163842599 访问时间 2023/4/28.

-

任意进制计数器设计方案汇总(七款模拟电路设计原理详解) - 应用电子电路 - 电子发烧友网. https://www.elecfans.com/dianlutu/187/20180117617698.html 访问时间 2023/4/28.

-

使用74LS161设计任意进制计数器 - CSDN博客. https://blog.csdn.net/qq_64366997/article/details/124776070 访问时间 2023/4/28.

复习

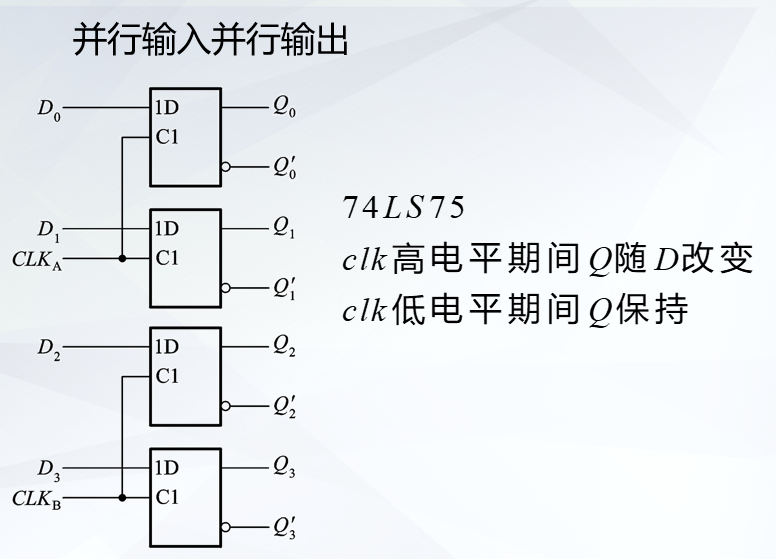

寄存器和移位寄存器

在数字电路中,用来存放一组二进制数据或代码的电路称为寄存器。其由多个触发器构成,一个触发器可存储一位二进制代码。

- 按照功能,寄存器分为普通寄存器(基本寄存器)和移位寄存器两大类。

- 按照输入输出,其分为并行和串行方式。

移位寄存器

具有存储加移位功能,串行输入