触发器

! https://zhuanlan.zhihu.com/p/625225272

0 触发器

1 SR触发器(SR锁存器)

SR锁存器(Set-Reset Latch)是静态存储单元当中最基本、也是电路结构最简单的一种。通常它由两个或非门或者与非门组成。

- S是set,有效置1,R是reset,有效置0。并且注意或非门构成的SR是正有效,与非门是负有效。

不确定是因为如果RS同时有效,状态被置为后效,但是下一次进保持的话就不确定。

1.1 一些表示

其主要有状态转换表,特性方程,状态转换方程,波形图四种。

1.1.1 状态转换表

下面以或非门为例子(与非门是负有效,并且主语)

| S | R | \(Q^n\) | \(Q^{n+1}\) |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | d |

| 1 | 1 | 1 | d |

1.1.2 特性方程和卡诺图

卡诺图如下:

| \(Q^{n}/SR\) | 00 | 01 | 11 | 10 |

|---|---|---|---|---|

| 0 | 0 | 0 | d | 1 |

| 1 | 1 | 0 | d | 1 |

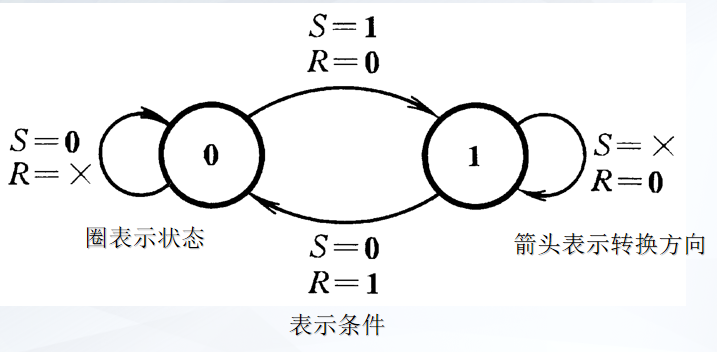

1.1.3 状态转换图

1.1.4 波形图

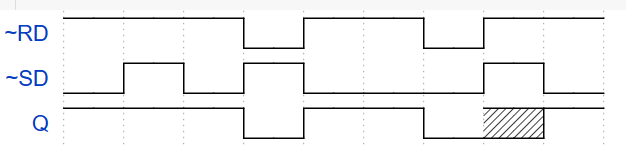

{name: '~RD', wave: 'h..lh.lh.'},

{name: '~SD', wave: 'lhlhl..hl'},

{name: 'Q', wave: 'h..lh.l*h'}

]}

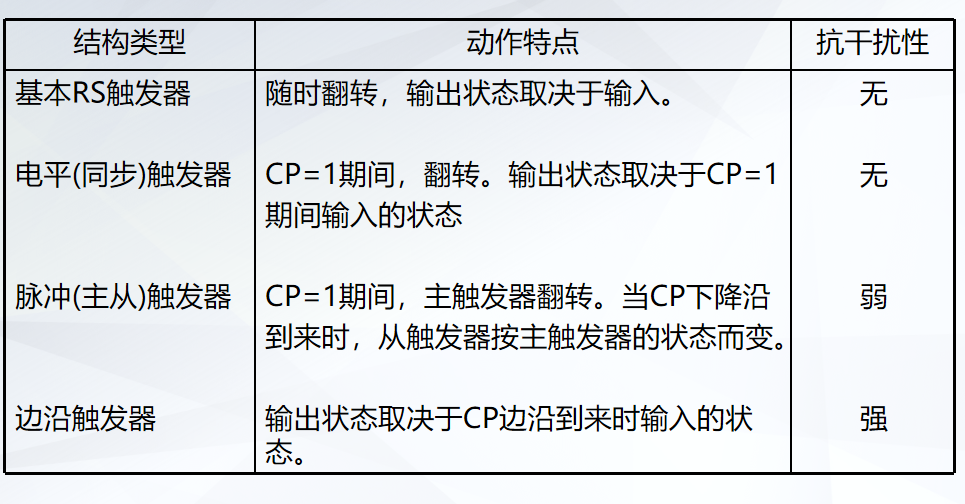

2 同步触发器(电平触发)

为使某些触发器于同一时刻动作,引入时钟(信号),用CP/CLK(Clock Pulse)表示。

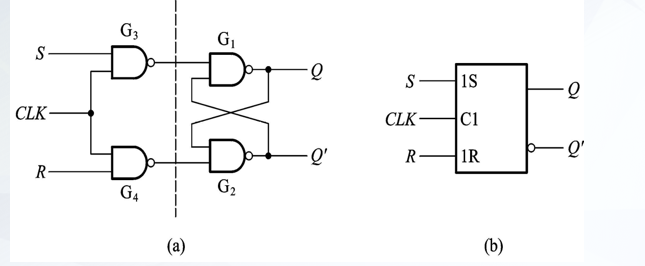

2.1 同步RS触发器

使用与非门,clk低电平时S=1,R=0,电路为保持状态。只有高电平时才触发。

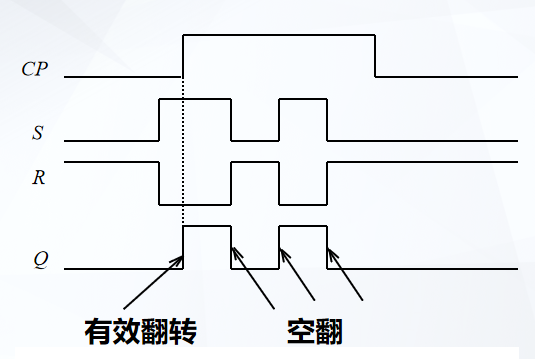

- 抗干扰性好。但是输入有约束限制,会发生空翻。

2.2 其他功能

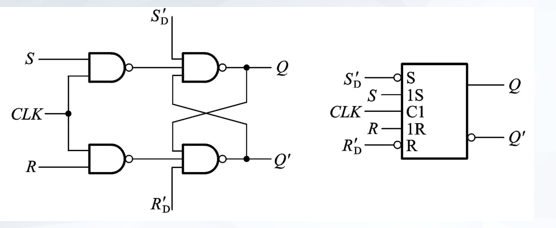

2.2.1 异步置0(1)端

有时需要在任意状态将触发器的状态置成制定的状态,为此设置了异步置1(0)端。\(S'_D,R'_D\)均为负有效。

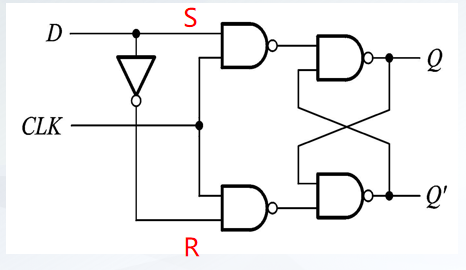

2.2.2 D触发器(同步RS触发器)

为了适应单端输入信号的场合,我们固定\(S=DR=\overline{D}\),称为D锁存器

2.3 例题

2.3.1 例题1

2.3.2 例题2

cp=1期间,若input多次变化,output将多次翻转,从而降低了电路的抗干扰能力。作为计数使用时,将发生空翻。

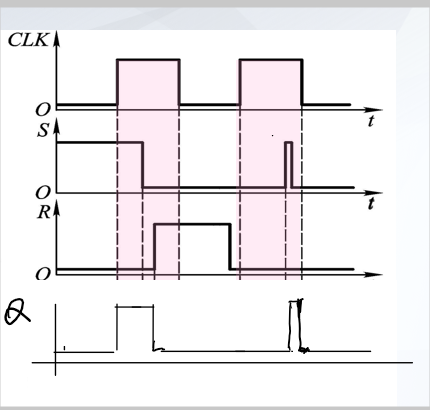

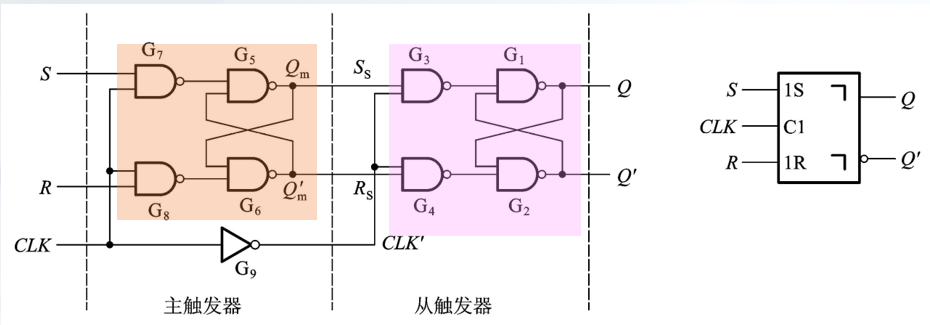

3 主从RS触发器(脉冲触发)

提高可靠性,要求每个CLK周期输出状态只能改变1次。其由两个同步RS触发器相连(也可以理解成前RS后D),二者时钟输入相反\(CLK \cdot CLK'=0\)。如下

其工作周期如下:

- 当CLK=1时,CLK’=0,从触发器被封锁。

- 当CLK由1跃变到0时。主触发器被封锁,从触发器作为D触发器工作,复制主输出器状态输出。

显然其只在时钟下降沿工作。而且其也还存在输入约束的问题,必须\(R\cdot S=0\)

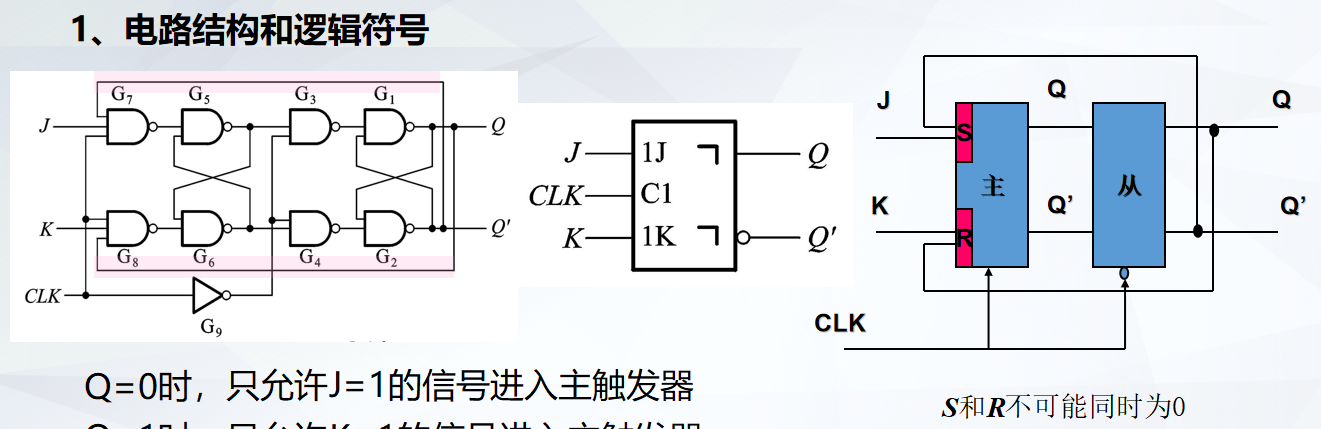

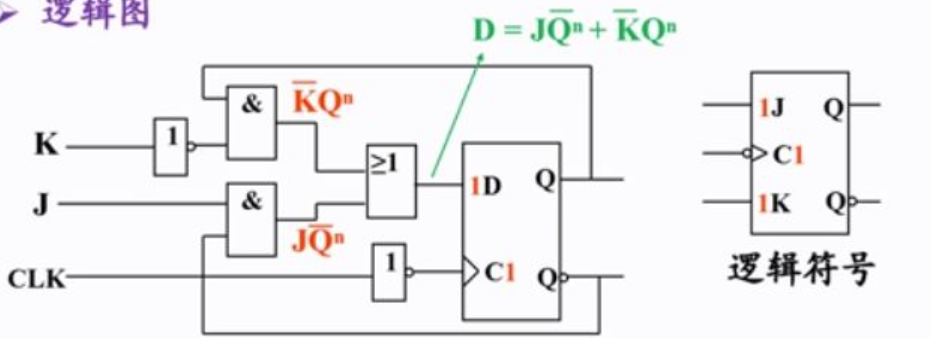

3.1 主从JK触发器

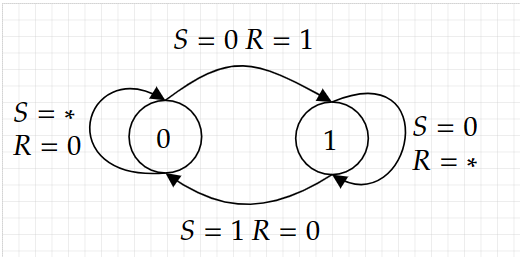

其将最终的输出Q接入到开始的K(R),Q*接入到开始的J(S)中去。取消了输入约束的限制,SR不可同时为0。看基本RS(注意是与非门)的状态转换图来分析(先不考虑主从)

- \(Q=0,Q^*=1\)时,R输出锁定为1,此时只对\(S=0\) \((J=1)\)的输入产生转换。

- \(Q=1,Q^*=0\)时, S输出锁定为1,此时只对\(R=0\) \((K=1)\)的输入产生转换。

根据上述转换形式,显然可列出其状态转换表

| J | K | Q | Q' |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

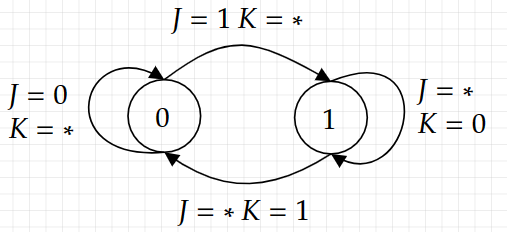

其不再具有输入约束,我们画出其状态转换图

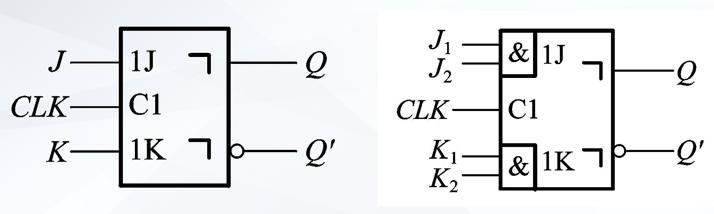

其符号表示

其也被叫做JK触发器。特性方程为

(其实上面的推导过于复杂了,直接将\(S=JQ' \quad R=R'Q\)代入式(1.1))

显然可得其没有输入约束。

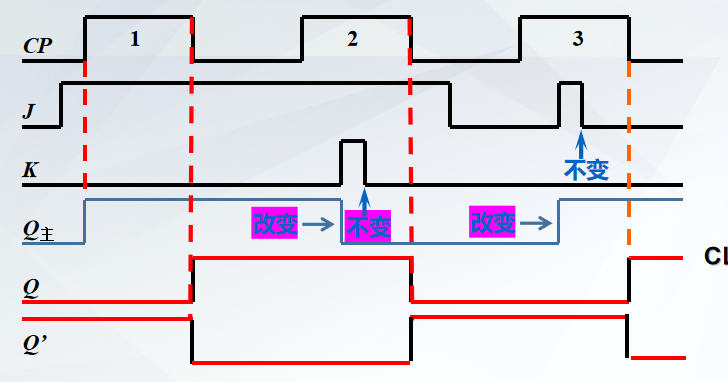

3.1.1 一次变化效应

CP=1期间,JK发生了变化,最终的输出只能随JK特性方程变化一次,这个叫 “1次变化效应”。

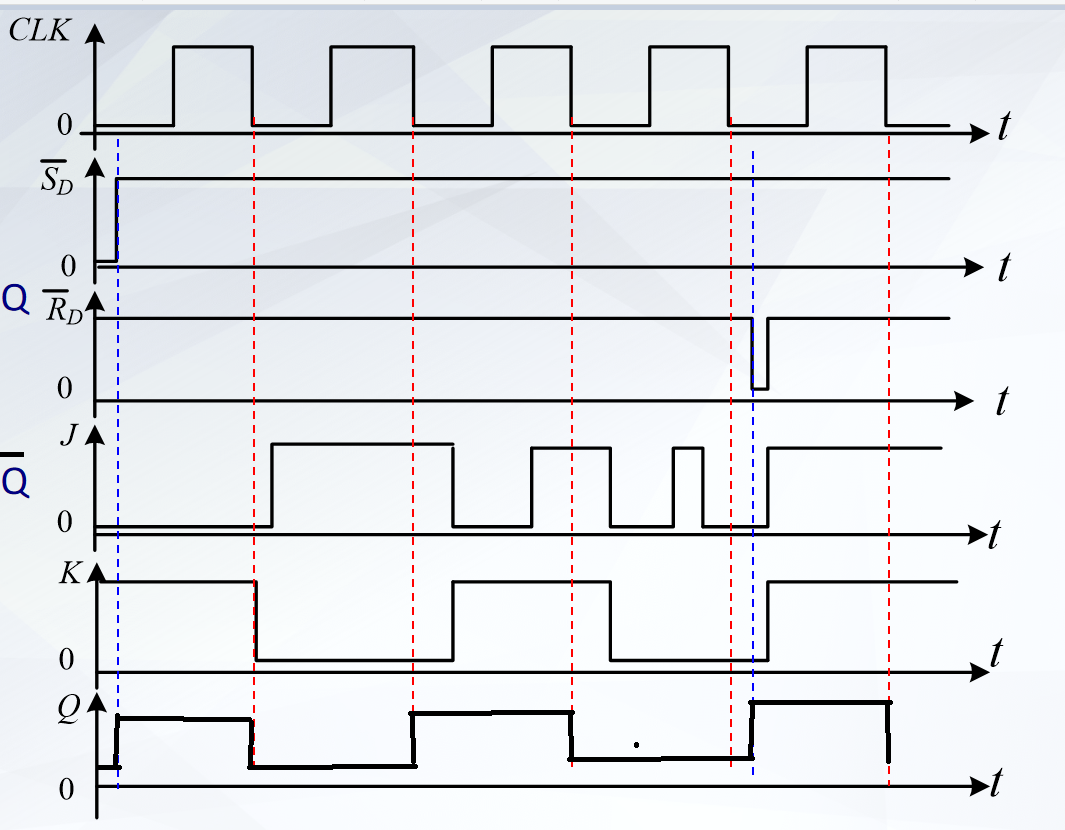

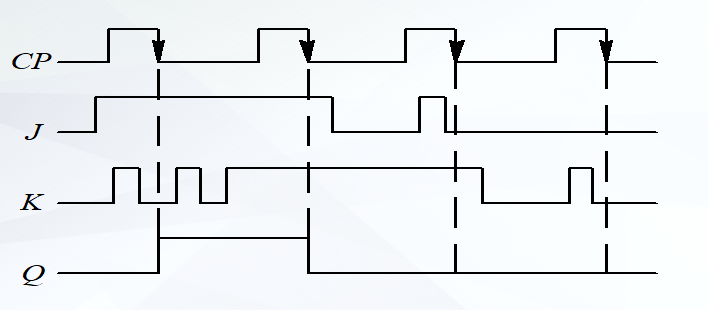

3.1.2 example

4 边沿触发器

我们希望触发器的次态仅取决于CLK的下降沿(或上升沿)到来前瞬间的输入信号状态,与在此前、后输入的状态没有关系。

4.1 电路结构和工作原理

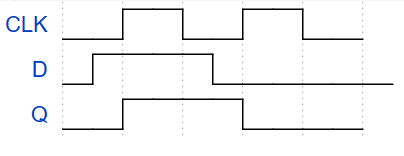

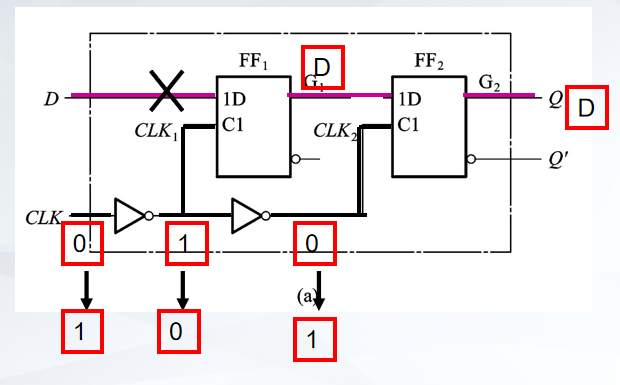

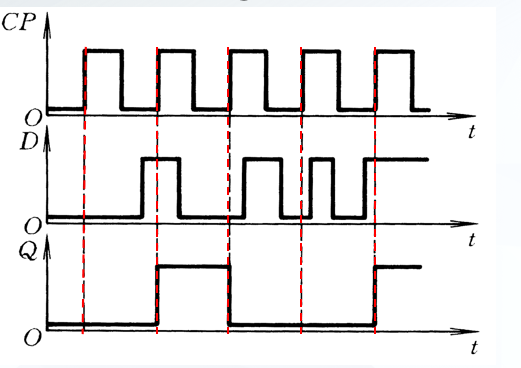

这是用两个电平触发D触发器组成的边沿触发器,显然是当且仅当在上升沿会触发

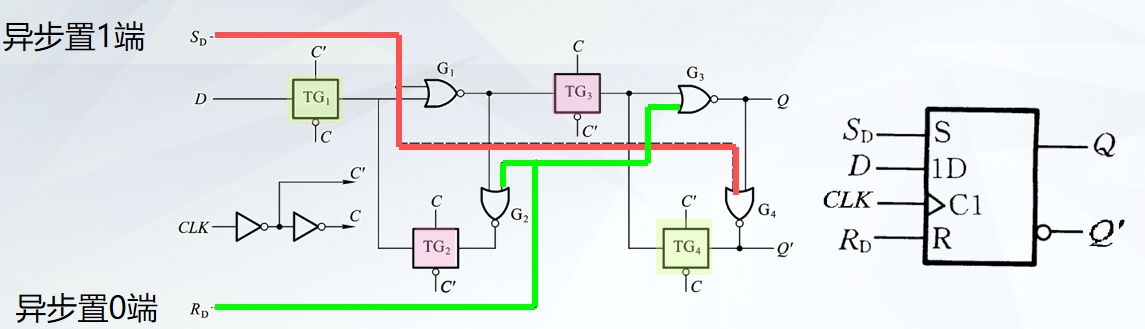

4.2 边沿D触发器

\(R_D\)、\(S_D\)为直接置“0”、置“1”端,高电平有效。其操作不受CP控制,因此也称异步置“0”、置“1”端

4.3 触发器分类和比较

上升沿触发。

4.4 负边沿JK触发器

对时钟信号加了一个反相器,也就是只有下降边沿有效。

5 触发器的描述方法

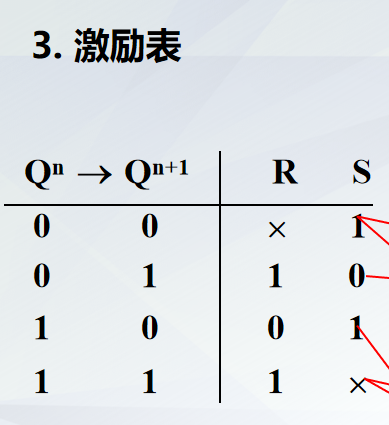

按照逻辑功能的不同特点,通常将时钟控制的触发器分为RS触发器、JK触发器、D触发器和T 触发器等几种类型。

描述其的方法主要有 特性表、状态卡诺图、特性方程、状态转换图等。

5.1 特性表

5.2 状态卡诺图

5.2.1 卡诺图

5.3 特性方程

5.4 状态转换图

D

T

各触发器之间的转换等

建立时间,延迟时间

附录 A

A.1 例题

例题1