深入浅出计算机组成原理学习笔记:第十四讲

一、顺序乘法的实现规程

1、十进制中13乘以9,转换成二进制整个计算的过程

乘法口诀表了,因为单个位置上,乘数只能是0或者1,所以实际的乘法,就退化成了位移和加法

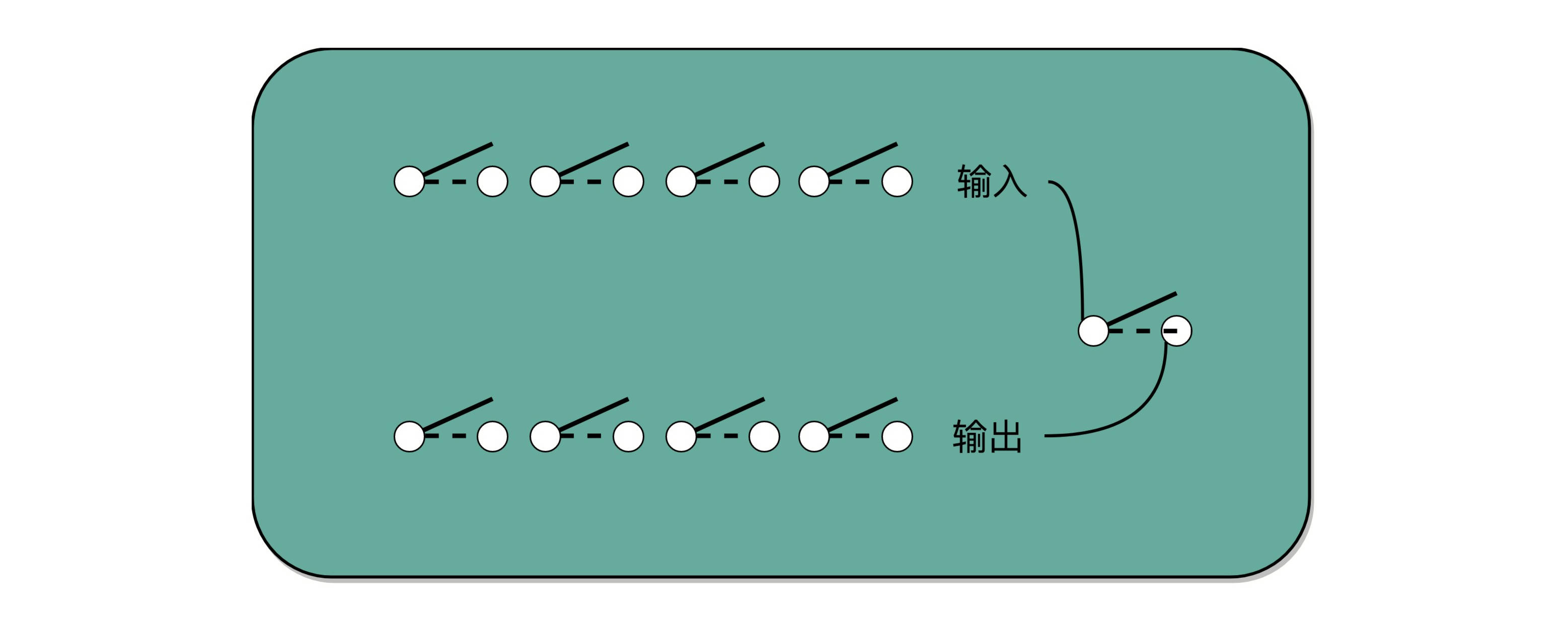

2、我们可以用一个开关来决定,下面的输出是完全复制输入,还是讲输出全部设置为0

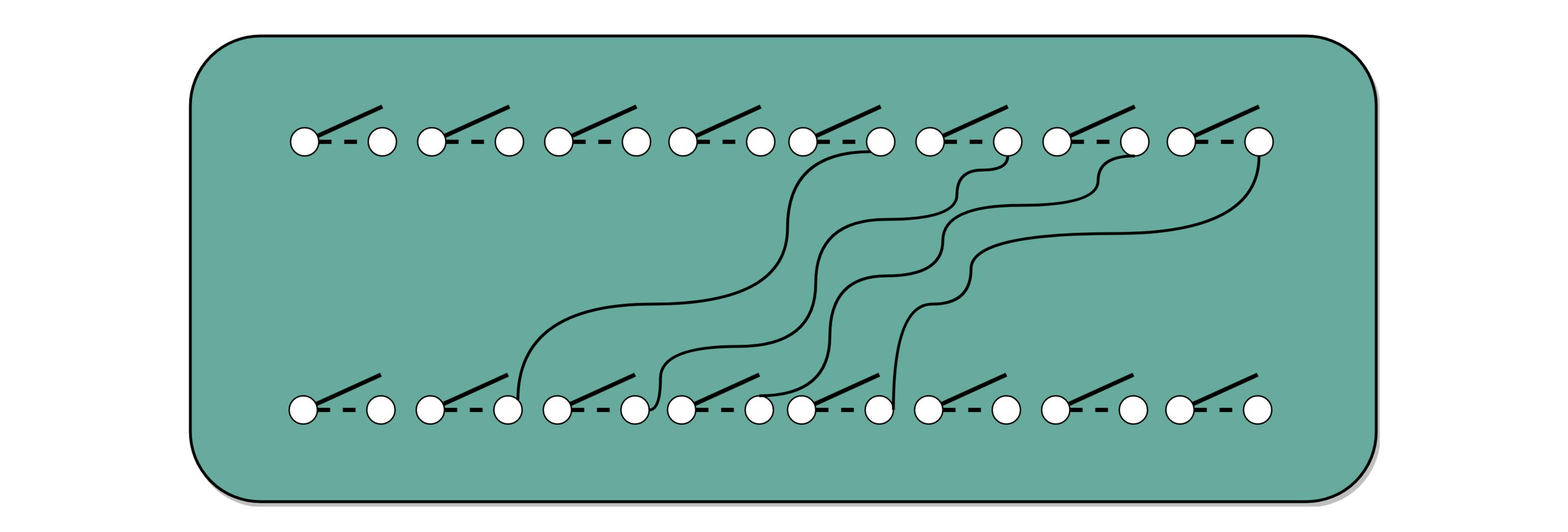

3、把对应的线路错位连接,就可以起到位移的作用

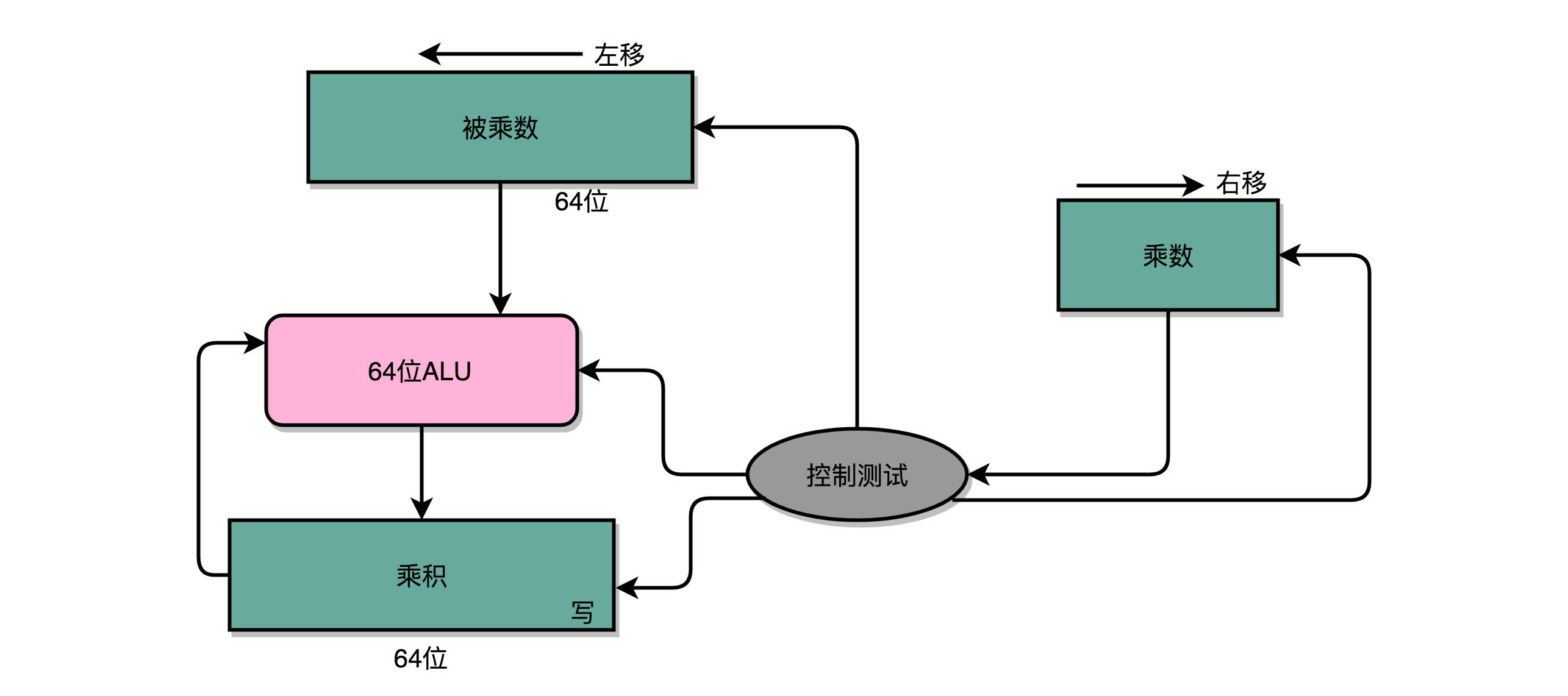

4、乘法器硬件结构示意图

5、虽然节约了开关,但是也有一个很大的缺点,那就是慢

你应该很容易就能发现,在这个乘法器的实现过程中,我们其实就是把乘法展开,变成了“加法+位移” 来实现,我们用的是4位数。所以要进行4组“位移+加法”的操作。而且这4组操作还不能同时进行

因为下一组的加法要依赖上一组的加法后的计算结果,下一组的位移也要依赖上一组的位移的结果这样这个,算法是“顺序”的,每一组加法或者位移的运算都要一定的时间

所以,最终这个乘法的计算速度,恰是和我们要计算的数的位数有关,比如:这里的4位,就需要4次的加法。而我们的现代CPU常常用32位或者是64位来表示整数,

那么对应需要32次或者64次加法,比起4位数,要多花了8倍乃至16倍的时间

二、并行加速方法

换个我们在算法和数据结构中的术语来说就是,这样的一个顺序乘法硬件进行计算的复杂度是O(N),这里的N,就是乘法的数里面的位数

能不能把O(N)降低到O(logN),办法还真的有,和软件开发里面改算法一样,在涉及CPU和电路的时候,我们可以改电路,32位数虽然是32次加法,

但是我们可以让很多加法同时进行,回到这一开始,我们把位移和乘法的计算结果加到中间结果里的方法,32位整数的乘法,其实就编程了32个整数相加

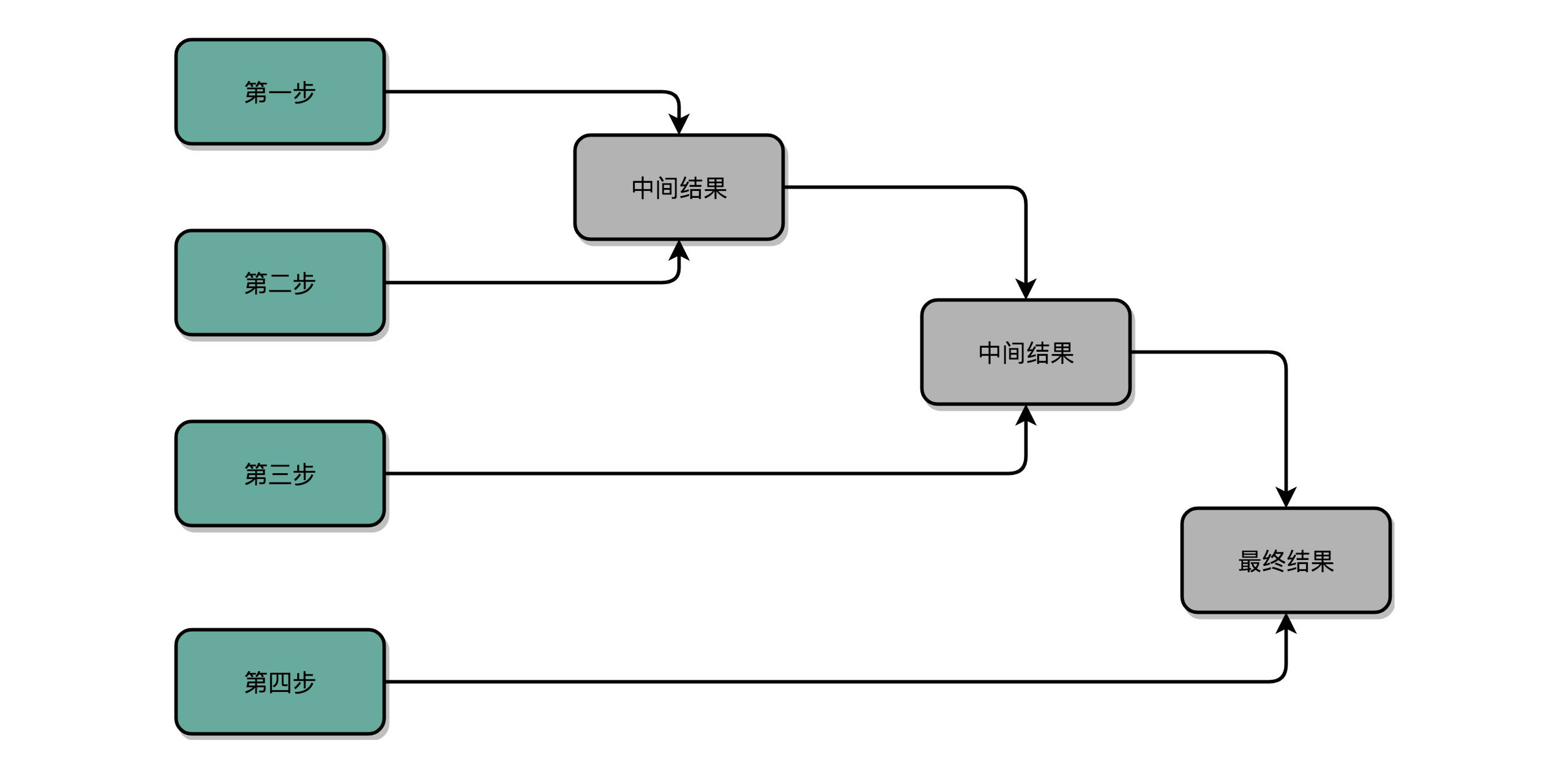

1、单败淘汰赛

2、加速乘法

加速的办法,就是把比赛变成像世界杯足球赛那样的淘汰赛,32个球队捉对厮杀,同时开赛。这样一天一下子就淘汰了 16 支队,也就是说,32 个数两两相加后,你可以得到 16 个结果。

后面的比赛也是一样同时开赛捉对厮杀。只需要 5 天,也就是 O(log2N) 的时间,就能得到计算的结果。

但是这种方式要求我们得有 16 个球场。因为在淘汰赛的第一轮,我们需要 16 场比赛同时进行。对应到我们 CPU 的硬件上,就是需要更多的晶体管开关、来放下中间计算结果

通过并联更多的ALU,加上更多的寄存器,我们也能加速乘法

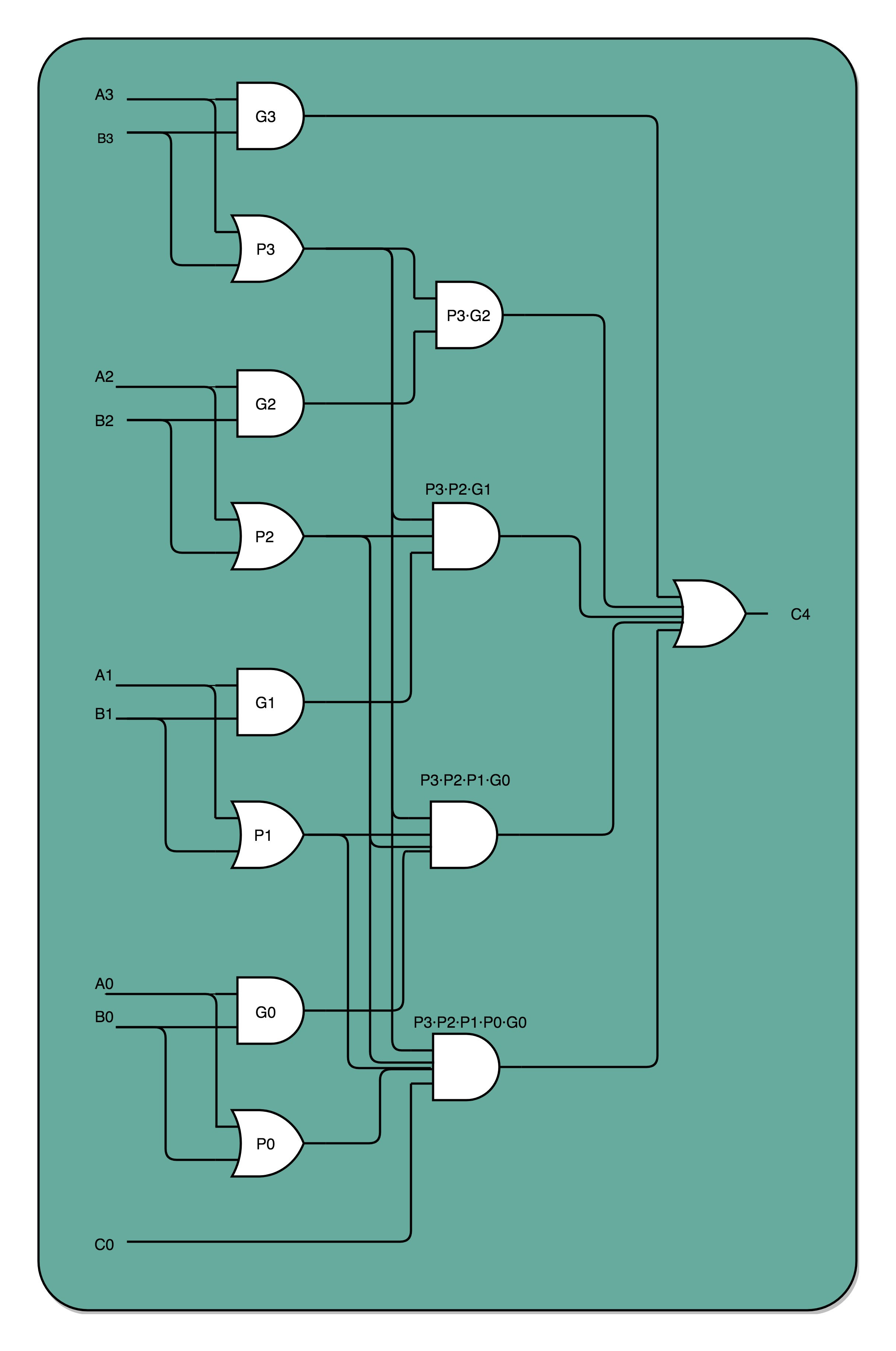

三、电路并行

1、并行加速慢的原因

并行加速,之所以会慢,核心原因其实在“顺序”计算,也就是,都要等前面的计算完成之后,我们才能得到后面的计算结果

2、并行加速慢的典型案例

最典型的例子就是我们上一讲讲的加法器。每一个全加器,都要等待待上一个全加器,把对应的进入输入结果算出来,才能算下一位的输出。位数越多,越往高位走,

等待前面的步骤就越多,这个等待的时间有个专门的名词,叫作门延迟(Gate Delay)

3、门延迟

把电路变复杂解决了延迟的问题

4、时钟频率

除了们延迟之外,还有一个问题就是时钟频率,在上面的顺序乘法计算里面,如果我们想要用更少的电路,计算的中间结果需要保存在寄存器里面,然后等待

下一个时钟周期的到来,控制测试信号才能进行下一次移为和加法,这个延迟比上面的们延迟更可观

这个优化,本质上是利用了电路天然的并行性,电路只要接通,输入的信号自动传播到了所有接通的线路里面,这其实也是硬件和软件最大的不同

无论是这里把对应的门电路逻辑进行完全展开以减少门延迟,还是上面的乘法通过并行计算多个位的乘法,都是把我们完成一个计算的电路变复杂了,也就是意味着晶体管变多了

之前很多同学在我们讨论计算机的性能问题的时候,都提到,为什么晶体管的数量增加可以优化计算机的计算性能,实际上,这里的门电路展开和上面的并行计算乘法都是很好的例子,我们通过更多的晶体

管,就可以拿到更低的门延迟,以及用更少的时钟周期完成一个计算指令

四、总结延伸

讲到这里,我相信你已经发现没我们通过之前两讲的ALU和门电路,搭建出来了乘法器,如果愿意的话,我们可以把很多在生活中不得不顺序执行的事情,

通过简单地连结一下线路,就变成并行执行,这是因为,硬件电路有一个很大的特点,那就是信号都是实时传输的

我们也看到了,通过精巧地设计电路,用较少的门电路和寄存器,就能够计算弯沉过程发这样相对复杂的运算,是用更少更简单的电路,但是需要更长的门延迟和时钟周期

;还是用更复杂的电路,但是更短的门延迟和时钟周期来计算一个复杂的指令,这之间的权衡,其实就是计算机体系结构中的RISC和CISC的经典历史线路之争

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 10年+ .NET Coder 心语,封装的思维:从隐藏、稳定开始理解其本质意义

· .NET Core 中如何实现缓存的预热?

· 从 HTTP 原因短语缺失研究 HTTP/2 和 HTTP/3 的设计差异

· AI与.NET技术实操系列:向量存储与相似性搜索在 .NET 中的实现

· 基于Microsoft.Extensions.AI核心库实现RAG应用

· TypeScript + Deepseek 打造卜卦网站:技术与玄学的结合

· 阿里巴巴 QwQ-32B真的超越了 DeepSeek R-1吗?

· 【译】Visual Studio 中新的强大生产力特性

· 10年+ .NET Coder 心语 ── 封装的思维:从隐藏、稳定开始理解其本质意义

· 【设计模式】告别冗长if-else语句:使用策略模式优化代码结构