Verilog单周期CPU(未完待续)

单周期CPU:指令周期=CPU周期

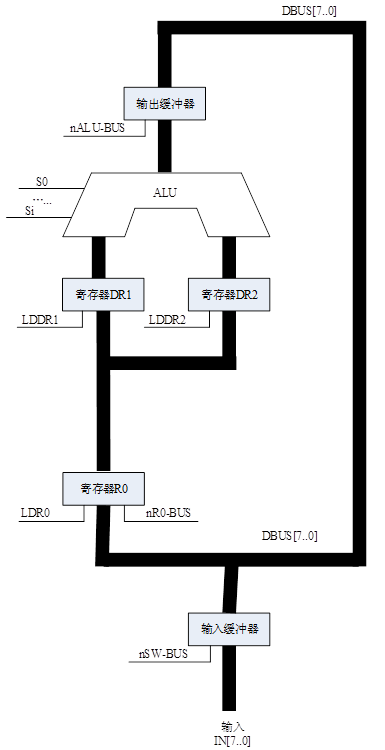

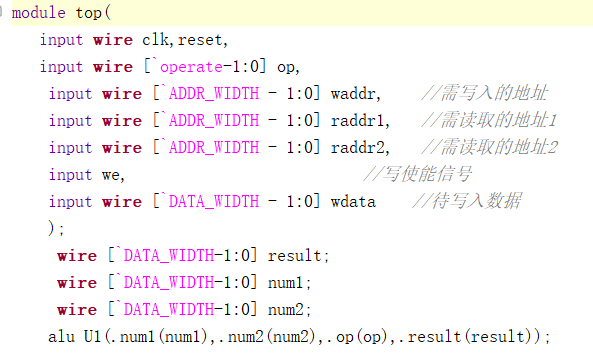

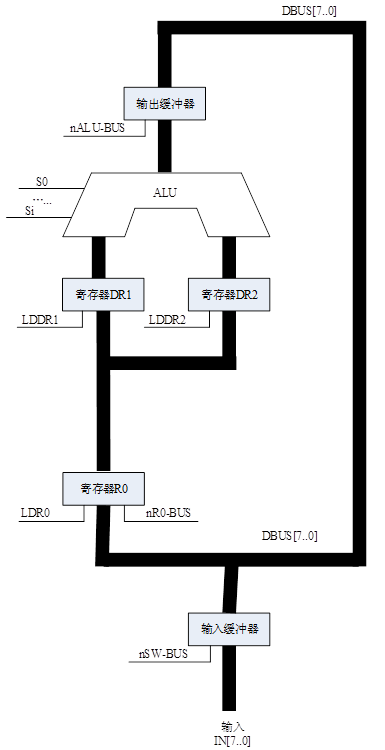

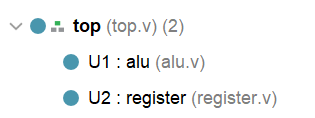

Top模块作为数据通路

运算器中有ALU,通路寄存器(R1、R2、R3、R4),数据缓冲寄存器(鉴于书上的运算器只有R0)。..........

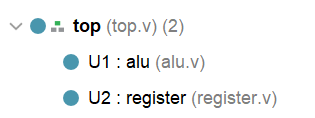

此为ALU和通用寄存器的模块,(注意:当各个模块进行仿真时应该将其模块set as top,当进行数据通路时则如图,此图缺少数据输入缓冲寄存器)

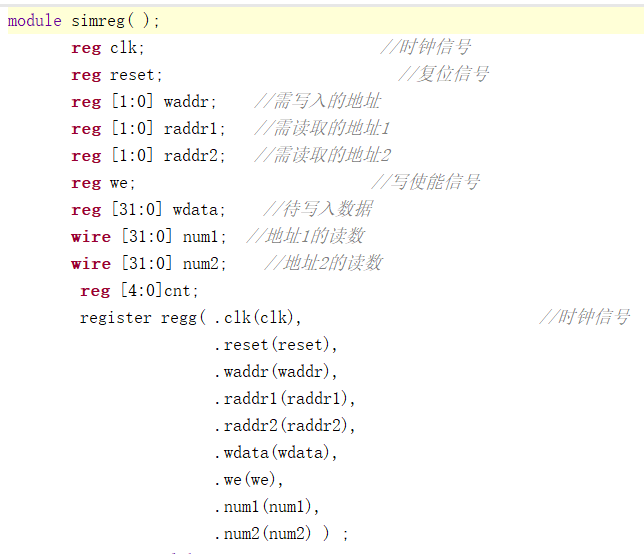

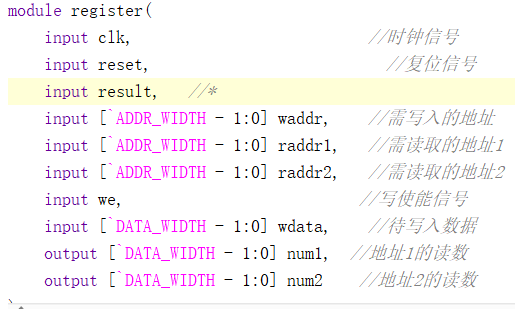

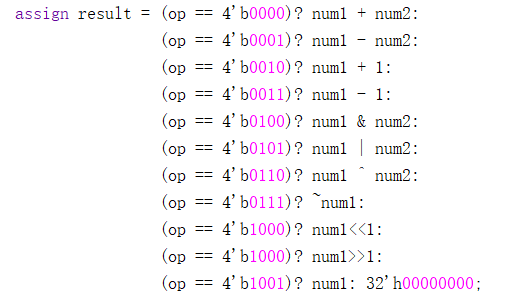

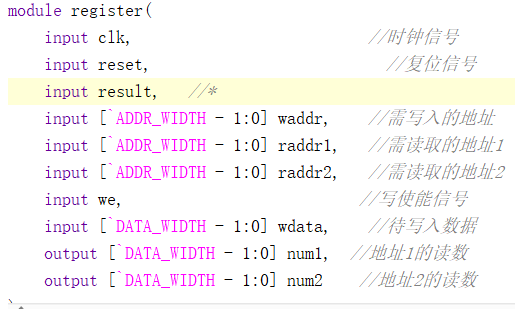

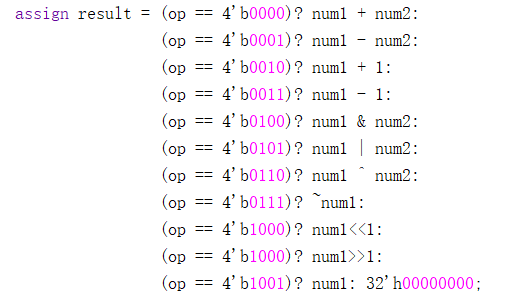

部分代码如下

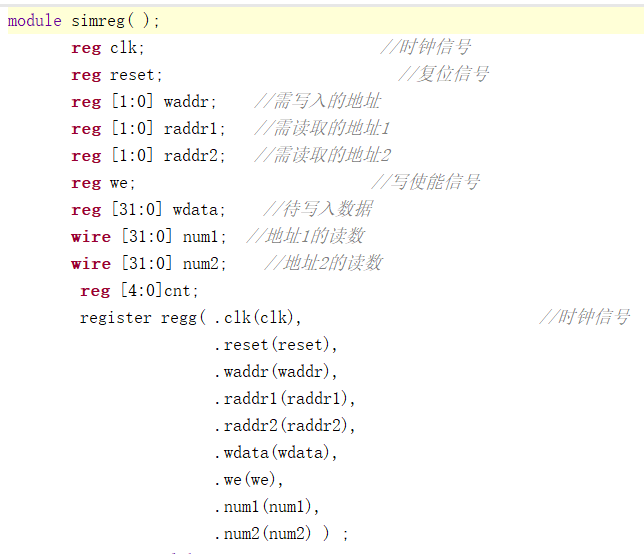

对不通发模块进行仿真后,对top仿真

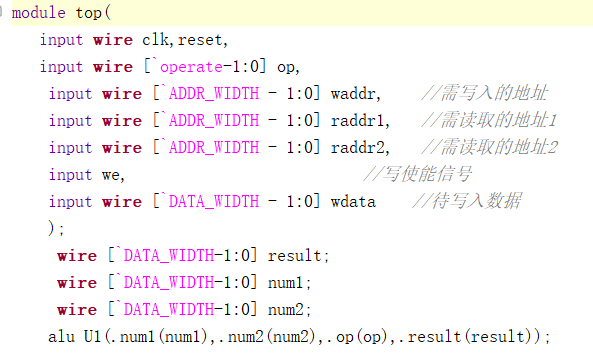

部分代码

单周期CPU:指令周期=CPU周期

Top模块作为数据通路

运算器中有ALU,通路寄存器(R1、R2、R3、R4),数据缓冲寄存器(鉴于书上的运算器只有R0)。..........

此为ALU和通用寄存器的模块,(注意:当各个模块进行仿真时应该将其模块set as top,当进行数据通路时则如图,此图缺少数据输入缓冲寄存器)

部分代码如下

对不通发模块进行仿真后,对top仿真

部分代码