FPGA实现IP核之PLL实验

PLL的英文全称是Phase Locked Loop,即锁相环,是一种反馈控制电路。

PLL对时钟网络进行系统级的时钟管理和偏移控制,具有时钟倍频、分频、相位偏移和可编程占空比的功能。

对于一个简单的设计来说,FPGA整个系统使用一个时钟或者通过编写代码的方式对时钟进行分频是可以完成的,但是对于稍微复杂一点的系统来说,系统中往往需要使用多个时钟和时钟相位的偏移,且通过编写代码输出的时钟无法实现时钟的倍频,因此学习Altera PLL IP核的使用方法是我们学习FPGA的一个重要内容。

本实验我们将通过一个简单的例程来向大家介绍一下PLL IP核的使用方法。

1. PLL IP核简介

锁相环作为一种反馈控制电路,其特点是利用外部输入的参考信号控制环路内部震荡信号的频率和相位。

因为锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

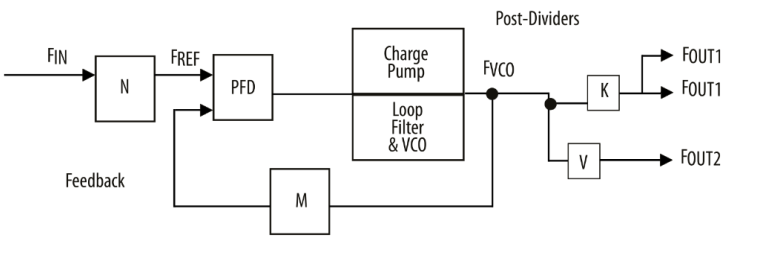

PLL的结构图如下图所示。

PLL结构图

PLL由以下几部分组成:

前置分频计数器(N计数器)、相位-频率检测器(PFD,Phase-Frequency Detector)电路,电荷泵(Charge Pump)、环路滤波器(Loop Filter)、压控振荡器(VCO,Voltage Controlled Oscillator)、反馈乘法器计数器(M计数器)和后置分频计数器(K和V计数器)。

在工作时,PFD检测其参考频率(FREF)和反馈信号(Feedback)之间的相位差和频率差,控制电荷泵和环路滤波器将相位差转换为控制电压;

VCO根据不同的控制电压产生不同的震荡频率,从而影响Feedback信号的相位和频率。

在FREF和Feedback信号具有相同的相位和频率之后,就认为PLL处于锁相的状态。

在反馈路径中插入M计数器会使VCO的震荡频率是FREF信号频率的M倍,FREF信号等于输入时钟(FIN)除以预缩放计数器(N)。

参考频率用以下方程描述:FREF=FIN/N,VCO输出频率为FVCO=FIN*M/N,PLL的输出频率为FOUT=(FIN*M)/(N*K)。

我们开发板上的FPGA芯片型号为EP4CE6,内部含有2个PLL,为设备提供强大的系统时钟管理以及高速I/0通信的能力。

外部时钟经过锁相环,产生不同频率和不同相位的时钟信号供系统使用。

需要注意的是,PLL的时钟输入可以来自于时钟专用输入引脚,FPGA内部产生的信号不能驱动PLL。

Altera提供了用于实现PLL功能的IP核ALTPLL,在这里我们需要说明的是,有关ALTPLL的工作原理和ALTPLL的组成结构,我们就不在进一步进行讲解了,我们主要讲解的是如何使用ALTPLL IP核,对ALTPLL的工作原理和ALTPLL的组成结构感兴趣的朋友,可

以参考A1tera提供的ALTPLL IP核的用户手册。

2. 实验任务

本实验任务是使用FPGA开发板输出4个不同时钟频率或相位的时钟,并通过Modelsim软件对ALTPLL IP核进行仿真,来向大家详细介绍一下ALTPLL IP核的使用方法。

3. 硬件设计

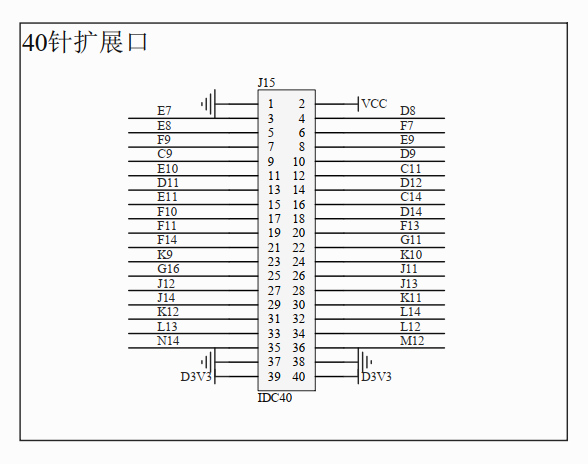

本实验将ALTPLL IP核产生的四个时钟输出到FPGA的扩展口IO上,也就是开发板J15扩展口的第31、32、33和第34脚。

扩展口原理图如下图所示:

扩展口原理图

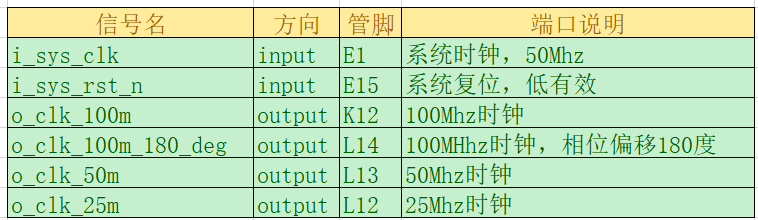

本实验中,各端口信号的管脚分配如下表所示。

4. 程序设计

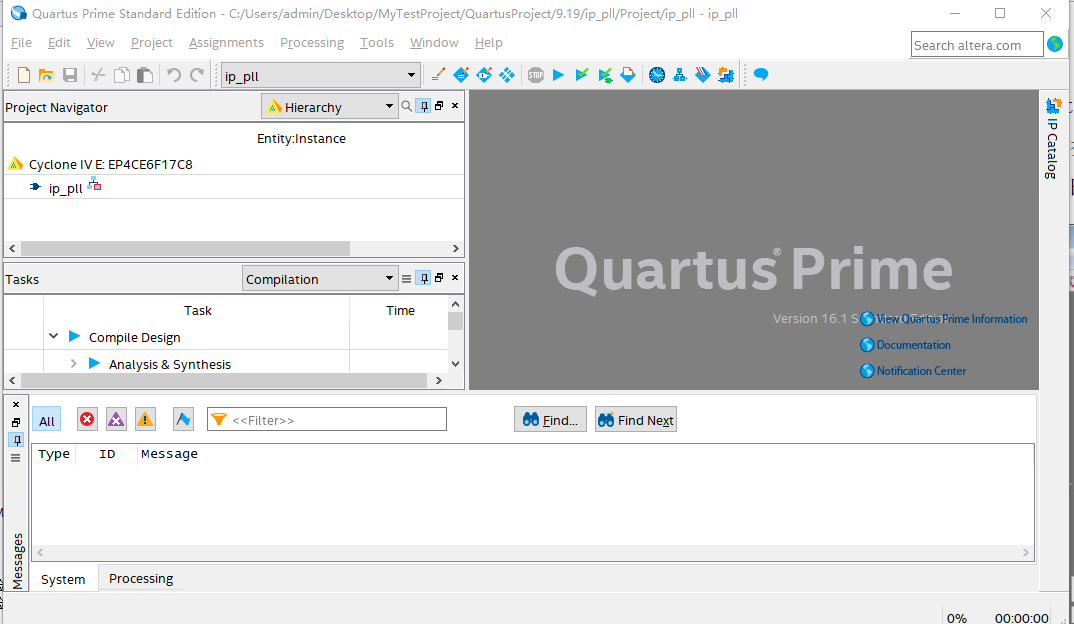

首先创建一个名为ip_p11的工程,在这里我们就不再给出Quartus Prime Standard Edition软件创建工程的详细过程,如果大家对QuartusII软件的创建过程还不熟悉的话,可以百度。新建后的工程如下图所示:

创建好了工程以后,接下来我们创建PLL IP核。

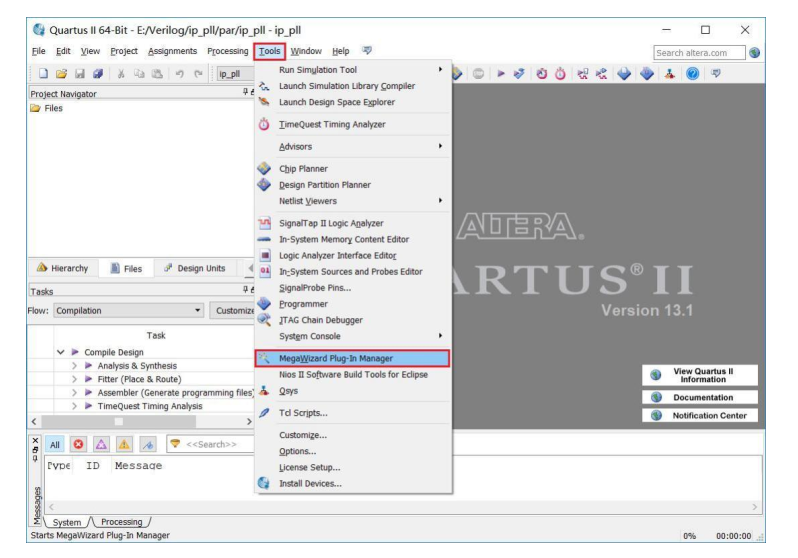

我们在QuartusII软件的菜单栏中找到【Tools】->【MegaWizard Plug-In Manager】按钮并点击打开,Too1工具栏打开页面及打开后弹出的页面如下图所示。

工具栏打开IP核页面

代码

1 /*********************************************************************** 2 Filename : ip_pll.v 3 Author : 4 Company : 5 Mail : 6 Device : Altera 7 Enviroment : Win10,Quartus16.1,modelsim 10.4 8 Created date : 9 Version : V1.0 10 Description : 11 Sim : 12 Modified by : 13 Modified date: 14 Version : 15 Description : 16 ************************************************************************/ 17 module ip_pll ( 18 input i_sys_clk, /* 系统时钟信号50MHz */ 19 input i_sys_rst_n, /* 系统复位信号 */ 20 output o_clk_100m, /* 100Mhz时钟频率 */ 21 output o_clk_100m_180deg,/* 100Mhz时钟频率,相位偏移180度 */ 22 output o_clk_50m, /* 50Mhz时钟频率 */ 23 output o_clk_25m /* 25Mhz时钟频率 */ 24 ); 25 wire w_rst_n;/* 复位信号 */ 26 wire w_locked;/* locked信号拉高,锁相环开始稳定输出时钟 */ 27 assign w_rst_n = i_sys_rst_n & w_locked;/* 系统复位与锁相环locked相与,作为其他模块的复位信号 */ 28 /* 例化锁相环模块 */ 29 pll_clk u_pll_clk ( 30 .areset (~i_sys_rst_n)/* 锁相环高电平复位,所以复位信号取反 */ 31 .inclk0 (i_sys_clk), 32 .c0 (o_clk_100m), 33 .c1 (o_clk_100m_180deg), 34 .c2 (o_clk_50m), 35 .c3 (o_clk_25m), 36 .locked (w_locked) 37 ); 38 endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号