RS触发器

RS触发器

来源 http://www.elecfans.com/book/story.php?id=621

参考 http://www.elecfans.com/book/1/shuzidianzijishu-17.html

SR Latch

A latch (also called a flip-flop) is a fundamental component of data storage. A single latch can hold 1-bit of data, increase that number by many orders of magnitude and you can create kilo-, mega-, giga-, even tera-bytes of memory. Of course, like most digital circuits, latches are made out of digital logic gates!

There are many different kinds of latches, all with somewhat cryptic names like SR, D, JK, and T. The SR-latch we'll be experimenting with is one of the most fundamental forms of a latch.

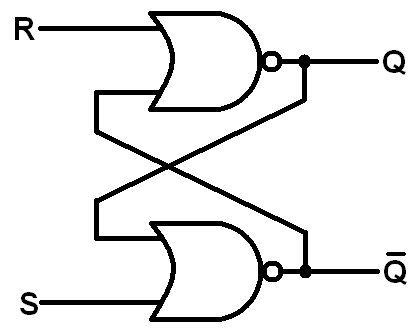

There are a few ways to make an SR latch. Here’s an example of a NOR SR latch:

Notice the feedback? This is another sequential logic circuit. The two NOR gates each have their output flow into the input of the other. There are two controllable inputs: reset (R) and set (S), which produce the two outputs: Q and Q' ("Q-not"). That's where the SR latch get's its name -- it's a set/reset latch.

The SR latch comes with a rule, which cannot ever be broken: Q' must always be the opposite of Q. These outputs are called complements. In our application Q is the only output we really care about -- that's where the latch's data is usually stored and retreived -- but it's important to observe that the two outputs are opposites.

An SR latch is so important it even gets its very own circuit symbol:

Here is the state table, which is a bit wonky. Because the circuit is sequential, the current value of Q depends on its previous state:

| S | R | Previous Q | Current Q | Current Q' |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 (no change) | 1 |

| 0 | 0 | 1 | 1 (no change) | 0 |

| 0 | 1 | 0 | 0 (no change) | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 1 (no change) | 0 |

| 1 | 1 | 0 | 0 (Restricted, Q and Q' would not be complements) | 0 |

| 1 | 1 | 1 | 0 (Restricted, Q and Q' would not be complements) | 0 |

Put into words, the output, Q, can be in any of the following states:

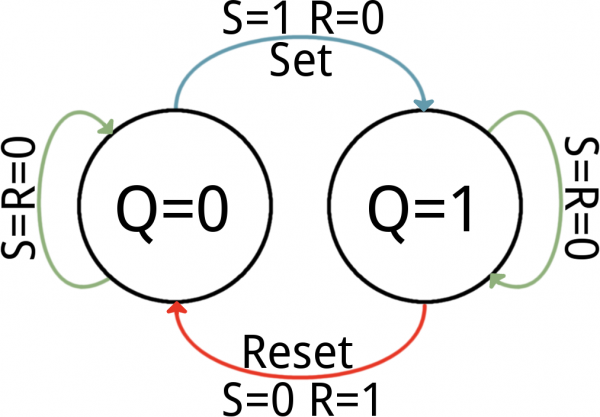

- Steady: When S and R are both 0, then Q remains steady. It keeps the value it had before. If it was 0 it'll remain 0, if it was 1 it will still be 1.

- Set: Changing S to 1 has the potential to "set" the output of Q. If Q was 0, changing S to 1 will change Q to 1 as well. If Q was already 1, making S=1 will have no effect.

- Reset: Moving the R input from 0 to 1 can "reset" Q. As long as Q was 1, setting R to 1 will change Q to 0. If Q was already 0, though, R won't have any effect on it.

- Restricted: When both S and R are 1, we enter restricted territory: our rule that Q and Q' must be complements is broken, as they both go to 0. So we call S=1/R=1 a restricted combination. In most latch circuits precautions are taken to keep those inputs from both being 1. Our LogicBlock circuit isn't quite that smart, so you'll need to take the "circuit safety" precautions into your own hands to make sure they're never both 1 (don't worry, the universe should survive the contradiction if you set both inputs high).

We can also use a state diagram to document the possible states of Q:

在触发器中,最简单的触发器是基本RS触发器,它由两个与-非门(或者两个或-非门)来组成。

图5.2.1(a)是由与-非门构成的基本RS触发器,由图看出,基本RS触发器有两个输入端(![]() 和

和![]() )和两个输出端(

)和两个输出端(![]() 和

和![]() ),门G1和G2的组成有对称性, G1的输出经过G2的传输后回送到G1的另一个输入端,G2的输出经过G1的传输后回送到G2的另一个输入端,正是有了这样的反馈通道才使其具有了存储特性,也有别于前面所讲到的组合逻辑电路。通常将它们的电路结构画成图5.2.1(b)的形式,与

),门G1和G2的组成有对称性, G1的输出经过G2的传输后回送到G1的另一个输入端,G2的输出经过G1的传输后回送到G2的另一个输入端,正是有了这样的反馈通道才使其具有了存储特性,也有别于前面所讲到的组合逻辑电路。通常将它们的电路结构画成图5.2.1(b)的形式,与![]() 相连的输出端称为

相连的输出端称为![]() ,与

,与![]() 相连的输出端称为

相连的输出端称为![]() 。

。

定义输出端的状态:![]() ,

,![]() 时,为触发器的1状态;

时,为触发器的1状态;![]() ,

,![]() ,为触发器的0状态。触发器处与1状态或0状态时输出端都有互补性。下面具体分析两个输入端对输出端的影响情况。

,为触发器的0状态。触发器处与1状态或0状态时输出端都有互补性。下面具体分析两个输入端对输出端的影响情况。

(1)当![]() ,

,![]() 时,

时,![]() ,

,![]() ,触发器为0状态;

,触发器为0状态;

(2)当![]() ,

,![]() 时,

时,![]() ,

,![]() ,触发器为1状态;

,触发器为1状态;

(3)当![]() ,

,![]() 时,触发器两个输出端的值不变,触发器保持为原来的状态;

时,触发器两个输出端的值不变,触发器保持为原来的状态;

(4)当![]() ,

,![]() 时,

时,![]() ,

,![]() ,此时触发器的输出端既不是定义的1状态,也不是定义的0状态,破坏了

,此时触发器的输出端既不是定义的1状态,也不是定义的0状态,破坏了![]() 和

和![]() 的互补特性,实际使用时应该避免这种现象的产生。因为在

的互补特性,实际使用时应该避免这种现象的产生。因为在![]() 和

和![]() 的有效信号同时消失时,即

的有效信号同时消失时,即![]() 和

和![]() 同时从0变到1时,输出端的值不确定。

同时从0变到1时,输出端的值不确定。

下面分析当![]() 和

和![]() 同时从0转变到1时,输出端的情况。假设G1的传输时延小于G2的传输时延,在

同时从0转变到1时,输出端的情况。假设G1的传输时延小于G2的传输时延,在![]() 由0变为1时,即G1的输出先变为0,其值反过来影响到G2的输出,使

由0变为1时,即G1的输出先变为0,其值反过来影响到G2的输出,使![]() 的值仍然保持为1;另一种假设就是G2的传输时延小于G1的传输时延,在

的值仍然保持为1;另一种假设就是G2的传输时延小于G1的传输时延,在![]() 由0变为1时,即G2的输出先变为0,其值反过来影响到G1的输出,使

由0变为1时,即G2的输出先变为0,其值反过来影响到G1的输出,使![]() 的值仍然保持为1。用图5.2.2可以说明在

的值仍然保持为1。用图5.2.2可以说明在![]() 和

和![]() 同时从0变为1时,输出端逻辑值的不确定情况,从图中可以看出,在这种情况下,门电路传输时延小的门电路其输出端的值会发生变化,而门电路传输时延大的门电路逻辑门其输出端的值不会发生变化。

同时从0变为1时,输出端逻辑值的不确定情况,从图中可以看出,在这种情况下,门电路传输时延小的门电路其输出端的值会发生变化,而门电路传输时延大的门电路逻辑门其输出端的值不会发生变化。

由以上分析可知,![]() 和

和![]() 的低电平同时消失时,在门电路传输时延未知的情况下,输出端状态是不确定的。在通常使用RS触发器时,应该避免这种情况的出现,一般不要让

的低电平同时消失时,在门电路传输时延未知的情况下,输出端状态是不确定的。在通常使用RS触发器时,应该避免这种情况的出现,一般不要让![]() 和

和![]() 同时为0。所以,在正常工作的条件下,用式

同时为0。所以,在正常工作的条件下,用式![]() +

+![]() =1来约束两个输入端,称为约束条件。

=1来约束两个输入端,称为约束条件。

在正常工作时,输出端![]() 和

和![]() 具有互补的特性,

具有互补的特性,![]() 是低电平使输出端

是低电平使输出端![]() 为0,

为0,![]() 也是低电平才使输出端

也是低电平才使输出端![]() 为1。所以

为1。所以![]() 是低电平有效置0(

是低电平有效置0(![]() ),置0也称为触发器复位,

),置0也称为触发器复位,![]() 端称为复位端。

端称为复位端。![]() 是低电平有效置1(

是低电平有效置1(![]() ),置1也称为触发器置位,

),置1也称为触发器置位,![]() 端称为置位端。

端称为置位端。

对于RS触发器输入和输出的逻辑关系,可以通过逻辑状态转移真值表来加以描述。如表5.2.1所示,真值表中考虑了触发器在![]() 和

和![]() 信号作用前的输出状态值,即触发器的初态

信号作用前的输出状态值,即触发器的初态![]() ,得到的新的状态记作

,得到的新的状态记作![]() 。

。

表5.2.1可以写成逻辑状态转移表的形式,如表5.2.2的所示,亦称为逻辑状态转移表,还可以将其转换为卡诺图的形式,如图5.2.3所示。卡诺图中的“×”表示约束项,即约束条件![]() +

+![]() =1。

=1。

经过化简卡诺图后得到(5.2.1)式,这就是RS触发器的特性方程(也称为状态方程和或次态方程)。从特性方程中可以看出,输出端新的状态![]() 与前一状态

与前一状态![]() 有关,这是组合逻辑电路所不具有的特点。

有关,这是组合逻辑电路所不具有的特点。

图5.2.4为与-非门RS触发器状态转换图,图中“×”在此表示任意项,它用图形的方式描述了触发器状态间的转换情况。图5.2.5为与-非门RS触发器的逻辑符号。

例5.2.1 用与-非门组成的RS触发器中,已知输入端的波形如图5.2.6所示,试画出输出端![]() 和

和![]() 的电压波形图。

的电压波形图。

解: 在用与-非门组成的RS触发器中,输入端是低电平有效复位和置位,根据这一特性可以画出其输出波形。在图中必须注意![]() 和

和![]() 端同时出现了低电平,但是其低电平值不是同时消失的,所以输出端的值是可以确定的。

端同时出现了低电平,但是其低电平值不是同时消失的,所以输出端的值是可以确定的。

用或-非门也可以组成RS触发器,其电路结构和逻辑符号见图5.2.7(a)、(b),与前面与-非门组成的RS触发器相比,其输入端是高电平有效复位和置位。如果RS同时从高电平变到低电平时,输出的状态

是不确定的,所以其相应的约束条件为:RDSD=0。图5.2.7(c)是其卡诺图,利用约束条件化简得其特性方程为(5.2.2)式。

![]() (5.2.2)

(5.2.2)

5.2.2 时钟控制RS触发器

基本的RS触发器结构简单,但其功能单一,在较复杂的数字逻辑系统中可能要用到很多的触发器,如此多的逻辑器件要能够有条不紊的工作,应该有一个统一的指挥,这就是时钟脉冲,将时钟脉冲应用到基本RS触发器中,即为钟控RS触发器(也称为同步RS触发器)。其电路的结构形式如图5.2.8(a)所示,图5.2.8(b)为其逻辑符号。

从图5.2.8可以看出,其电路结构的变化在于将RS端和时钟信号相与,门G1和G2组成控制电路,结果送入与-非门组成的基本RS触发器,下面分析其工作原理。

(1)当钟控信号CP =0时,G3和G4被封锁,其输出端均为1,则![]() ,

,![]() ,触发器两个输出端的值不变,触发器保持为原来的状态,即:

,触发器两个输出端的值不变,触发器保持为原来的状态,即:![]() 。

。

(2)当钟控信号CP =1时,G3和G4的输出端的值取决于R、S端的值,则![]() ,

,![]() ,触发器的状态可以发生变化。输入端的取值情况与输出的关系为

,触发器的状态可以发生变化。输入端的取值情况与输出的关系为

(ⅰ) 当![]() ,

,![]() 时,

时, ![]() ,

,![]() ,触发器为1状态;

,触发器为1状态;

(ⅱ) 当![]() ,

,![]() 时,

时, ![]() ,

,![]() ,触发器为0状态;

,触发器为0状态;

(ⅲ) 当![]() ,

,![]() 时,

时,![]() ,

,![]() ,此时

,此时![]() 和

和![]() 不具有互补特性,而且R和S的高电平同时消失时,

不具有互补特性,而且R和S的高电平同时消失时,![]() 和

和![]() 状态不定,实际使用时应该避免这种输入。

状态不定,实际使用时应该避免这种输入。

(ⅳ) 当![]() ,

,![]() 时,触发器两个输出端的值不变,触发器保持为原来的状态。

时,触发器两个输出端的值不变,触发器保持为原来的状态。

根据以上分析可知,在CP =1时,输入端的有效电平为高电平,此时钟控RS触发器的逻辑状态的变化与用或-非门组成的RS触发器相同。所以其特性方程可以总结为

![]() (5.2.3)

(5.2.3)

从式(5.2.3)出发,可以画出钟控信号为1期间,输出端的逻辑状态的转换关系,即图5.2.9所示的状态转换图。

例5.2.2 对于图5.2.8所示的钟控RS触发器,其输入端的信号波形如图5.2.10所示,试画出输出端![]() 和

和![]() 的波形。

的波形。

解: 图5.2.8所示的钟控RS触发器,在时钟信号CP =1时,输出端的状态可以发生变化,在CP =0时,输出端的状态不变。其R、S端是高电平有效复位和置位,输出端的波形图如图5.2.10所示。

5.2.3 主从RS触发器

在钟控RS触发器中,时钟信号CP =0期间,输出端的值不会发生变化,而在CP =1期间,输出端的状态可以发生变化,其状态与R、S端的值有关,如果R、S的值发生多次变化,则输出端的值也会发生多次变化,例题5.2.2已经说明了这一点。因此,为了提高触发器的工作的可靠性,让时钟信号作用的一个周期里,输出端的

值只能变化一次,主从触发器可实现这一功能。下面分析主从结构的RS触发器工作原理。

主从RS触发器的电路结构如图5.2.11所示。电路中由两个钟控RS触发器组成,从触发器的时钟端通过非门和主触发器的时钟端相连,作为总的时钟端;主触发器的R、S端作为整个主从结构RS触发器的输入端;从触发器的输出端作为整个主从结构RS触发器的输出端,即![]() 和

和![]() 。

。

(1)当时钟信号CP =1时,主触发器对应的时钟端为1,处于工作状态,其输出端![]() 和

和![]() 的值与输入端RS的值有关。此时从触发器的时钟端为0,处于封锁状态,其输出端

的值与输入端RS的值有关。此时从触发器的时钟端为0,处于封锁状态,其输出端![]() 和

和![]() 的状态不会发生变化。

的状态不会发生变化。

(2)当时钟信号CP =0时,主触发器对应的时钟端为0,处于封锁状态,其输出端的![]() 和

和![]() 的状态不会发生变化。此时从触发器的时钟端为1,处于工作状态,输出端

的状态不会发生变化。此时从触发器的时钟端为1,处于工作状态,输出端![]() 和

和![]() 的值与主触发器输出端

的值与主触发器输出端![]() 和

和![]() 有关。

有关。

如果此时:![]() 、

、![]() ,则

,则![]() 、

、![]() ;

;

![]() 、

、![]() ,则

,则![]() 和

和![]() 。

。

所以在时钟信号CP =0期间,主触发器状态不变,而从触发器接收主触发器的数据,即将主触发器的数据送到了输出端保存下来。钟信号CP的一个周期里,主触发器状态在CP =1期间可以发生多次变化,而从触发器的输出只会变化一次。下面通过例5.2.3来说明主从RS触发器的工作情况。

例5.2.3 在图5.2.11所示的RS触发器中,已知触发器的输出端的初始值为

![]() ,

,![]() ,R、S波形如图5.2.12所示,试画出输出端

,R、S波形如图5.2.12所示,试画出输出端![]() 、

、![]() 和

和![]() 、

、![]() 的电压波形图。

的电压波形图。

解:在主从结构的RS触发器中,时钟信号CP =1时,主触发器的状态可以发生改变,其逻辑值与输入端R、S的值有关。此时主触发器的对应波形如图中的①部分所示,从触发器的波形保持不变。

当时钟信号CP 由1变为0时,从触发器接收主触发器数据,因为此时的![]() 、

、![]() ,所以从触发器的输出端的值为

,所以从触发器的输出端的值为![]() 、

、![]() ,即图中②的前半部分。在CP =0期间,主触发器保持不变。

,即图中②的前半部分。在CP =0期间,主触发器保持不变。

当时钟信号CP 又由0变为1时,主触发器的状态又与此时的R、S值有关,其值可以发生变化,波形为图中②的后半部分。重复前面的分析过程可以得到图5.2.12的波形。

通过分析可以看出,主从结构的RS触发器输出端的值在时钟信号的一个周期里只能改变一次,即在时钟信号由1变为0时(下降沿),接收主触发器的数据,保存在输出端。这种结构的RS触发器,克服了简单钟控RS触发器在时钟信号CP =1时输出端的多次翻转现象。

5.2.4 集成RS触发器

集成基本RS触发器有54/74LS279、CC4043、CC4044。54/74LS279为4RS触发器,图5.2.13是其逻辑电路,其中两个RS触发器的S端具有与运算功能。

CC4043、CC4044为三态4 RS集成器件,逻辑图及其引脚功能图如图5.2.14所示。图5.2.14(a)为CC4043逻辑图,它是由或-非门组成的基本RS触发器,图5.2.14(b)

为CC4044逻辑图,它是由与-非门组成的基本RS触发器,它们都是经传输门输出,因此都具有三态输出功能。CC4043/CC4044是4个基本RS触发器共用一个使能端EN。当EN= 1,传输门TG导通,输出按基本RS触发器特性工作;当EN= 0,传输门TG截止,所有输出端都处于高阻状态。

5.2.5 基本RS触发器的简单应用

利用基本RS触发器的置位和复位功能可以组成很多实际应用电路。下面列举其两个应用。

应用一 根据RS触发器工作原理的分析,可以看出在输入端出现多次的复位信号时,只有第一个复位信号产生作用,在输入端出现多次的置位信号时,只有第一个置位信号产生作用,利用其这一特性,可以应用到机械开关的防抖动电路中,消除机械触点引起的毛刺现象。

在图5.2.15中,普通的机械开关在转换触点时,由触点1到触点2,在输出端

V0可能会产生图中所示的一串窄脉冲(毛刺),对数字系统带来了噪声,引起严重的问题。图5.2.16是利用基本RS触发器组成的消除机械开关抖动的电路。开关由触点1到触点2转换时,在输出端V0不会产生毛刺现象,消除了机械开关的抖动。

应用二 利用RS触发器的两个输出端的功能,还可以组成抢答电路,用于输入端的时间判断。如图5.2.17所示位三输入端的抢答器逻辑电路。

电路中设计有三个输出端A、B、C,三个输出端Y1、Y2、Y3,一个复位控制端RX。正常工作时,首先应该让三个触发器的输出端复位,在RX输入端用低电平脉冲复位,即得![]() ,

,![]() 。

。

当输入端没有按键(没有高电平出现)时,即输入端X1=X2=X3=0,RS触发器输入端的值全为1,输出端的值保持不变,电路处于等待状态。

假设A输入端最先出现高电平(对应的按键先按下),则![]() ,

,![]() ,Y1=1,

,Y1=1,![]() 的反馈信号将使得其他两个RS触发器的S端输入锁定在逻辑值1,输出状态不会发生变化,Y2=0,Y3=0。通过观察输出端Y1、Y2、Y3的逻辑值,出现1的输出端即为最先按键。图5.2.17(b)是其工作的波形图。

的反馈信号将使得其他两个RS触发器的S端输入锁定在逻辑值1,输出状态不会发生变化,Y2=0,Y3=0。通过观察输出端Y1、Y2、Y3的逻辑值,出现1的输出端即为最先按键。图5.2.17(b)是其工作的波形图。

=========== End

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· SQL Server 2025 AI相关能力初探

· Linux系列:如何用 C#调用 C方法造成内存泄露

· AI与.NET技术实操系列(二):开始使用ML.NET

· 记一次.NET内存居高不下排查解决与启示

· 探究高空视频全景AR技术的实现原理

· 阿里最新开源QwQ-32B,效果媲美deepseek-r1满血版,部署成本又又又降低了!

· SQL Server 2025 AI相关能力初探

· AI编程工具终极对决:字节Trae VS Cursor,谁才是开发者新宠?

· 开源Multi-agent AI智能体框架aevatar.ai,欢迎大家贡献代码

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

2020-12-26 设备监控系统

2020-12-26 EVE-NG 社区懒人版

2020-12-26 VyOS和cisco交换机如何配置trunk

2020-12-26 General vs Trunk Mode

2020-12-26 cisco smb sf300-08

2019-12-26 NSIS 7-zip

2018-12-26 java与C++的区别