xilinx和ise的互联仿真

xilinx和ise的互联仿真

欢迎使用 赛灵思编辑器。

1.设置modelsim为ise的默认仿真工具

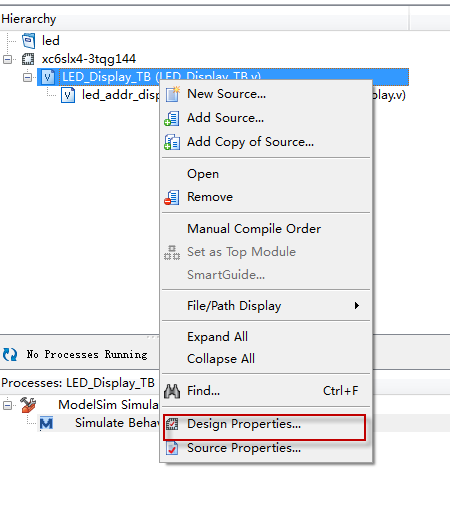

在xilinx的工程中, 点击右键,选择图中红色选框中的选项。

1-1工程选项

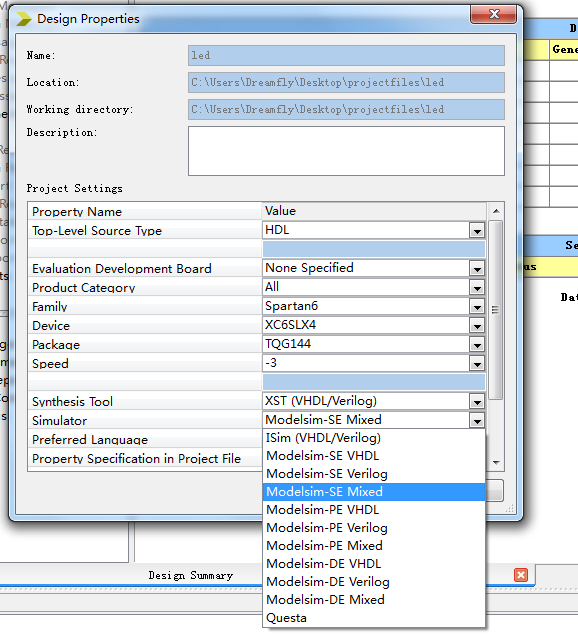

弹出如图1-2对话框

1-2 工程属性

在simulator中选择modelsim-se mixed选项,点击ok,完成设置。

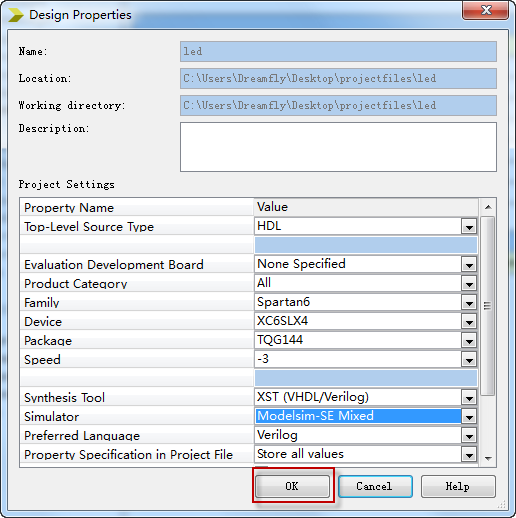

1-3 设置完成

2.设置ISE 调用modelsim路径

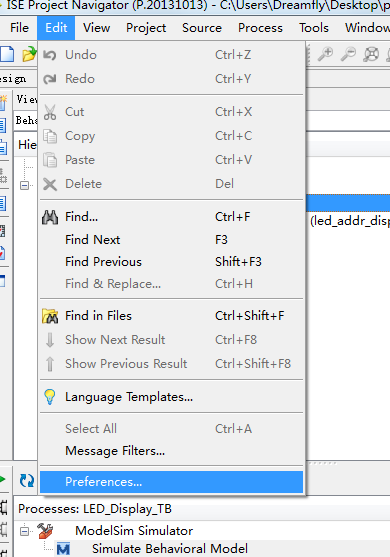

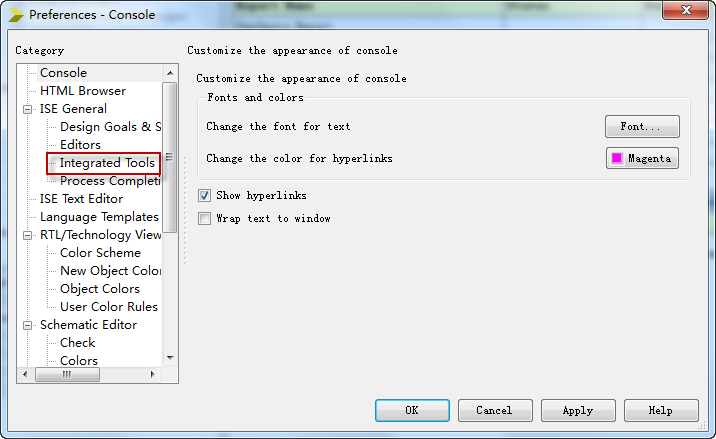

点击edit,preferences。

2-1 设置路径

弹出如图对话框

2-2 设置路径2

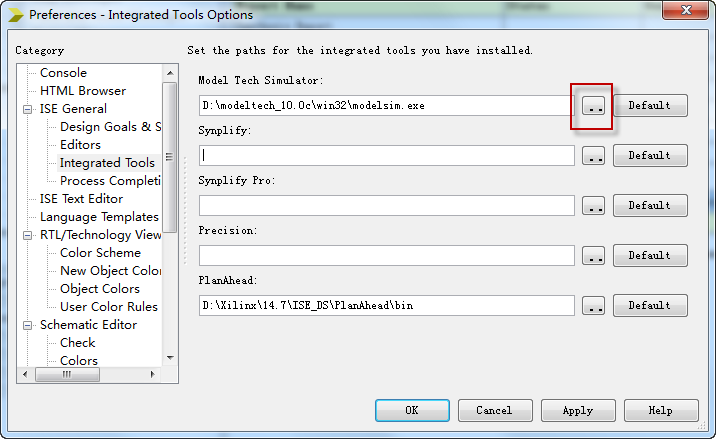

点击integerated tools选项,在model tech simulator选项中点击红色选项框,

2-3 设置路径3

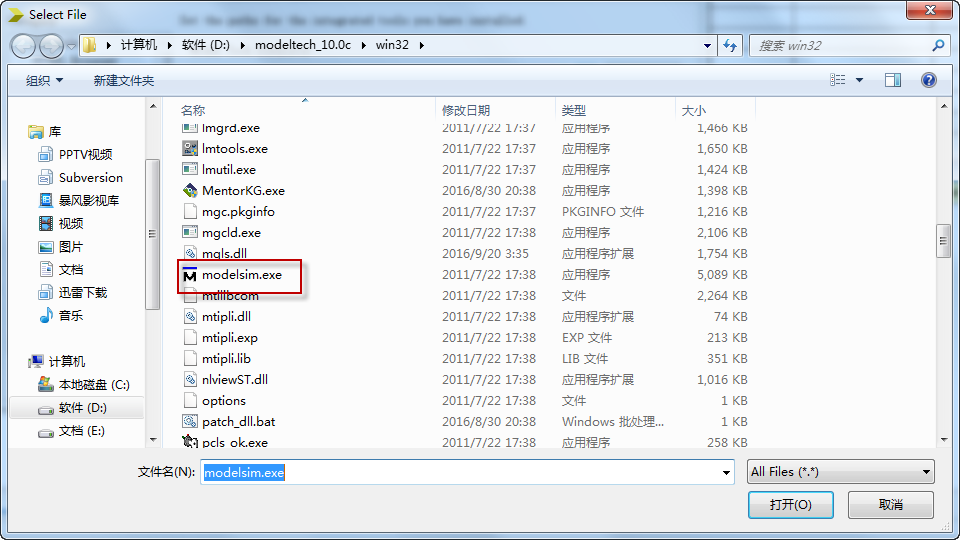

在modelsim的安装目录下找到modelsim.exe文件,双击

2-4 设置路径4

点击ok,设置完成。

3.仿真

下面已led为例,给出verilog源代码以及testbench源码。

-

- `timescale 1ns/1ns

- module led_addr_display

- #(

- parameter LED_WIDTH = 8

- )

- (

- //global clock

- input clk,

- input rst_n,

-

- //user led output

- output reg [LED_WIDTH-1:0] led_data

- );

-

- //-----------------------------------

- //Delay for 0.3s

- //localparam DELAY_TOP = 24'hff_ffff;

- localparam DELAY_TOP = 24'hf; //Just for test

- reg [23:0] delay_cnt;

- always@(posedge clk or negedge rst_n)

- begin

- if(!rst_n)

- delay_cnt <= 0;

- else if(delay_cnt < DELAY_TOP)

- delay_cnt <= delay_cnt + 1'b1;

- else

- delay_cnt <= 0;

- end

- wire delay_done = (delay_cnt == DELAY_TOP) ? 1'b1 : 1'b0;

-

- //-----------------------------------

- always@(posedge clk or negedge rst_n)

- begin

- if(!rst_n)

- led_data <= 0;

- else if(delay_done)

- led_data <= led_data + 1'b1;

- else

- led_data <= led_data;

- end

- endmodule

-

测试代码如下

-

- `timescale 1ns/1ns

- module LED_Display_TB;

-

- //------------------------------------------

- //clock generate module

- reg clk;

- reg rst_n;

- localparam PERIOD = 20; //50MHz

- initial

- begin

- clk = 0;

- forever #(PERIOD/2)

- clk = ~clk;

- end

-

- task task_reset;

- begin

- rst_n = 0;

- repeat(2) @(negedge clk);

- rst_n = 1;

- end

- endtask

-

- //----------------------------------------------

- //the target component instantiation

- //----------------------------

- //led display for addr

- wire [7:0] led_data;

- led_addr_display

- #(

- .LED_WIDTH (8)

- )

- led_addr_display

- (

- //global clock

- .clk (clk),

- .rst_n (rst_n),

-

- //user led output

- .led_data (led_data)

- );

-

-

- //---------------------------------------

- //system initialization

- task task_sysinit;

- begin

-

- end

- endtask

-

- //----------------------------------------

- //testbench of the RTL

- initial

- begin

- task_sysinit;

- task_reset;

- end

-

- endmodule

-

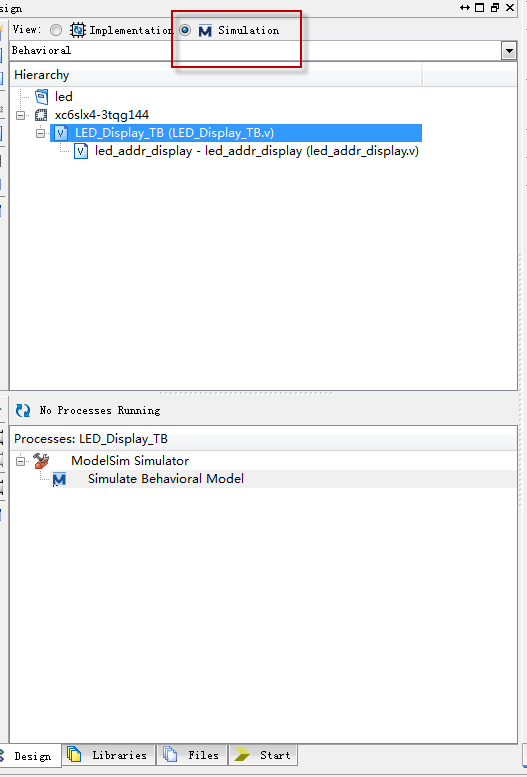

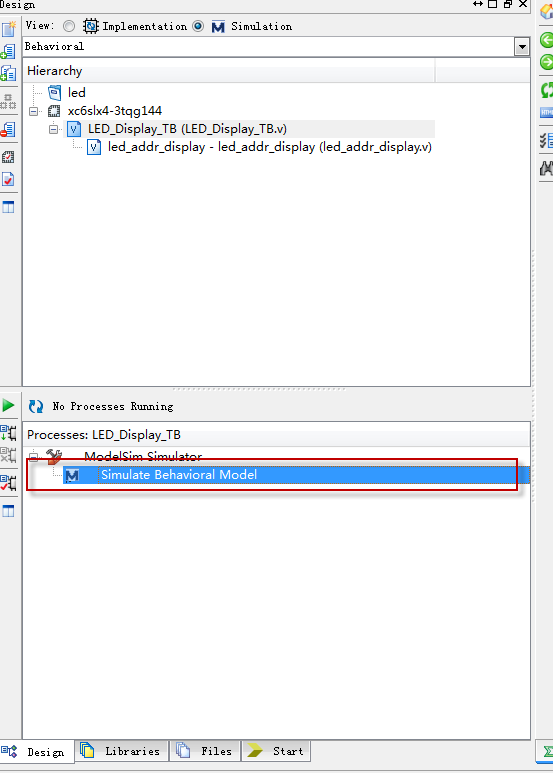

在ise中建立工程,在工程导航中选中红色选框中的选项

3-1 仿真1

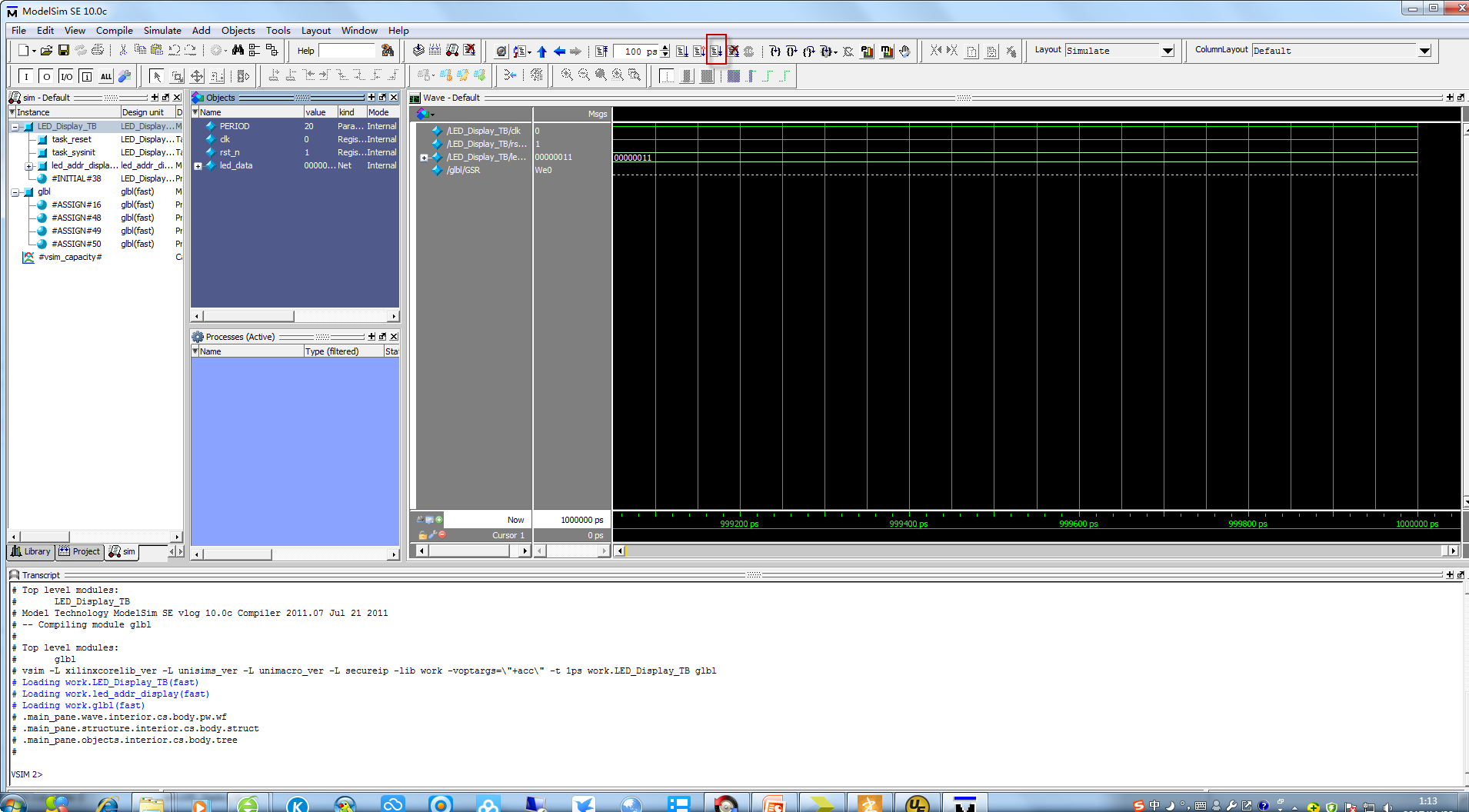

双击下图中的选项

3-2 仿真2

弹出下列选框,点击图中红色框的运行按钮

3-3 仿真3

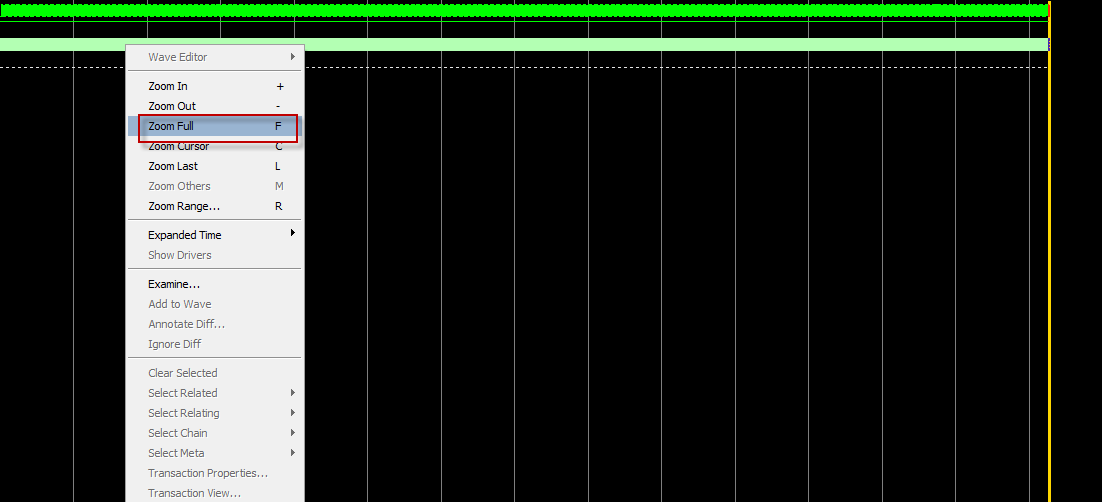

然后等待一会点击stop,在wave视图中点击zoom full

3-4 仿真4

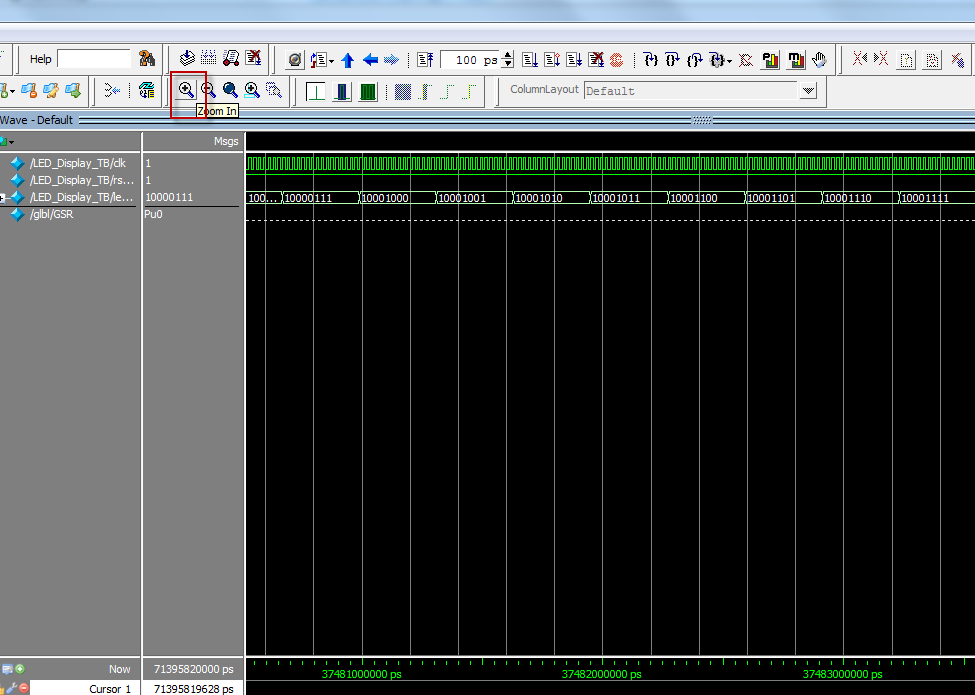

点击图中的放大按钮到合适的视图。

3-5 仿真5

到这,ise关联modelsim的内容结束。谢谢

浙公网安备 33010602011771号

浙公网安备 33010602011771号