计算机频率、内存相关杂谈

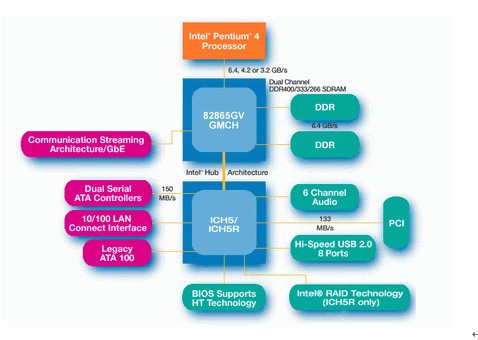

计算机传统架构是分为 北桥和南桥两个芯片组,其中北桥连接着 CPU 、显卡、以及内存等高速设备,南桥则连接着硬盘、 USB 、 PS/2 、 PCI 等等低速设备,不直接与处理器打交道,北桥和南桥之间也是通过 Hub 架构进行连接。如下图:

从图上可以看出,北桥芯片负责和 CPU 通信,并控制内存 ( 仅限于 Intel 除 i7 系列以外的 cpu , AMD 系列 cpu 在 K8 系列以后就在 cpu 中集成了 内存控制器 ,因此 AMD 平台的北桥芯片不控制内存 ) 、显卡数据在北桥内部传输 , 而北桥和 cpu 通信是通过 CPU 的 FSB 前端总线来进行传输的。

内存数据与 cpu 交互是这么一个过程: CPU 发出指令,通过前端总线到达北桥内存控制器,内存控制器再将命令给内存,内存将数据传递给北桥,北桥再通过前端总线传递给 CPU ,注意这个过程, CPU-> 北桥 -> 内存 -> 北桥 ->CPU. 因此 cpu 到北桥,北桥到内存的传输速度要匹配才能达到最佳效果,而北桥因为承载了大量数据的中转运输,发热量可不容小觑。

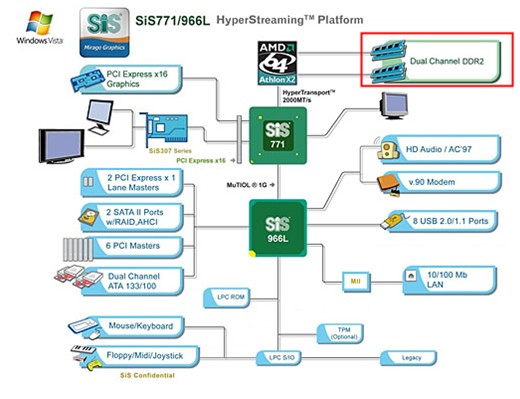

上面说的过程是传统过程,还有一类刚才说的 intel i7 系列以及 AMDK8 系列以后的 CPU 由于在 CPU 内部集成了内存控制器,内存控制器与 cpu 之间几乎没有间距,内存交互与 cpu 交互不再需要北桥参与,内存数据直接交给内存控制器后, cpu 直接取用,比传统方式来讲内存延迟小很多,当然也快捷很多。参考下图:

明白了以上内容之后,后面部分就相对不那么空洞了,接下来再来看一些基本概念,然后我会讲一些与机器性能相关的一些匹配问题:

U(CPU 简称) 的 主频 :cpu 工作时的频率,对于同系列的U 来说,一般是主频越高代表U 的处理速度越快,不同系列的U ,主频只能作为参考,因为整体性能还要考虑U 的指令流水线等等。

U 的外频 :这个频率一般是整个系统的基准工作频率,也称为系统时钟频率,是cpu 与主板之间的同步数据的基准频率,而大多数系统中外频也是内存和主板同步数据的基准频率,因此可以认为是以cpu 的外频与内存在进行数据同步。

U 的倍频 : U 的主频与外频之间存在着一个比值关系,这个比值就是

倍频系数,简称倍频。理论上倍频是从1.5 一直到无限的,但需要注意的是,倍频是以0.5 为一个间隔单位。外频与倍频相乘就是 主频 ,所以其中任何一项提高都可以使CPU 的主频上升,但是有的U 的厂家将某些U 的倍频进行了锁定,例如intel, 因此一般来说都只有提升外频来帮助提高U 的主频。

FSB(intel U 的概念) :全称 Front Side BUS ,前端总线,它是U 和北桥芯片之间传递数据的通道,U 的前端总线频率一般遵从如下公式:FSB 前端总线频率= 外频*4 ,注意只有intel 的U 才有前端总线的概念,FSB 传输速率计算方式是:FSB 传输速率=FSB 总线频率* 总线位宽= 外频*4* 总线位宽,一般FSB 总线位宽是64 位,即U 的外频和位宽越高,表示了这个通道传输能力越强大。

HyperTransport : 超传输技术, 它是一种高速、低延时、点对点的连接,旨在提高电脑、服务器、嵌入式系统,以及网络和电信设备的集成电路之间的通信速度。它的速度比某些现有技术高出48 倍。HyperTransport 有助于减少系统之中的布线数量,从而能够减少系统瓶颈,让当前速度更快的微处理器能够更加有效地在高端多处理器系统中使用系统内存。前面说了cpu 与内存直连,cpu 与北桥直连,北桥和南桥直连,AMD 就采用了这种技术,当然这种技术也是首先由AMD 发明的,HyperTransport 也有他自己的传输频率,HyperTransport 总线频率=CPU 外频*HyperTransport 倍频 , 注意不是CPU 的倍频,因此如果cpu 外频提高,可见,HyperTransport 总线频率也在相应提高。由于HyperTransport 采用类似DDR 的工作方式,即在上升沿和下降沿都传送数据,相当于传送数据能力翻倍,400MH 工作频率相当于800MHZ, 因此其传输速率= 工作频率*2* 位宽,而 HyperTransport 默认位宽是32 位,此外HyperTransport 是在同一个总线中可以模拟出两个独立数据链进行点对点数据双向传输,因此理论上最大传输速率可以视为再翻倍 ,称为双向传输技术,因此考虑到双向传输的话,那么HyperTransport 最大传输速率= 工作频率*2* 位宽*2 ,目前HyperTransport 3.0 标准有1.8GHz 、2.0GHz 、2.4GHz 和2.6GHz 四种物理工作频率,在2.0GHZ 工作频率下,单向传输速度=2.0*2*32/8=16GB/S, 双向传输速度更可以达到32GB/S 。可见传统FSB 传输速度的确没法跟 HyperTransport 比啊。

内存频率:内存的频率其实细分应该分为核心频率、实际时钟频率、等效工作频率。

结合内存分代来讲,内存到目前为止可以分 SDRAM 、 DDR 、 DDR2 、 DDR3 ,我们平时购买内存条的时候就会接触到这些名字 DDR400 、 DDR333 、 DDRII533 、 DDRII667 、 DDRIII1066 等名字。 DDR 后面 I 、 II 、 III 代表的是 DDR 一代、二代、三代内存条, 400 、 533 、 667 、 1066 等表示的内存条的等效工作频率。

可以从上图中看到 DDR2-800 的字样。另外 CL=5 表示列选通延迟时间为 5 个内存时钟周期,具体后面再深入分析。

大家知道计算机系统的时钟频率依靠的是晶体振荡器来产生的,而内存自身并不带振荡器,因此内存自身并没有办法控制自己的频率,它只能限制自己能够运行的最大频率是多少,真正的工作时的频率还是要依赖芯片上的北桥或者主板上的时钟发生器来产生。

先来看下内存工作的两个步骤:内存从 Memory Cell Array( 内存单元对列,内存的一种结构 ) 中读取数据到 Io Buffer 中,等到了一定位数之后再从 Io Buffer 中传送到 cpu 系统进行处理。

于是有了下面的概念:

核心频率 : ( 内部时钟 ) 指内存颗粒工作频率,它是读取数据到 IO Buffer 的频率。

内存外部时钟频率 :这个频率就好理解了,就是将数据从 IO Buffer 传送出去的频率

等效工作频率 :这个就涉及到另外的知识了,先说概念,表示数据等效传输频率,目前 DDR 、 DDR2 、 DDR3 等效工作频率都是外部时钟频率的 2 倍。

先看下面的图:

SDRAM : ( Synchronous Dynamic Random Access Memory )同步动态随机存储器,同步是指 内存工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断的刷新来保证数据不丢失;随机是指数据不是线性依次存储,而是自由指定地址进行数据读写,如上图, SDRAM 核心工作时,每次获取 1bit 数据到 I/Obuffer 中, SDRAM 核心工作频率 = 外部时钟频率,由于 SDRAM 是在外部时钟周期的上升沿传递一次数据,因此等效频率 = 外部时钟频率。

DDR : ( Dual Date Rate SDRAM )双倍速率 SDRAM 的简称, DDR 在 SDRAM 上有了提高,每次核心工作时可以同时预取 2bit 数据到 I/O buffer, 而为了把 I/O buffer 中的 2 位数数据给送出去, DDR 采用了外部时钟周期上升沿和下降沿都传送一位数据,因此很自然我们能知道, DDR 核心频率 = 外部时钟频率,而等效工作频率是外部时钟频率的 2 倍,因此他采用了上升、下降沿都传送一位数据。

DDR2 : 这是第二代 DDR 内存,从上图我们可以看出, DDR2 采用 4 位数据预取技术,即每次核心工作时将同时传递 4 位数据到 I/O buffer 中,而将这 4 位数据要全部传送出去,采用上升沿和下降沿都传递一位数据来看, DDR2 的外部时钟频率必须要是核心频率的两倍才能及时将数据传递出去。因此可以得出这么一个关系: DDR2 等效工作频率是外部时钟频率的两倍 ( 因为采用了上下沿都传递数据 ) ,而外部时钟频率又是核心频率的两倍(为了及时将数据传递出去,否会积压在 buffer 中)

DDR3 : 这是第三代 DDR 内存,同理, DDR3 采用了 8 位数据预取技术,相应的要及时将数据传递出去,外部时钟频率需要时核心工作频率的 4 倍才行,而等效工作频率一样是外部时钟频率的 2 倍(上下沿传递数据)

可见在相同的核心频率下, DDR3 的传输能力要强得多,并且,在得到相同的传输带宽下, DDR3 只需要很小的核心工作频率就可以完成,工作电压也会小很多,发热量也就相应小了很多,好处多多,目前 DDR 内存基本上已经销声匿迹, DDR2 也基本上要被 DDR3 完全淘汰。

那么内存有这么多频率,跟 cpu 外频又有什么关系呢?前面讲到,外频是 cpu 与内存等同步数据的一个频率,因此一般来说内存外部时钟频率应该大于 cpu 外频为好,否则内存将会成为 cpu 运行的一个瓶颈,因为数据供应跟不上。考虑内存和 cpu 搭配,除了考虑频率搭配以外,还要考虑数据带宽搭配,什么意思呢?举个例子

Cpu 外部频率 200MHZ, FSB 800MHZ, 我们可以计算一下, FSB 一般是 64 位,因此 0.8*64/8=6.4GB/S, 考虑频率一致,我们可以采用 DDR 400 、 DDR2-400 、 DDR3-400( 如果有 ), 三种中一种,他们的外部时钟频率都是 200MHZ ,但是带宽呢?由于 DDR 、 DDR2 、 DDR3 位宽一般为 64 位 , 因此, 0.4*64/8=3.2GB/S, 明显数据宽度是个瓶颈,达不到 cpu 要求的数据宽度,于是就出现了双通道技术,双通道技术目的是将内存的数据宽带增加一倍,注意,是数据宽度,而不是频率增加一倍,即,如果再插一根同样类型的内存条,并且你的主板支持双通道技术,那么你的带宽将增加一倍, 64 位可以变成 128 位,即, 0.4*128/8=6.4GB/S ,恰好匹配。

请记住两点:①频率需要匹配②带宽也要匹配 才能不拖 cpu 后腿。

( 其实关于上面两点,网上有很多说法,没有个准,也有说应该是外频要和内存核心频率匹配的,也有说要跟外部时钟频率匹配的, 对于拖 cpu 后腿的说法,有的人认为只要带宽匹配就行了,他们举的例子都是 DDR 内存,由于 DDR 内存核心频率和外部时钟频率一致,因此也完全看不出来是否一定要频率一致,到底以哪个频率一致,经过我看了大概几百多篇文章以及自己试验结果来看,我得出了以上结论 )

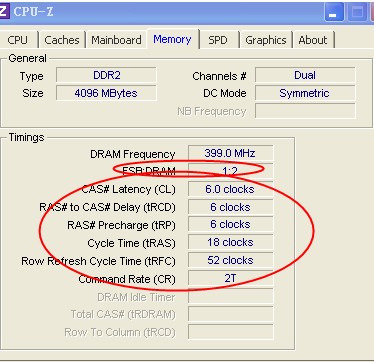

当然,这只是让内存工作再同步模式下,你的内存也可以是 DDR3 -1333 ,此时由于你的内存外部时钟频率是 667MHZ ,明显高于 cpu 外频,系统默认情况一般会设定为内存异步工作模式,即内存频率与外频可以不一致。如果你采用 CPUZ 或者 everest 查看,可以看到 FSB:DRAM=xx:xxxx, 这里 FSB 请不要搞错,由于历史原因,这里只表示外频 ,DRAM 表示内存外部时钟频率。

前面说了 DDR 、 DDR2 、 DDR3 ,也看了他们工作示意图,我们可以从中得出什么来呢?

同样的等效频率 DDR400 、 DDR2-400 , DDR 核心频率 200,ddr2 核心频率 100 ,也就是说 DDR2 核心工作的周期比 DDR 要长。怎么得出来的呢?频率的倒数就是周期。自己计算一下就知道。三类内存他们延迟时间 DDR3>DDR2>DDR 。延迟时间会影响到内存的工作效率,就是同样的 DDR3-800 型号,不同的物理内存,他们制作时也不可能完全一样,总有的体质好的内存条延迟时间可以短点,有的却要长一些,我们应该选用体质较好的内存条,延迟时间短一点,这也是为什么有的内存条上会标注 CL=5 的原因,表示 CL 延迟时间为 5ns.

下面是我从另一处文章中摘抄过来的,是关于内存延迟的很好的描述,我做了少量修饰,文章出处给忘记了,先贴出来,供大家参考:

再来了解一下内存基本结构 和工作流程。目前,每一颗内存芯片内部的存储电路分为 4 块存储阵列(就是 4 个逻辑 Bank, 也就是前面说的 Cell Array )每个存储阵列(逻辑 Bank )的存储单元地址通过 “ 行地址 ” 和 “ 列地址 ” 定位。因此每个存储单元的地址由三部分组成:逻辑 Bank 地址、行地址、列地址。寻址的过程是:先指定逻辑 Bank 地址,再指定行地址,然后指定列地址,这样就能够确定一个存储阵列内的存储单元。

在实际工作中,逻辑 Bank 地址与相应的行地址是同时发出的,这个命令称之为 “ 行有效 ” 或 “ 行激活 ” ( Row Active )。在此之后,将发送列地址寻址命令与具体的操作命令(是读还是写),这两个命令也是同时发出的,所以一般都会以 “ 读 / 写命令 ” 来表示列寻址。

从行有效命令发出到读

/

写命令发出之间有一段时间间隔,这个间隔称之为

tRCD

,即

RAS to CAS Delay

(

RAS

至

CAS

延迟),

RAS

是行地址选通脉冲,

CAS

是列地址选通脉冲

,

所以

tRCD

也可以理解为行选通周期。

tRCD

是

SDRAM

(包括

DDR

)的一个重要时序参数,一般以时钟周期(

tCK

,

Clock Time

)为单位。比如

tRCD=2

,就代表延迟周期为两个时钟周期,具体到确切的时间,则要根据时钟频率而定,对于

DDR400

(时钟频率

=200MHz

)来说,每个周期是

5ns

,

tRCD=2

,就是

10ns

的延迟,对于

DDR333

来说(时钟频率

=166MHz

)

,

每个周期是

6ns

,

tRCD=2

,就是

12ns

的延迟。

当列地址被选中之后,就会触发数据传输,但是从存储单元中输出到数据真正出现在内存芯片的

I/O

接口之间还需要一定的时间(数据触发本身就有延迟,而且还需要进行信号放大),这段时间就是非常著名的

CL

(

CAS Latency

,列地址脉冲选通潜伏期)。

CL

时间长短与芯片硬件设计和制作工艺密切相关,因为这个列地址脉冲选通潜伏期取决于芯片的数据触发电路的延迟和信号放大电路的延迟。所以

JEDEC

就是以

CL

、

tRCD

等参数把

DDR400

分成

A

、

B

、

C

三个等级。

CL

的数值也是以时钟周期表示。常见有

2

、

2.5

、

3

等。相同工作频率的内存芯片,

CL

值不同,实际延迟时间是不一样的。比如

DDR-400

,时钟频率为

200MHz

,时钟周期为

5ns

,那么

CL=2

就意味着

10ns

的潜伏期,

CL=2.5

就意味着

12.5ns

的潜伏期,

CL=3

就意味着

15ns

的潜伏期。因此

CL=3

的

DDR400

其性能不如

CL=2.5

的。如果在

BIOS

里设置了

CL=2.5

,超出心存芯片的的标称性能,如果厂家设定的标称值是接近极限值,没有超频的余地,那么就会导致内存读取数据出错,表现为蓝屏死机。

CL=3

的

DDR400

,当

BIOS

设置为

CL=2.5

时,其频率必须降为

DDR333

(

166MHz

)

,

才可以稳定工作,当频率降为

DDR333

(

166MHz

),每个周期

=6ns

,

2.5

个周期

=15ns,

延迟时间是

15ns

。与

CL=3

时的

DDR400

(

200MHz

)延迟时间相同(

5ns X 3 = 15ns

)。

从上面的分析,可以看出,

CL

和

tRCD

参数值用周期表示,属于相对值,还要乘以实际工作频率才是实际的延迟时间。而实际延迟时间取决于芯片硬件设计的电路制作工艺。

CL

只是针对读取操作,对于

SDRAM

,写入是没有潜伏期的,对于

DDR SDRAM

,写入潜伏期在

0.75

至

1.25

个时针周期之间。

BIOS

里的内存时序参数设置比较专业,所以

JEDEC

规定在内存条加一个

EEPROM

芯片,记录时序参数设置,

BIOS

可以读取这个参数,自动设置。避免用户错误设置。这个纪录时序参数设置的

EEPROM

芯片就叫

SPD

。

我们可以通过看

SPD

信息了解内存条的性能。

这也就说明为什么在双通道时,用

CL=3

的

DDR400

,如果内存条品质(超频)不优秀,导致蓝屏死机,把速度降为

333

就可以解决的原因。

微星

865

主板

BIOS

的内存时序设置里没有

CL=3

的选项,使用

CL=3

的

DDR400

会蓝屏死机。那些有

CL=3

选项的主板也会因为使用

CL=3

的

DDR400

蓝屏死机。我就处理和解决过其他各种品牌主板的这个问题。如果到网上搜索

“

蓝屏死机

DDR400”

,就可以看到很多这一类帖子。各种品牌的主板都有。

下面我们再看看

tRCD

参数,这里小写的

t

是

timing

(时序)的第一个字母,表示时序的意思,

RCD

就是

RAS to CAS Delay

的缩写,其中

RAS

是行地址选通脉冲,

CAS

是列地址选通脉冲,

tRCD

就是行地址选通脉冲到列地址选通脉冲的时间间隔。根据

SDRAM

的工作原理和

JEDEC

标准,

CPU

读写内存时,首先发出从行地址选通脉冲(也叫行有效命令),然后发出列地址选通脉冲(也叫读

/

写命令)。从行有效命令发出到读

/

写命令发出之间有一段时间间隔,

tRCD

就是这个间隔。这个也是由芯片的触发电路的延迟和信号放大电路的延迟决定的,也就是说是硬件本身的特性。

tRCD

一般用时钟周期为单位。比如

tRCD=2

,就代表延迟周期为两个时钟周期,这是相对的。绝对的时间间隔,要根据时钟频率而定。

浙公网安备 33010602011771号

浙公网安备 33010602011771号