verilog注意

wire

wire是一种信号类型,wire 的中文可以翻译为导线,但 Verilog 中的 wire 和现实中的导线不同,wire 应该理解为一个信号。

assign

注意与软件中的赋值操作做区分,Verilog 中的赋值是使用一条带有方向的导线连接了两个信号,所以 left_side 始终等于 right_side,随 right_side 变化而变化。而软件中的赋值是一种事件,某个时刻 left_side 的值变成了和 right_side 相同的值。

assign 描述的是端口之间的连接关系,而不是一次复制右值,赋给左值的复制黏贴,连接关系不存在先后之分。

assign 语句并不是创建 wire ,而是将创建 wire 之间的连接。

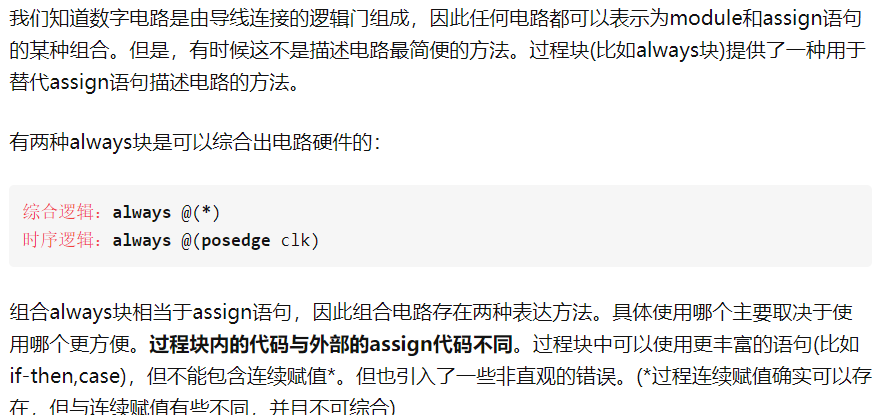

always

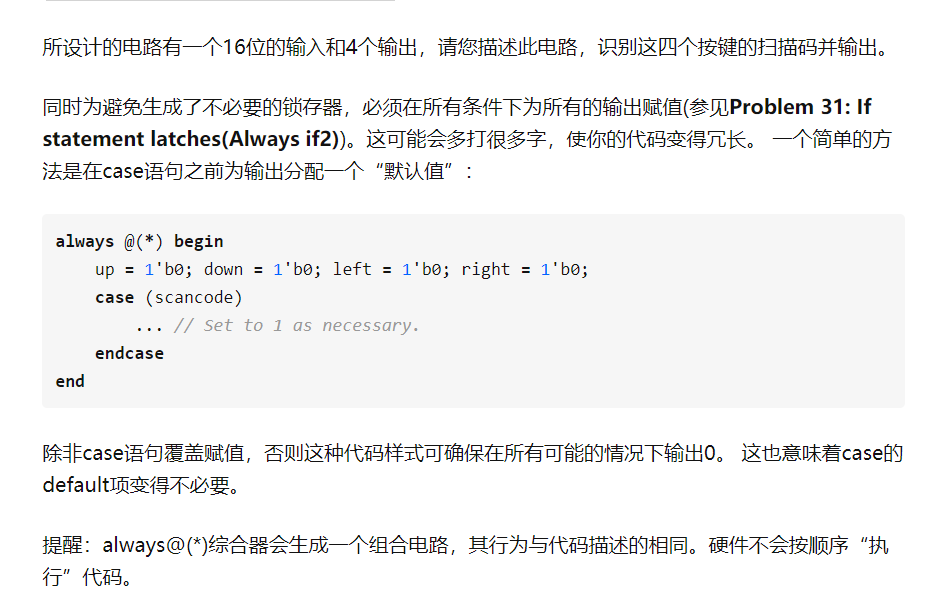

case

如果case语句中的case项与某些输入无关,就可以减少列出的case项。这就是casez的用途:它在比较中将具有值z的位视为无关项(即输入01都会匹配到)。

always @(*) begin casez (in[3:0]) 4'bzzz1: out = 0; // in[3:1]输入什么都可以 4'bzz1z: out = 1; 4'bz1zz: out = 2; 4'b1zzz: out = 3; default: out = 0; endcase end

避免锁存器,同时可以优化代码

NOR(或非门)

assign out = ~(a|b)

XNOR(同或门)

同或门 (XNor Gate) 是异或门 (Nor Gate) 的取反输出。异或门的输入输出可以概括为:(输入)相同(输出)为 0 ,不同为 1 。

assign out = ~ (a^b);