摘要:

@[TOC](静态时序分析) # 一、TCL语言和synopsys TCL语言入门 基本目标: 1.掌握常用TCL基本指令(至少要看得懂) 2.掌握常用synopsys TCL常用指令,包括信息与属性的获取以及过滤 3.重点关注TCL正则匹配与文本处理方法,能够写出简单的文本处理脚本 ## 1.1 阅读全文

posted @ 2023-07-26 20:53

陆路慧

阅读(4114)

评论(0)

推荐(0)

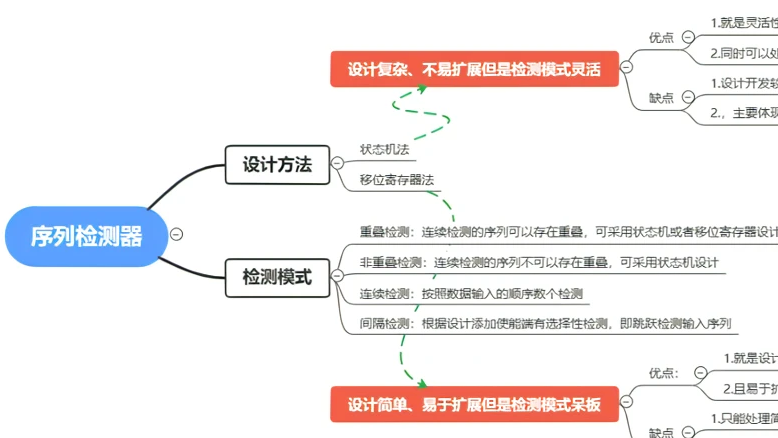

数字IC经典电路设计 经典电路设计是数字IC设计里基础中的基础,盖大房子的第一部是打造结实可靠的地基,每一篇笔者都会分门别类给出设计原理、设计方法、verilog代码、Testbench、仿真波形。然而实际的数字IC设计过程中考虑的问题远多于此,通过本系列希望大家对数字IC中一些经典电路的设计有初步 阅读全文

数字IC经典电路设计 经典电路设计是数字IC设计里基础中的基础,盖大房子的第一部是打造结实可靠的地基,每一篇笔者都会分门别类给出设计原理、设计方法、verilog代码、Testbench、仿真波形。然而实际的数字IC设计过程中考虑的问题远多于此,通过本系列希望大家对数字IC中一些经典电路的设计有初步 阅读全文