基于labview和fpga的信号发生器

配套FPGA开发板(含该设计的工程代码):https://item.taobao.com/item.htm?spm=a1z10.1-c.w4004-4676525296.4.6e8950ed57YPhv&id=17848039135

基于labview和fpga的信号发生器(实现FPGA部分,不提供labview代码)

要求:

【1】正弦波、方波、锯齿波、三角波。

【2】频率、幅值、相位可调,调节步进值:频率0.1,幅值0.1,相位1;

【3】频率最高:20k;峰值最高:3.3。

【4】波形选择控制字 频率控制字 相位控制字幅值控制字由labbiew产生然后发送给fpga进行控制。

【5】串口9600,数据协议由FPGA进行确定。

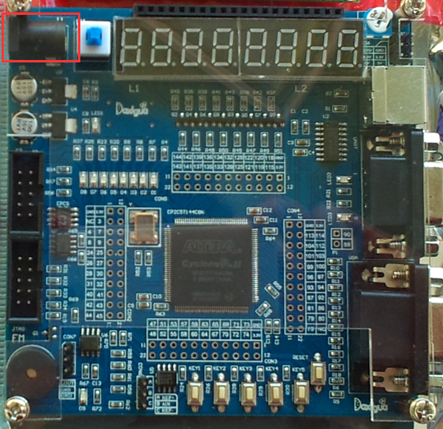

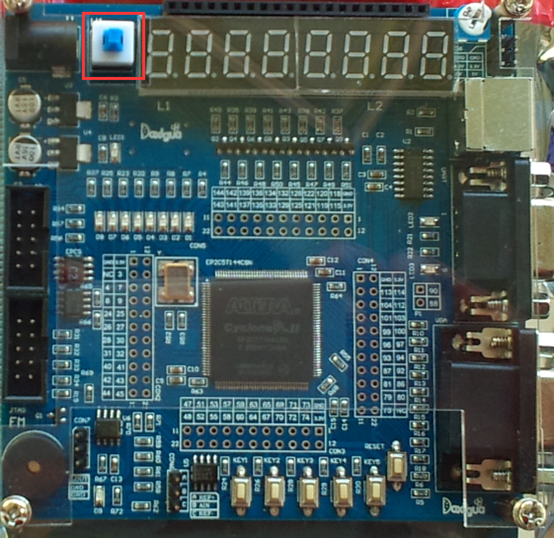

电路板

该设计中涉及到的硬件电路如下:

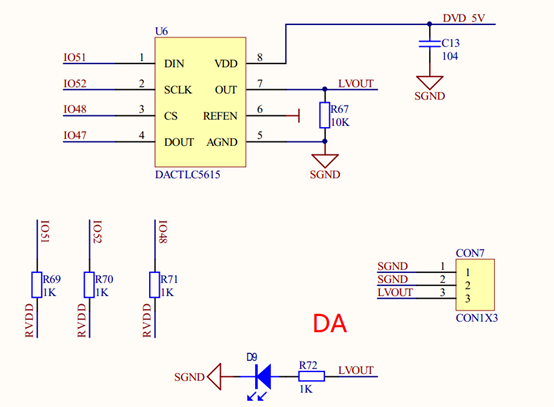

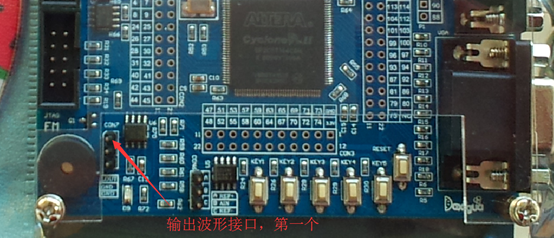

DAC电路

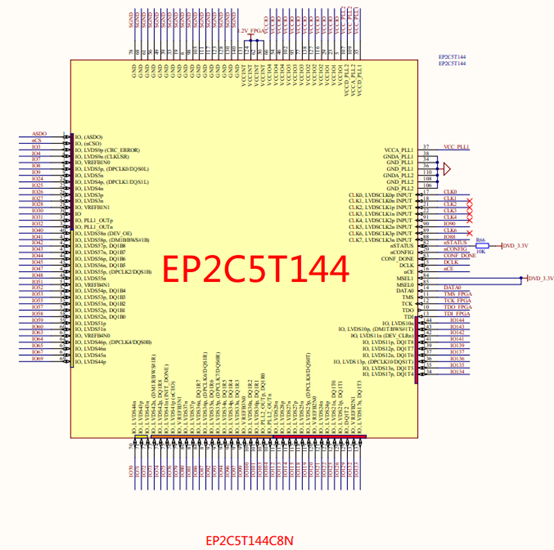

FPGA

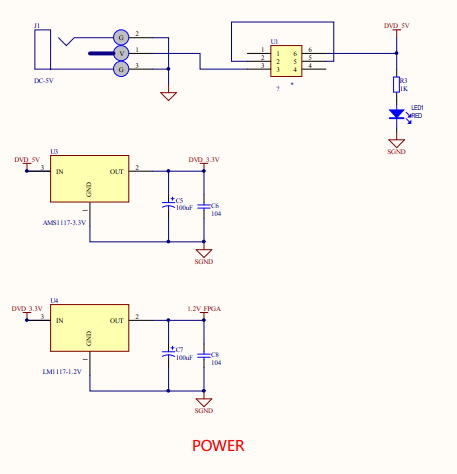

电源

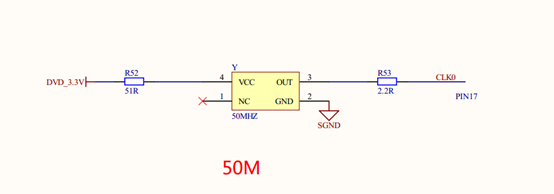

晶振

操作

上电

接入5V电源,用配套的线,USB那端接电脑即可;

电源开关

按下电源开关

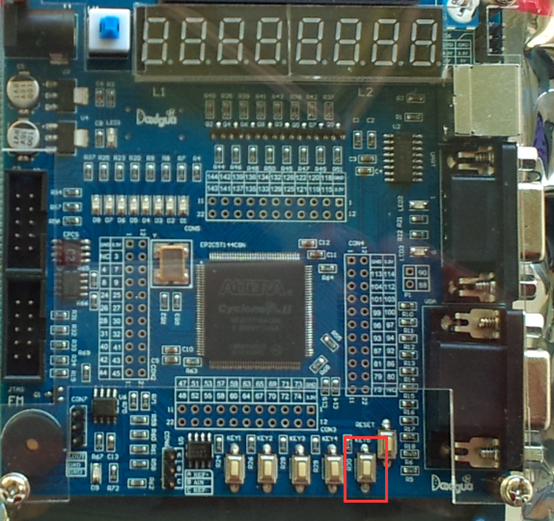

复位

输出正弦波

DAC波形输出与示波器的接法

DAC芯片旁边插针为3个

图示接口接示波器!

谨防短路!

通信协议

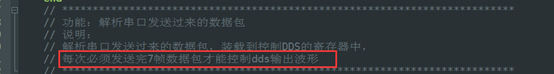

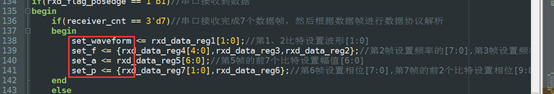

每次必须发送完8帧数据包才能控制dds输出波形!!!

|

第1帧 |

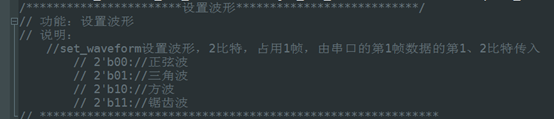

第1、2比特设置波形[1:0] |

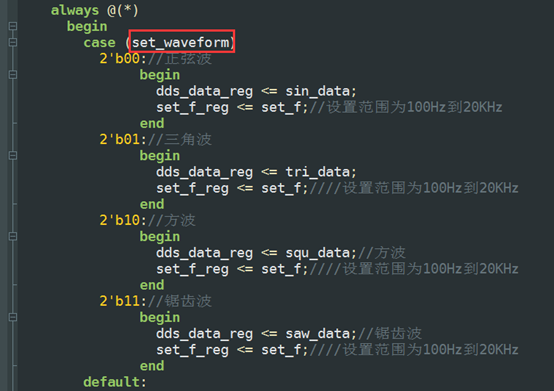

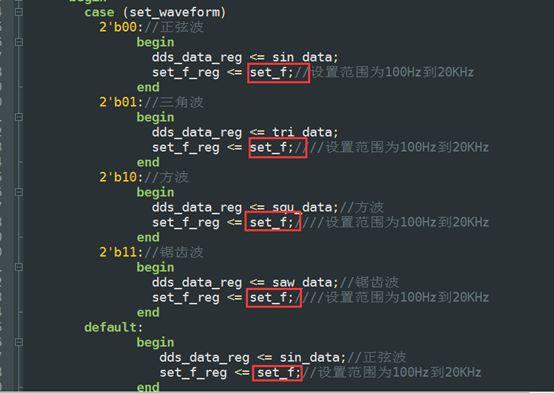

设置波形,2比特,占用1帧,由串口的第1帧数据的第1、2比特传入, 2'b00:正弦波; 2'b01:三角波; 2'b10:方波; 2'b11:锯齿波 |

rxd_data_processing.v文件 |

|

第2帧 |

整帧设置频率的[7:0] |

||

|

第3帧 |

整帧设置频率的[15:8] |

||

|

第4帧 |

整帧设置频率的[23:16] |

||

|

第5帧 |

整帧设置频率的[31:24] |

||

|

第6帧 |

整帧的前7个比特设置幅值[6:0] |

||

|

第7帧 |

整帧设置相位[7:0] |

||

|

第8帧 |

整帧的前2个比特设置相位[9:8] |

||

|

第9帧 |

保留 |

||

|

第10帧 |

保留 |

接收串口数据帧组合成数据包

解析串口发送过来的数据包

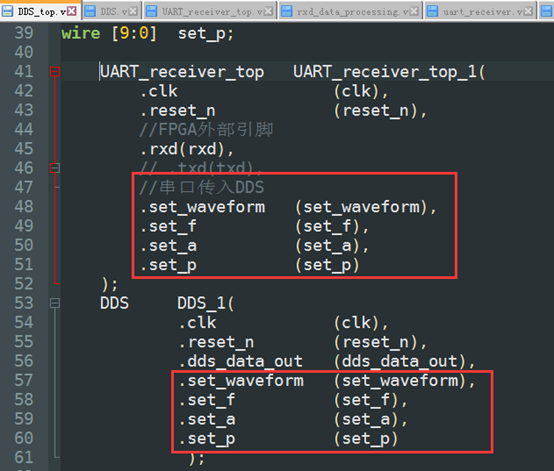

顶层信号连接

波形控制原理

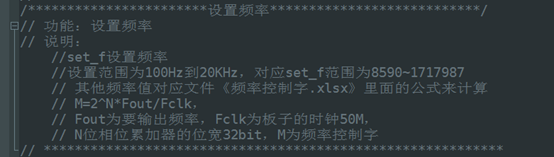

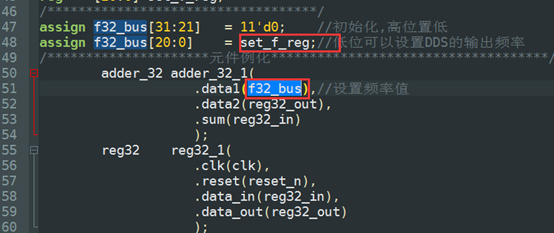

频率控制原理

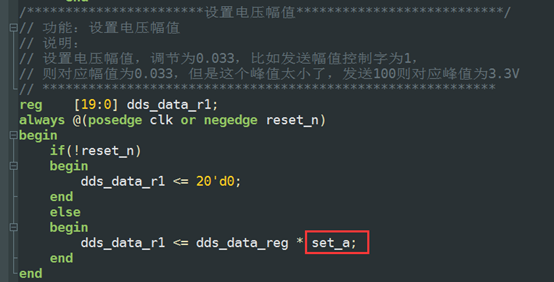

幅值控制原理

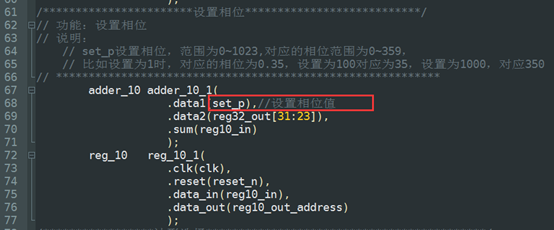

相位控制原理

浙公网安备 33010602011771号

浙公网安备 33010602011771号