19_基于FPGA驱动LCD12864显示字符

19_基于FPGA驱动LCD12864显示字符

实验原理

LCD12864驱动原理

LCD12864的驱动原理与LCD1602的驱动原理相似,不同之处体现在LCD12864采用的是上下分屏或者是左右分屏进行驱动的。

12864是一种图形点阵液晶显示器,它主要由行驱动器/ 列驱动器及128×64全点阵液晶显示器组成.可完成图形显示,也可以显示8×4个(16×16点阵)汉字。

主要技术参数和性能:

1.电源:VDD:+5V;

2.显示内容:128(列)×64(行)点

3.全屏幕点阵

4.七种指令

5.与CPU接口采用8位数据总线并行输入输出和8条控制线.

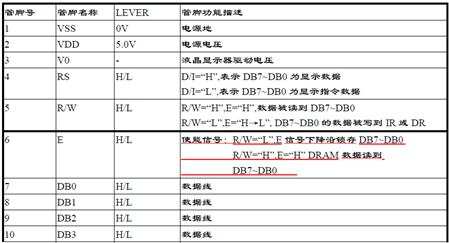

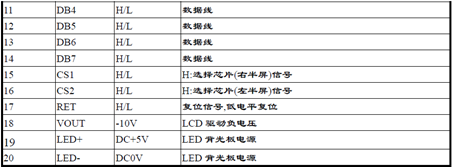

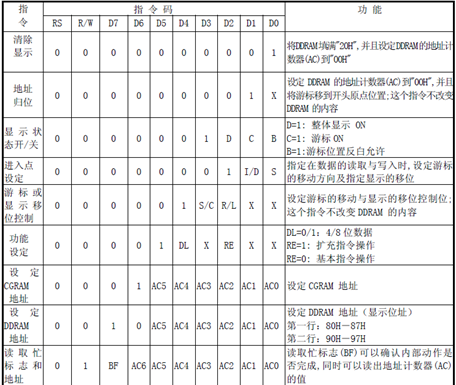

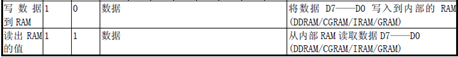

LCD12964的接口说明

由该表可以知道,要对LCD12864进行显示操作则必须操作数据信号(DB)和控制信号(RS、R/W、E)。发送数据的时候,采用RS来区分数据和指令,采用R/W来控制数据的读写。因为显示LCD12864只需用到写数据,所以当向LCD12864送入数据的时候将E输出一个下降沿。具体的操作方法要根据写数据时序进行设计。

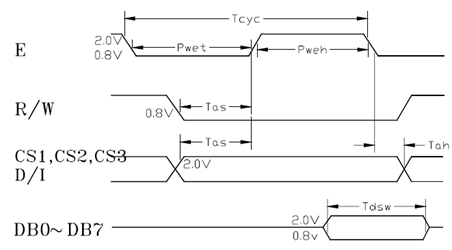

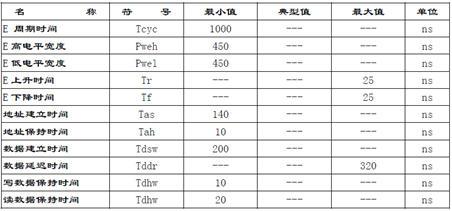

LCD12864的写数据时序分析

对LCD12864写数据时,主要的控制信号有:E、R/W、RS(送数据时置为高电平,送指令时置为低电平)。根据时序的参数表,在该工程中将E的时钟频率设置为1.5M(芯片手册的频率为1M),在进行写数据时根据E的时钟边沿,在E的上升沿将R/W置低,然后送出数据,当E出现下降沿的时候数据便会读进LCD12864内部寄存器中。

LCD12864控制指令说明

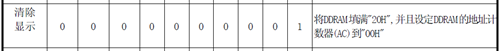

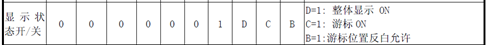

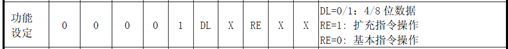

在进行写数据之前必须进行寄存器的设置,一般的显示设置涉及到的指令有:清除显示、显示开关状态、游标或显示移位控制、功能设定。

清除显示:01H

显示开关状态:0CH(整体显示、关游标、不允许反白)

游标或显示移位控制:

功能设定:31H(8位格式,基本指令)

指令设置过程如下:

- 设置8位格式

- 整体显示,关光标,不闪烁

- 设定输入方式,增量不移位

- 清除显示

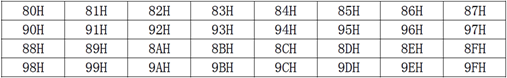

LCD12864字符显示地址:

每屏可显示4 行8 列共32个16×16 点阵的汉字,每个显示RAM 可显示1个中文字符或2个16×8 点阵全高ASCII 码字符,即每屏最多可实现32个中文字符或64个ASCII 码字符的显示。根据写入内容的不同,可分别在液晶屏上显示CGROM(中文字库)、HCGROM

(ASCII 码字库)及CGRAM(自定义字形)的内容。字符显示RAM 在液晶模块中的地址80H~9FH。字符显示的RAM 的地址与32个字符显示区域有着一一对应的关系,其对应关系如下表所示:

在该工程中需要将LCD12864的整个屏幕显示中文字符和英文字符,显示将整个屏幕分为4行进行显示控制。第一行到第四行的地址分别为80H、90H、88H、98H。

在显示数据发送完之后,将E置低,然后延迟一段时间后将E拉高,最后对屏幕进行刷新。

在显示ASCII 码字符时可以直接采用字符,而当显示中文时必须查找中文字型码表,中文字型采用的是16位的寻址,由于数据线只有8位,所以输出数据时采用分时复用,先输出高八位,后输出低八位。假如要显示"大",通过中文字型码表可以得出其地址为:B4F3。

所以输出数据时,先输出B4,后输出F3。

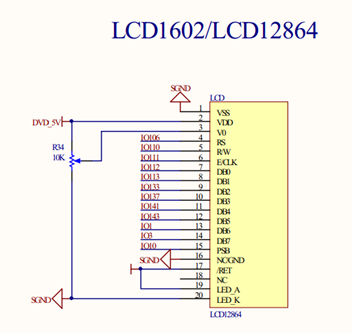

硬件原理图

LCD12864的接口与LCD1602接口进行复用,所以使用时需要将PSB置高,作为背光电源,滑动变阻器用来设置背光灯的亮度。

实验代码

主要分为两个模块,分别为分频模块,用来产生驱动的信号信号和使能信号E。

另一个为显示驱动模块用来进行指令和数据的发送,控制过程采用状态机进行控制各个状态的转移。

/********************************版权声明************************************** ** 大西瓜团队 ** **----------------------------文件信息-------------------------- ** 文件名称: lcd12864.v ** 创建日期: ** 功能描述:实现LCD显示功能 ** 硬件平台:大西瓜第三代开发板,http://daxiguafpga.taobao.com ** 版权声明:本代码属个人知识产权,本代码仅供交流学习. **---------------------------修改文件的相关信息---------------- ** 修改人: ** 修改日期: ** 修改内容: *******************************************************************************/ module lcd12864(clk,rs,rw,en,dat,psb); input clk; //系统时钟输入50M output [7:0] dat; //LCD的8位数据口 output rs,rw,en,psb; //LCD的控制脚

reg e; reg [7:0] dat; reg rs; reg [15:0] counter; reg [6:0] current,next; reg clkr; reg [1:0] cnt; /////////////////////////////////////////////

assign psb=1'b1; assign rw=0; always @(posedge clk) //da de shi zhong pinlv begin counter=counter+1; if(counter==16'h000f) clkr=~clkr; end //////////////////////////////////////////////// always @(posedge clkr) begin current=next; case(current) 7'd0: begin rs<=0; dat<=8'h31; next<=next+1'b1;end //*设置8位格式,* 7'd1: begin rs<=0; dat<=8'h0C; next<=next+1'b1;end //*整体显示,关光标,不闪烁*/ 7'd2: begin rs<=0; dat<=8'h06; next<=next+1'b1; end //*设定输入方式,增量不移位*/ 7'd3: begin rs<=0; dat<=8'h01; next<=next+1'b1; end //*清除显示*/

7'd4: begin rs<=1; dat<=8'hB4; next<=next+1'b1; end //显示第一行 7'd5: begin rs<=1; dat<=8'hF3; next<=next+1'b1; end

7'd6: begin rs<=1; dat<=8'hCE; next<=next+1'b1; end 7'd7: begin rs<=1; dat<=8'hF7;next<=next+1'b1; end

7'd8: begin rs<=1; dat<=8'hB9; next<=next+1'b1; end 7'd9: begin rs<=1; dat<=8'hCF; next<=next+1'b1; end

7'd10: begin rs<=1; dat<="-"; next<=next+1'b1; end 7'd11: begin rs<=1; dat<="F";next<=next+1'b1; end 7'd12: begin rs<=1; dat<="P"; next<=next+1'b1; end 7'd13: begin rs<=1; dat<="G";next<=next+1'b1; end 7'd14: begin rs<=1; dat<="A"; next<=next+1'b1; end 7'd15: begin rs<=1; dat<="!"; next<=next+1'b1; end 7'd16: begin rs<=1; dat<=" ";next<=next+1'b1; end 7'd17: begin rs<=1; dat<=" "; next<=next+1'b1; end

7'd18: begin rs<=0; dat<=8'h90; next<=next+1'b1; end //显示第二行

7'd19: begin rs<=1; dat<=8'hcc; next<=next+1'b1; end 7'd20: begin rs<=1; dat<=8'hd4; next<=next+1'b1; end

7'd21: begin rs<=1; dat<=8'hb1; next<=next+1'b1; end 7'd22: begin rs<=1; dat<=8'ha6; next<=next+1'b1; end

7'd23: begin rs<=1; dat<=8'hb5; next<=next+1'b1; end 7'd24: begin rs<=1; dat<=8'hea; next<=next+1'b1; end

7'd25: begin rs<=1; dat<=":"; next<=next+1'b1; end 7'd26: begin rs<=1; dat<="h"; next<=next+1'b1; end

7'd27: begin rs<=1; dat<="t"; next<=next+1'b1; end 7'd28: begin rs<=1; dat<="t"; next<=next+1'b1; end

7'd29: begin rs<=1; dat<="p"; next<=next+1'b1; end 7'd30: begin rs<=1; dat<=":"; next<=next+1'b1; end

7'd31: begin rs<=1; dat<="/"; next<=next+1'b1; end 7'd32: begin rs<=1; dat<="/"; next<=next+1'b1; end

7'd33: begin rs<=1; dat<="d"; next<=next+1'b1; end 7'd34: begin rs<=1; dat<="a"; next<=next+1'b1; end

7'd35: begin rs<=0; dat<=8'h88; next<=next+1'b1; end //显示第三行

7'd36: begin rs<=1; dat<="x"; next<=next+1'b1; end // 7'd37: begin rs<=1; dat<="i"; next<=next+1'b1; end

7'd38: begin rs<=1; dat<="g"; next<=next+1'b1; end 7'd39: begin rs<=1; dat<="u"; next<=next+1'b1; end

7'd40: begin rs<=1; dat<="a"; next<=next+1'b1; end 7'd41: begin rs<=1; dat<="f"; next<=next+1'b1; end

7'd42: begin rs<=1; dat<="p"; next<=next+1'b1; end 7'd43: begin rs<=1; dat<="g"; next<=next+1'b1; end

7'd44: begin rs<=1; dat<="a"; next<=next+1'b1; end 7'd45: begin rs<=1; dat<="."; next<=next+1'b1; end

7'd46: begin rs<=1; dat<="t"; next<=next+1'b1; end 7'd47: begin rs<=1; dat<="a"; next<=next+1'b1; end

7'd48: begin rs<=1; dat<="o"; next<=next+1'b1; end 7'd49: begin rs<=1; dat<="b"; next<=next+1'b1; end

7'd50: begin rs<=1; dat<="a"; next<=next+1'b1; end 7'd51: begin rs<=1; dat<="o"; next<=next+1'b1; end

7'd52: begin rs<=0; dat<=8'h98; next<=next+1'b1; end //显示第四行

7'd53: begin rs<=1; dat<="."; next<=next+1'b1; end 7'd54: begin rs<=1; dat<="c"; next<=next+1'b1; end

7'd55: begin rs<=1; dat<="o"; next<=next+1'b1; end 7'd56: begin rs<=1; dat<="m"; next<=next+1'b1; end

7'd57: begin rs<=1; dat<=8'hd0; next<=next+1'b1; end 7'd58: begin rs<=1; dat<=8'hbb; next<=next+1'b1; end

7'd59: begin rs<=1; dat<=8'hd0; next<=next+1'b1; end 7'd60: begin rs<=1; dat<=8'hbb; next<=next+1'b1; end//

7'd61: begin rs<=0; dat<=8'h00; // 把液晶的E 脚 拉高 if(cnt!=2'b10) begin e<=0;next<=7'd0;cnt<=cnt+1; end else begin next<=7'd61; e<=1; end end default: next=7'd0; endcase end assign en=clkr|e; endmodule |

实验操作

实验效果

大西瓜FPGA-->https://daxiguafpga.taobao.com

配套开发板:https://item.taobao.com/item.htm?spm=a1z10.1-c.w4004-24211932856.3.489d7241aCjspB&id=633897209972

博客资料、代码、图片、文字等属大西瓜FPGA所有,切勿用于商业! 若引用资料、代码、图片、文字等等请注明出处,谢谢!

每日推送不同科技解读,原创深耕解读当下科技,敬请关注微信公众号"科乎"。

浙公网安备 33010602011771号

浙公网安备 33010602011771号