09_基于FPGA驱动蜂鸣器唱歌

09_基于FPGA驱动蜂鸣器唱歌

实验原理

结构原理

1.压电式蜂鸣器 压电式蜂鸣器主要由多谐振荡器、压电蜂鸣片、阻抗匹配器及共鸣箱、外壳等组成。有的压电式蜂鸣器外壳上还装有发光二极管。

多谐振荡器由晶体管或集成电路构成。当接通电源后(1.5~15V直流工作电压),多谐振荡器起振,输出1.5~2.5kHZ的音频信号,阻抗匹配器推动压电蜂鸣片发声。

压电蜂鸣片由锆钛酸铅或铌镁酸铅压电陶瓷材料制成。在陶瓷片的两面镀上银电极,经极化和老化处理后,再与黄铜片或不锈钢片粘在一起。

2.电磁式蜂鸣器 电磁式蜂鸣器由振荡器、电磁线圈、磁铁、振动膜片及外壳等组成。

接通电源后,振荡器产生的音频信号电流通过电磁线圈,使电磁线圈产生磁场。振动膜片在电磁线圈和磁铁的相互作用下,周期性地振动发声。

现在市场上出售的一种小型蜂鸣器因其体积小(直径只有llmm)、重量轻、价格低、结构牢靠,而广泛地应用在各种需要发声的电器设备、电子制作和单片机等电路中。

从外观上看,两种蜂鸣器好像一样,但仔细看,两者的高度略有区别,有源蜂鸣器高度为9mm,而无源蜂鸣器的高度为8mm。如将两种蜂鸣器的引脚郡朝上放置时,可以看出有绿色电路板的一种是无源蜂鸣器,没有电路板而用黑胶封闭的一种是有源蜂鸣器。

迸一步判断有源蜂鸣器和无源蜂鸣器,还可以用万用表电阻档Rxl档测试:用黑表笔接蜂鸣器 "+"引脚,红表笔在另一引脚上来回碰触,如果触发出咔、咔声的且电阻只有8Ω(或16Ω)的是无源蜂鸣器;如果能发出持续声音的,且电阻在几百欧以上的,是有源蜂鸣器。

有源蜂鸣器直接接上额定电源(新的蜂鸣器在标签上都有注明)就可连续发声;而无源蜂鸣器则和电磁扬声器一样,需要接在音频输出电路中才能发声。

硬件原理图

实验代码

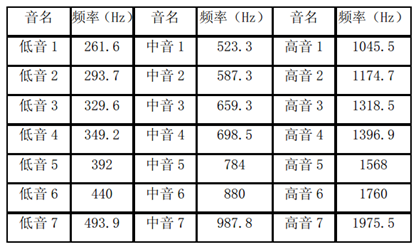

/********************************版权声明************************************** ** 大西瓜团队 ** **----------------------------文件信息-------------------------- ** 文件名称: song.v ** 创建日期: ** 功能描述: ** 硬件平台:大西瓜第三代开发板,http://daxiguafpga.taobao.com ** 版权声明:本代码属个人知识产权,本代码仅供交流学习. **---------------------------修改文件的相关信息---------------- ** 修改人: ** 修改日期: ** 修改内容: *******************************************************************************/ //音高与频率的对应关系 //---------------------------------------------------------------------- //| | 1 | 2 | 3 | 4 | 5 | 6 | 7 | //|低音 |261.6Hz |293.7Hz |329.6Hz |349.2Hz | 392Hz | 440Hz |493.9Hz | //|中音 |523.3Hz |587.3Hz |659.3Hz |698.5Hz | 784Hz | 880Hz |987.8Hz | //|高音 |1045.5Hz|1174.7Hz|1318.5Hz|1396.9Hz| 1568Hz | 1760Hz |1975.5Hz| //---------------------------------------------------------------------- module song(clk,beep); //模块名称song input clk; //系统时钟50MHz output beep; //蜂鸣器输出端

reg beep_r; //寄存器 reg[7:0] state; //乐谱状态机 reg[15:0]count,count_end; reg[23:0]count1;

//乐谱参数:D=F/2K (D:参数,F:时钟频率,K:音高频率) parameter L_3 = 16'd75850, //低音3 L_5 = 16'd63776, //低音5 L_6 = 16'd56818, //低音6 L_7 = 16'd50618, //低音7 M_1 = 16'd47774, //中音1 M_2 = 16'd42568, //中音2 M_3 = 16'd37919, //中音3 M_5 = 16'd31888, //中音5 M_6 = 16'd28409, //中音6 H_1 = 16'd23912; //高音1 parameter TIME = 12000000; //控制每一个音的长短(250ms)

assign beep = beep_r; //输出音乐

always@(posedge clk) begin count <= count + 1'b1; //计数器加1 if(count == count_end) begin count <= 16'h0; //计数器清零 beep_r <= !beep_r; //输出取反 end end

always @(posedge clk) begin if(count1 < TIME) //一个节拍250mS count1 = count1 + 1'b1; else begin count1 = 24'd0; if(state == 8'd66) state = 8'd0; else state = state + 1'b1; case(state) 8'd0,8'd1,8'd2,8'd3: count_end = L_3;//低音"3",持续4个节拍 8'd4,8'd5,8'd6: count_end = L_5;//低音"5",持续3个节拍 8'd7: count_end = L_6;//低音"6",持续1个节拍 8'd8,8'd9,8'd10: count_end = M_1;//中音"1",持续3个节拍 8'd11: count_end = M_2;//中音"2",持续1个节拍 8'd12: count_end = L_6;//低音"6",持续1个节拍 8'd13: count_end = M_1;//中音"1",持续1个节拍 8'd14,8'd15: count_end = L_5;//低音"5",持续2个节拍 8'd16: count_end = M_1;//中音"1",持续1个节拍 8'd17,8'd18: count_end = L_5;//低音"5",持续2个节拍 8'd19,8'd20,8'd21: count_end = M_5;//中音"5",持续3个节拍 8'd22: count_end = H_1;//高音"1",持续1个节拍 8'd23: count_end = M_6;//中音"6",持续1个节拍 8'd24: count_end = M_5;//中音"5",持续1个节拍 8'd25: count_end = M_3;//中音"3",持续1个节拍 8'd26: count_end = M_5;//中音"5",持续1个节拍 8'd27,8'd28,8'd29,8'd30,8'd31, 8'd32,8'd33,8'd34,8'd35,8'd36,8'd37:count_end = M_2;//中音"2",持续11个节拍 8'd38: count_end = M_3;//中音"3",持续1个节拍 8'd39,8'd40: count_end = L_7;//低音"7",持续2个节拍 8'd41,8'd42: count_end = L_6;//低音"6",持续2个节拍 8'd43,8'd44,8'd45: count_end = L_5;//低音"5",持续3个节拍 8'd46: count_end = L_6;//低音"6",持续1个节拍 8'd47,8'd48: count_end = M_1;//中音"1",持续2个节拍 8'd49,8'd50: count_end = M_2;//中音"2",持续2个节拍 8'd51,8'd52: count_end = L_3;//低音"3",持续2个节拍 8'd53,8'd54,8'd55: count_end = M_1;//中音"1",持续3个节拍 8'd56,8'd57: count_end = L_5;//低音"5",持续2个节拍 8'd58: count_end = M_1;//中音"1",持续1个节拍 8'd59,8'd60,8'd61,8'd62,8'd63, 8'd64,8'd65,8'd66: count_end = L_5;//低音"5",持续8个节拍

endcase end end endmodule |

实验操作

实验效果

大西瓜FPGA-->https://daxiguafpga.taobao.com

博客资料、代码、图片、文字等属大西瓜FPGA所有,切勿用于商业! 若引用资料、代码、图片、文字等等请注明出处,谢谢!

浙公网安备 33010602011771号

浙公网安备 33010602011771号