步步详解之第1节----ALTERA FPGA关于PLL的使用,帮你用光所有PLL

-

PLL

-

创建工程

创建新工程

![]()

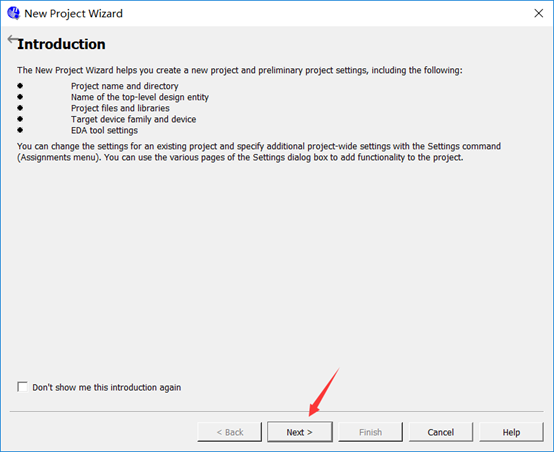

引导说明,点击next

![]()

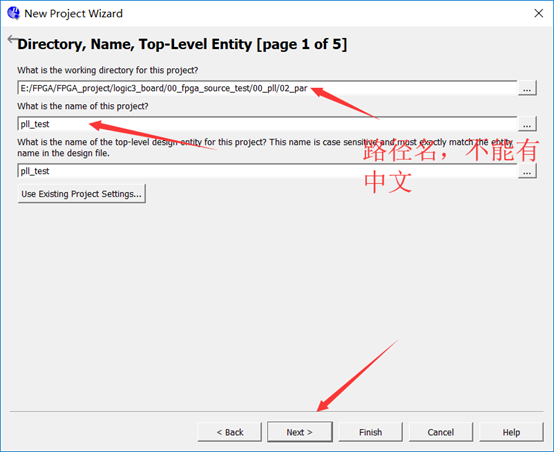

设置工程路径,不能有中文;设置工程名称,点击next

![]()

点击next

![]()

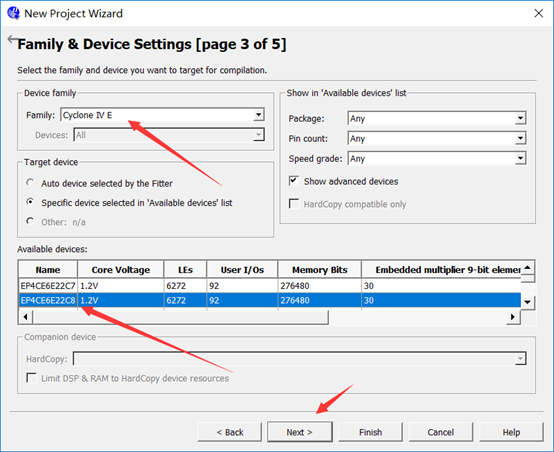

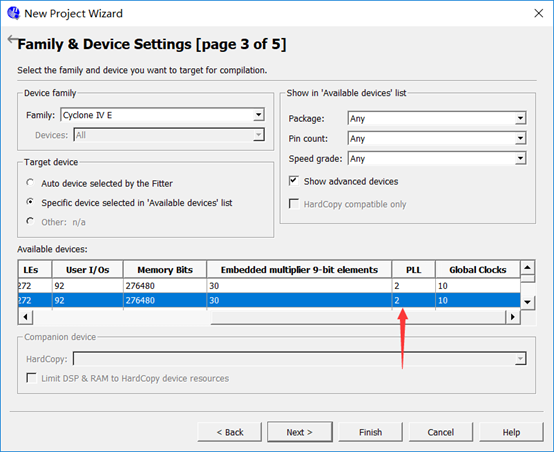

选择器件库,这里选择cyclone IV E,器件型号为EP4C6EE22C8,该器件有两个PLL;

![]()

![]()

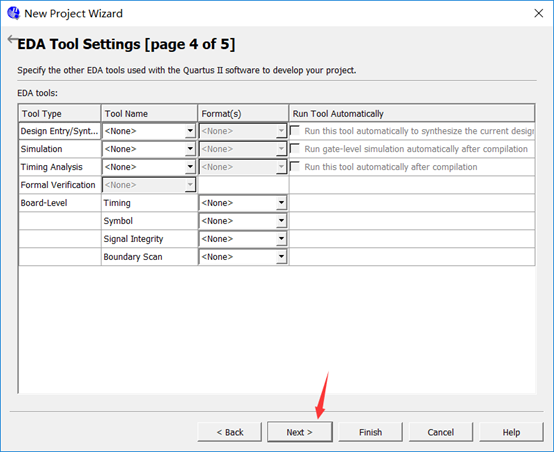

点击next

![]()

-

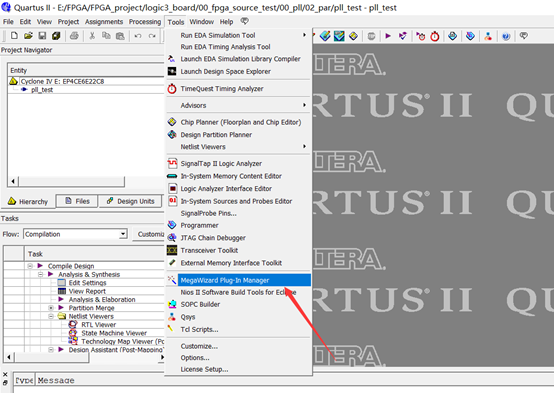

调用PLL IP核

调用PLL IP核

![]()

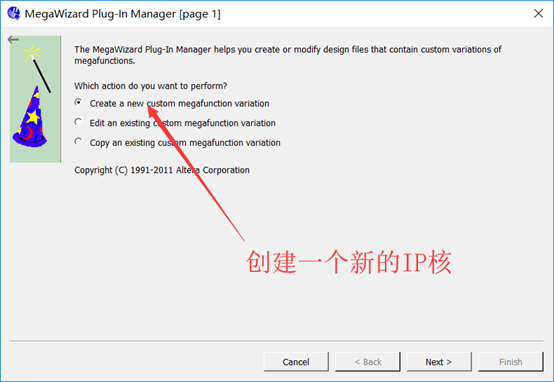

选择创建新的IP核

![]()

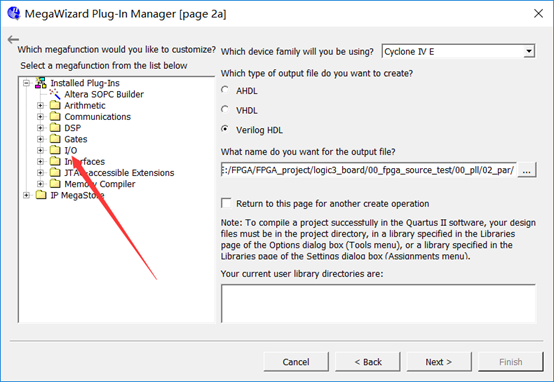

选择I/O

![]()

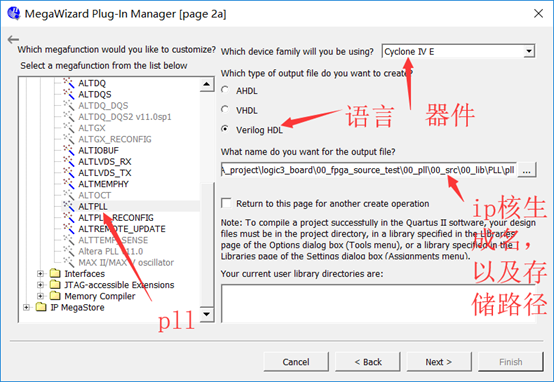

选择ALTPLL,器件类型、语言、设置IP的名称和文件路径

![]()

-

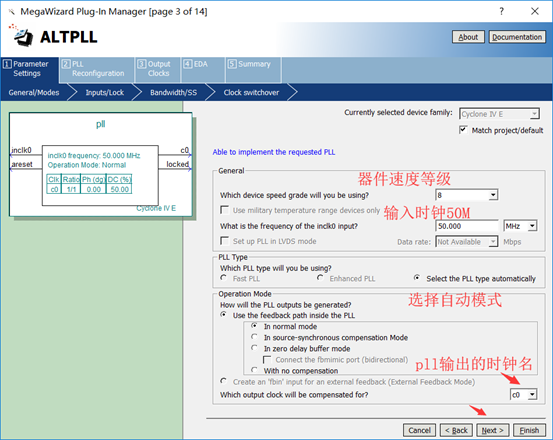

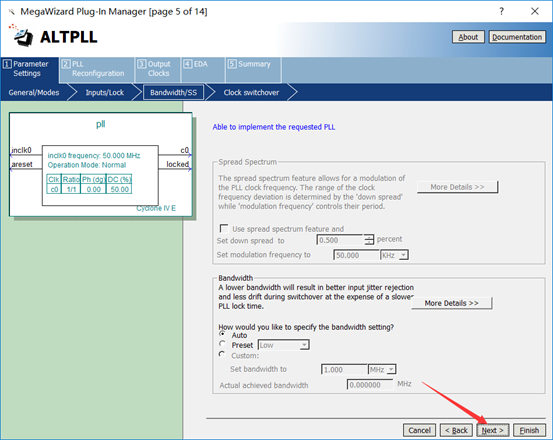

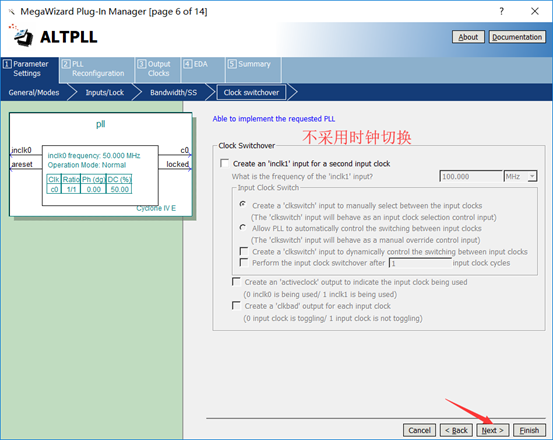

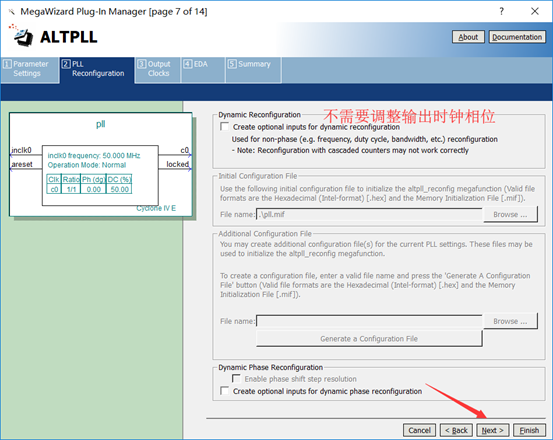

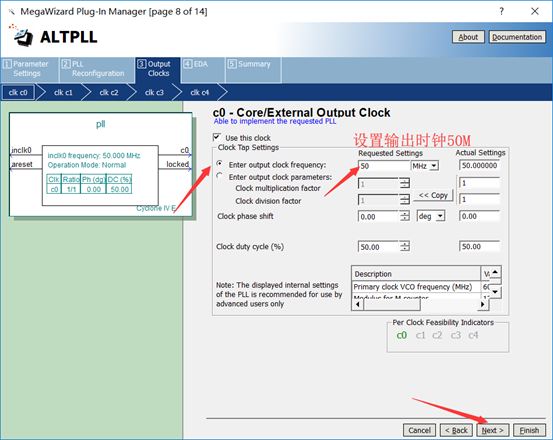

参数设置

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

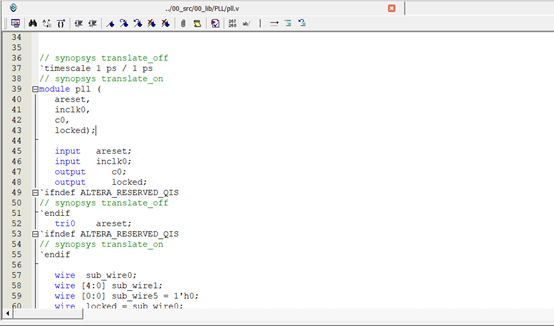

点击yes,成生成IP核文件,如下:

![]()

-

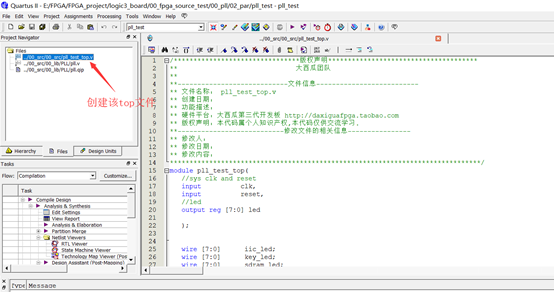

例化调用IP核

首先创建一个top文件,用来调用pll,

![]()

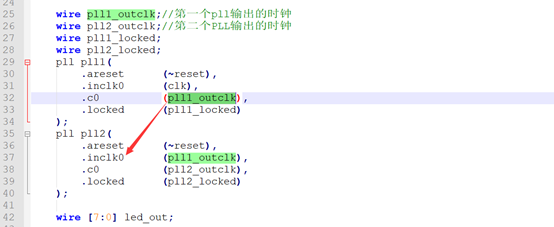

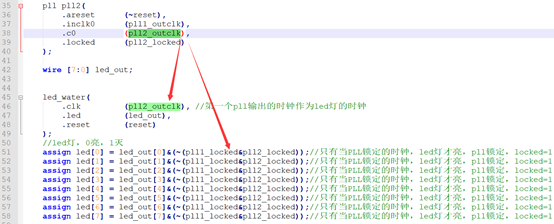

由于该器件包含有两个PLL,测试这两个PLL的功能,可以采用级联起来的方式:第一个PLL的时钟输出,作为第二个PLL的时钟输入,最后将第二个PLL的时钟输出作为LED灯模块的时钟输入;如果有很多个PLL,测试的时候也可以采用这种方式进行级联起来,有多少个PLL,就级联成多少级。

同时将两个PLL的锁定指示作为控制信号,锁定指示为1时表示锁定,为0时表示失锁,所以可以用这两个锁定信号来控制led灯的状态,当两个锁相环有一个为失锁时,LED灯灭,只有当两个都是锁定时,LED灯才能形成流水闪烁。

![]()

![]()

-

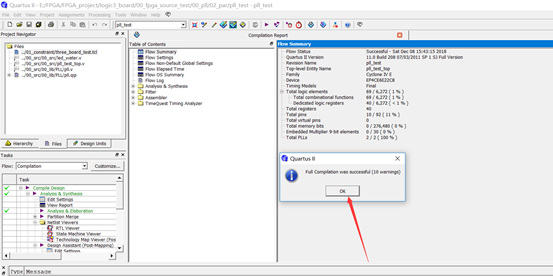

综合&布局布线

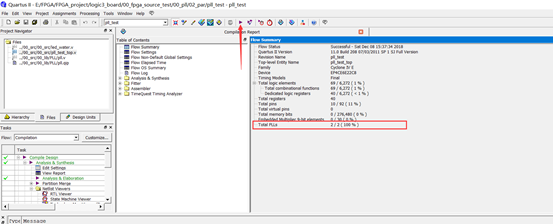

综合&布局布线之后,可以看到PLL的使用率达到100%。

![]()

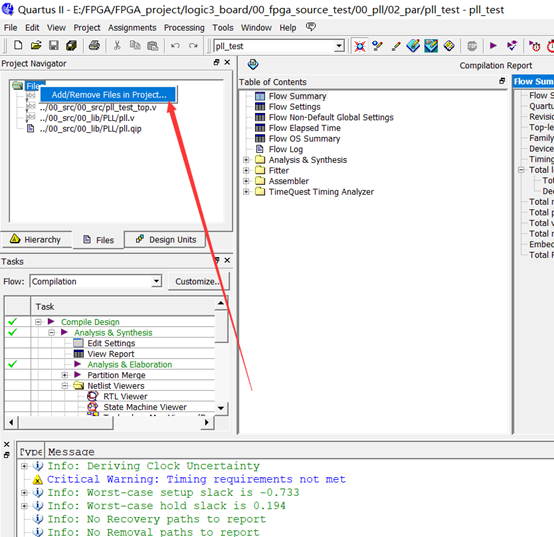

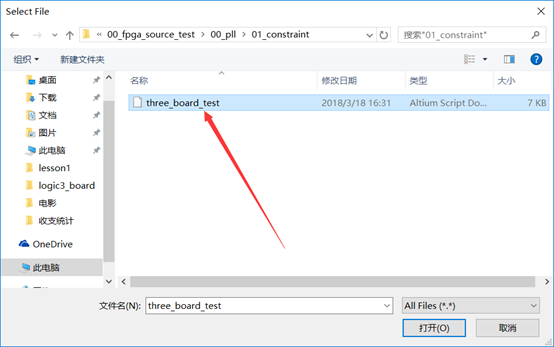

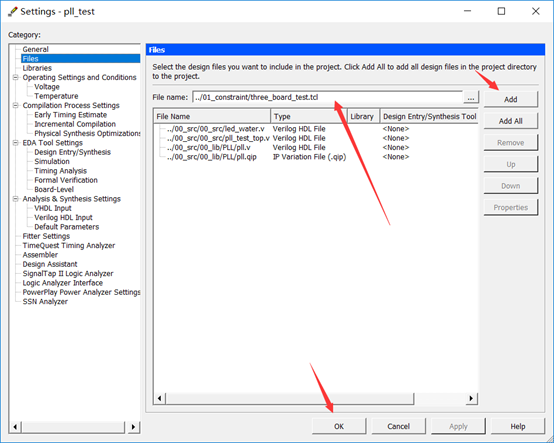

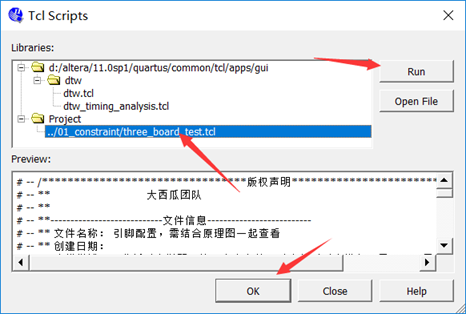

选择IO约束文件,用来约束IO的位置,大西瓜开发板已经提供完整的约束文件,直接调用即可:

![]()

![]()

![]()

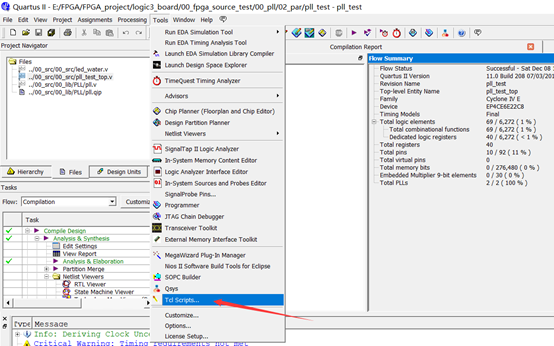

运行IO约束文件:

![]()

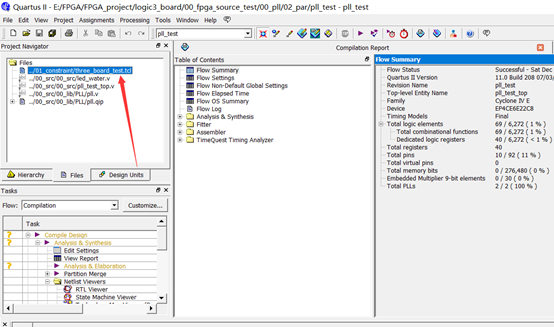

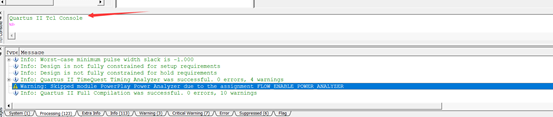

![]()

![]()

![]()

再重新布局布线一次:

![]()

-

查看布局布线后的结果

-

-

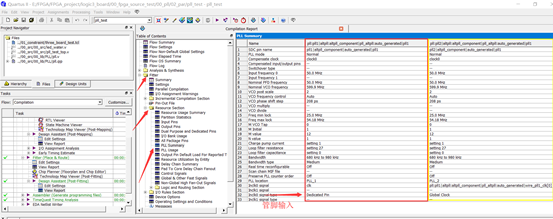

PLL资源的使用情况

查看每个PLL的使用情况,这是每个工程综合&布局布线之后必须确认的步骤:

![]()

-

PLL在芯片上的布局情况

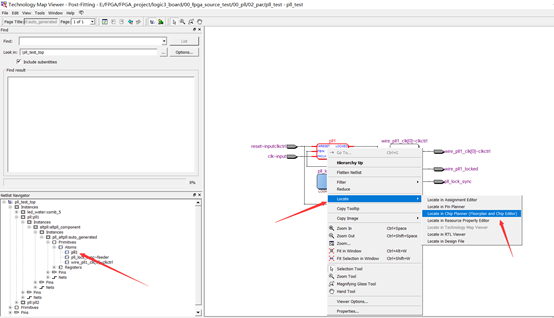

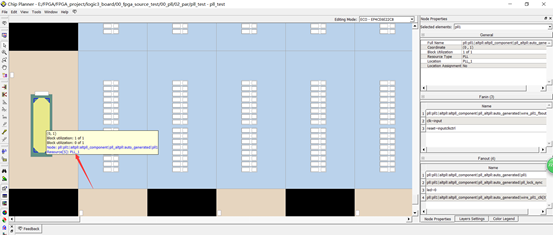

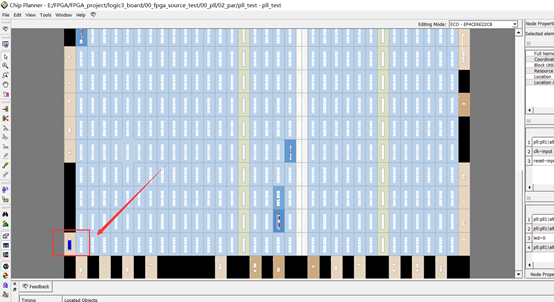

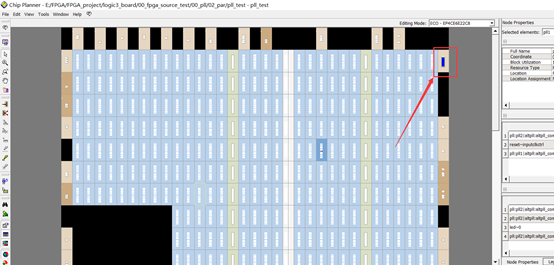

要更好的了解工程最后综合&布局布线之后的电路,必须查看布局布线的结果,这里采用由原理图定位到chip planner的方式,查看电路;

![]()

![]()

![]()

![]()

![]()

![]()

本文档为大西瓜FPGA所有,淘宝地址:https://daxiguafpga.taobao.com,

(如需转载或使用,请注明作者信息和出处,谢谢!)

代码链接:https://pan.baidu.com/s/1ba-qOC0f-NoWNUlM8jKRlA 密码:hz9t

浙公网安备 33010602011771号

浙公网安备 33010602011771号