cadence入门学习第二章之原理图绘制

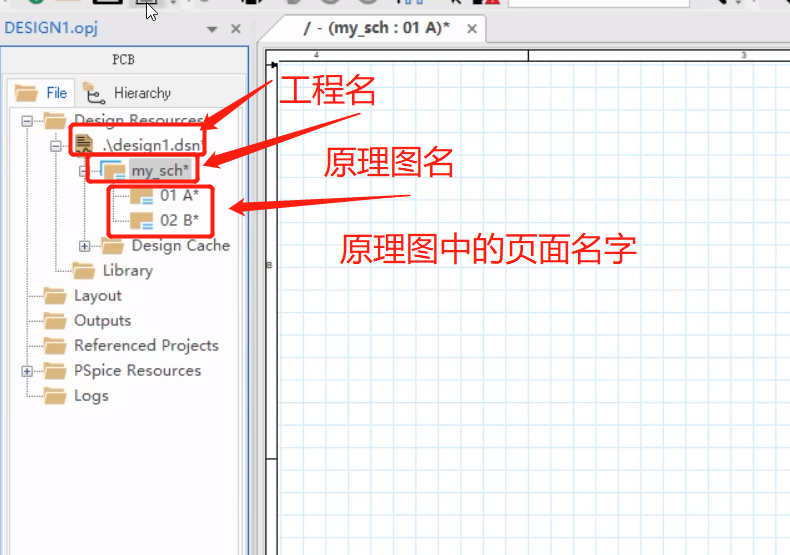

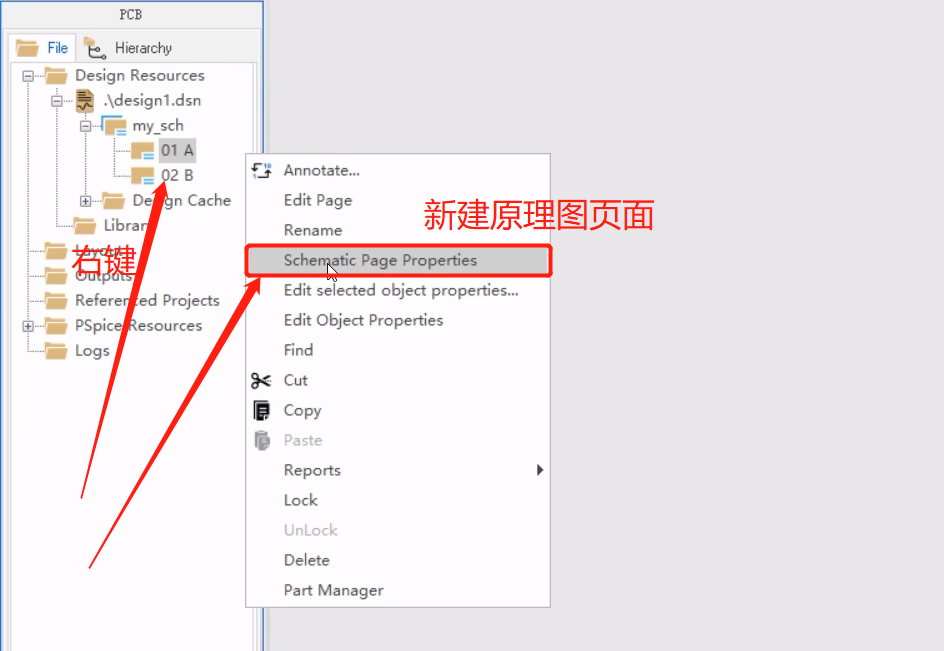

原理图的新建与添加

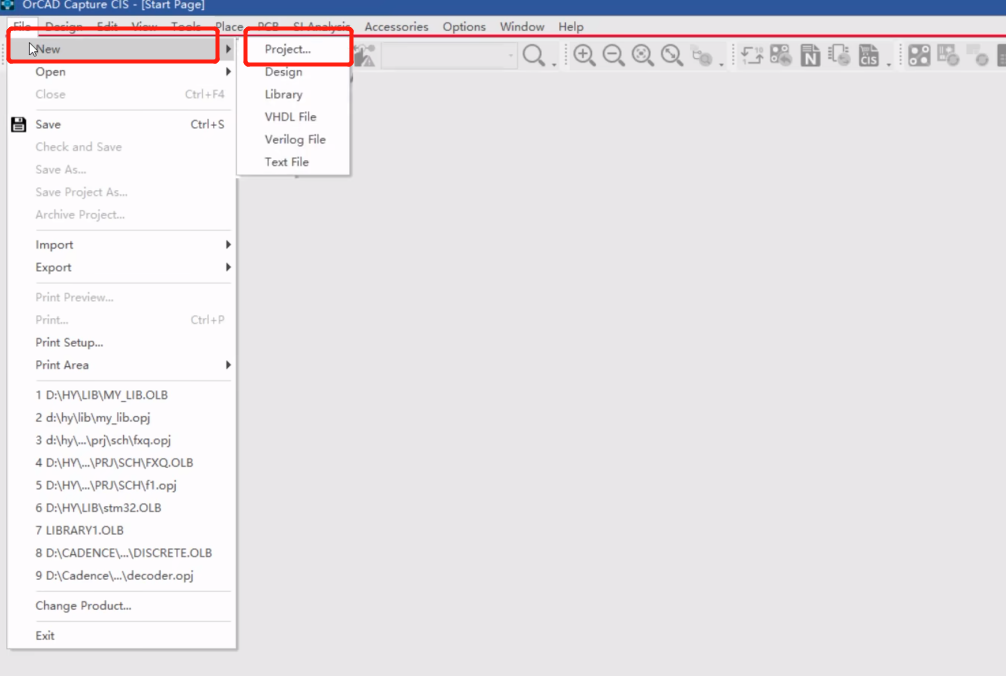

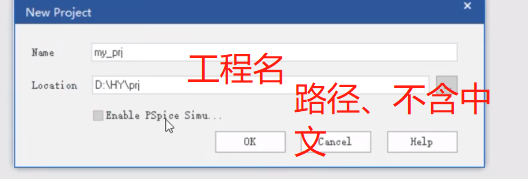

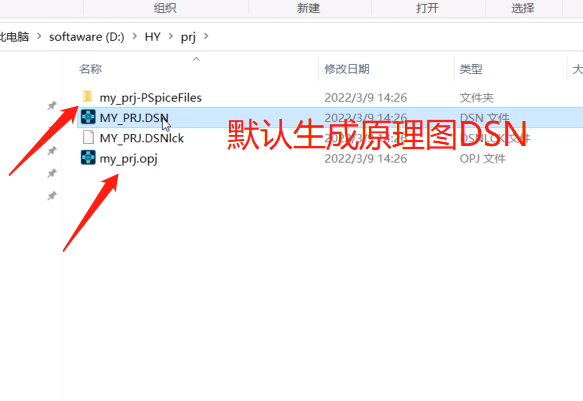

1、新建工程

工程以obj文件结尾!!!!

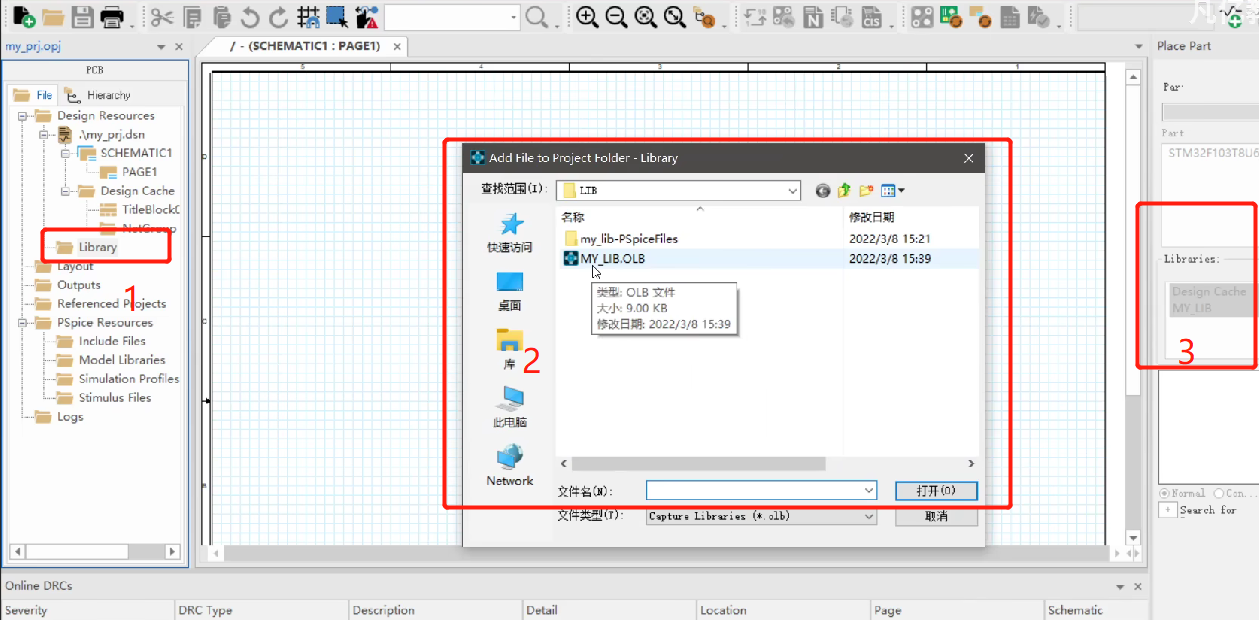

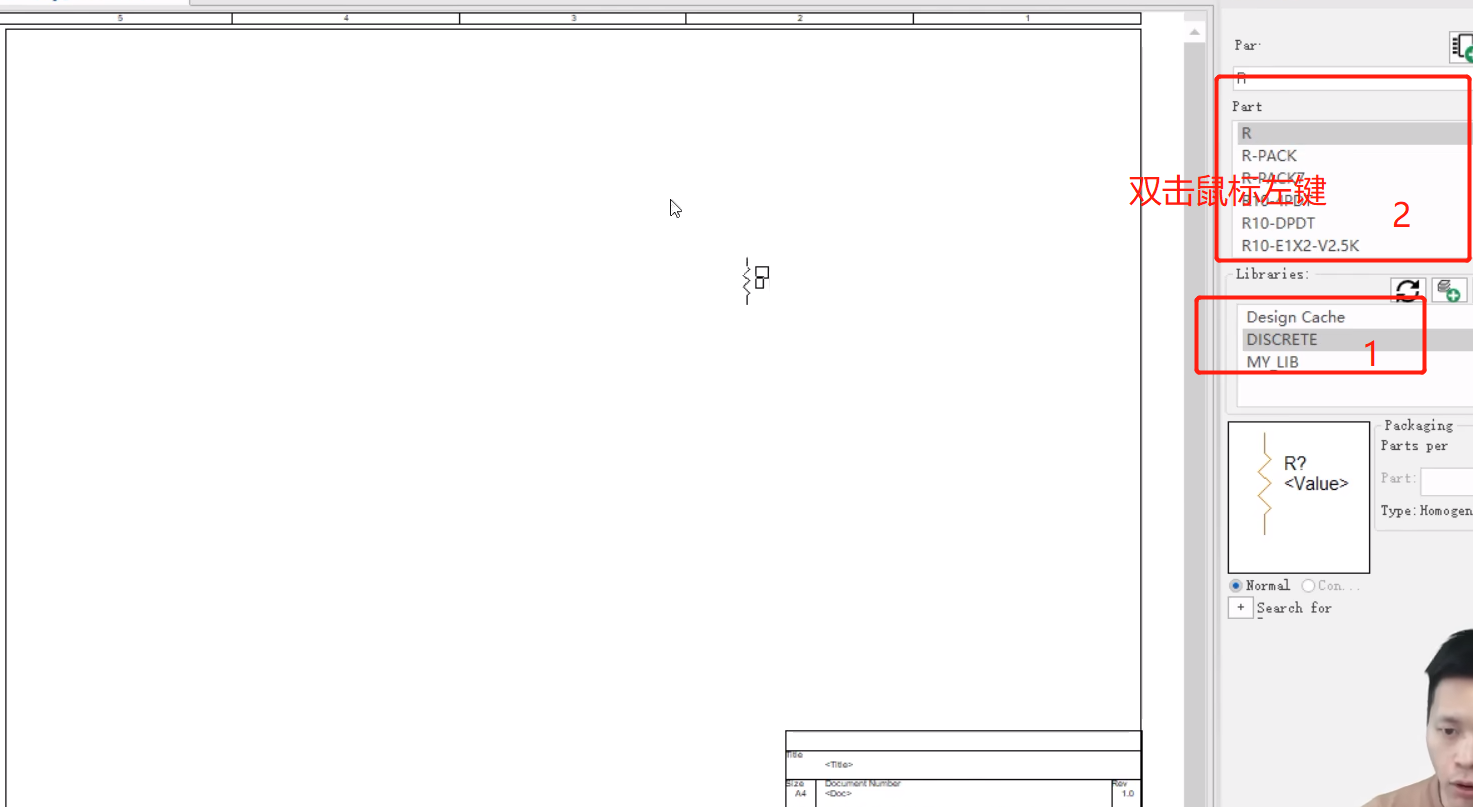

2、添加元件库

Lib中是没有的!!!添加后才会有!!!!

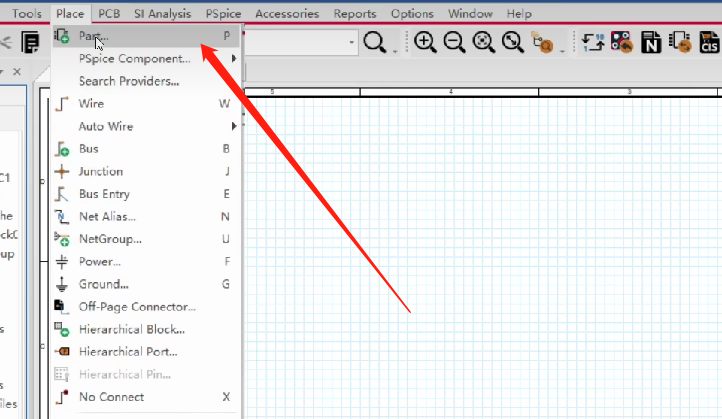

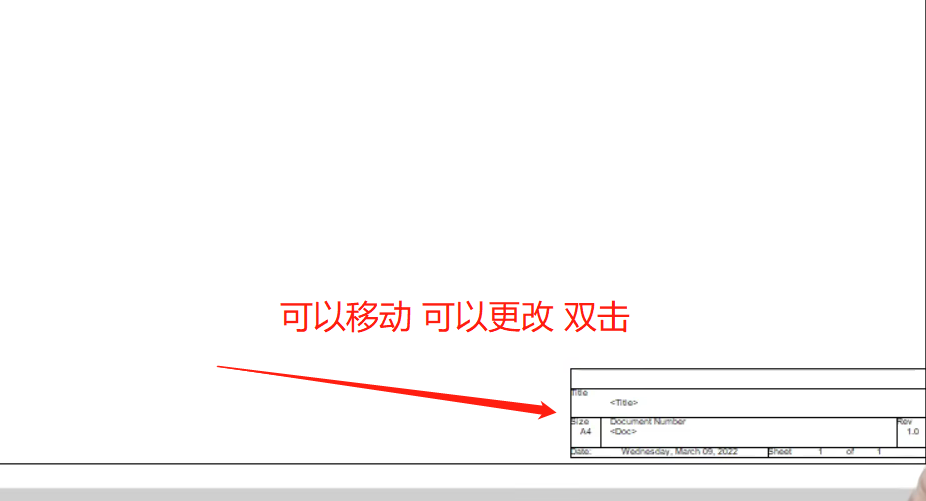

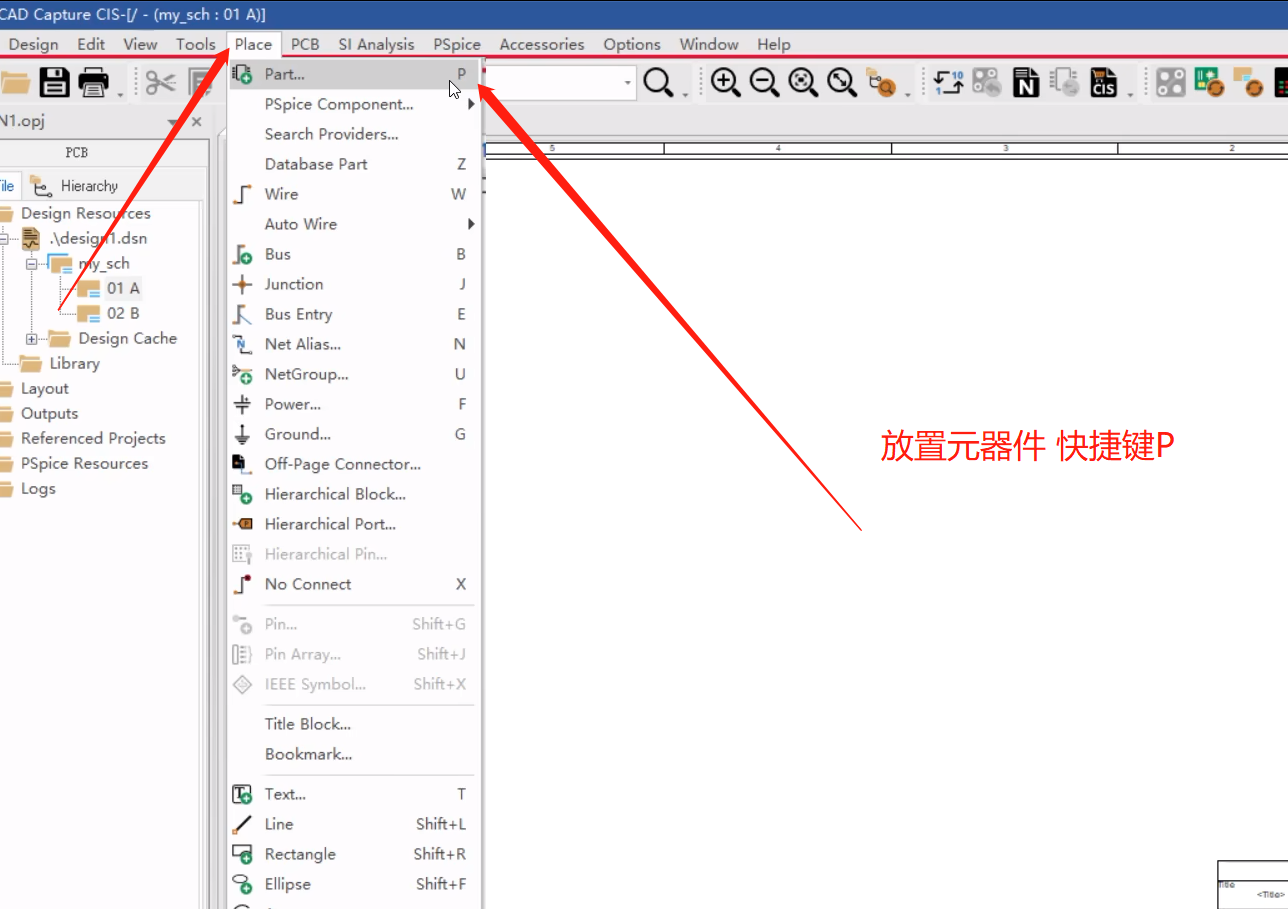

3、原理图添加元器件绘图

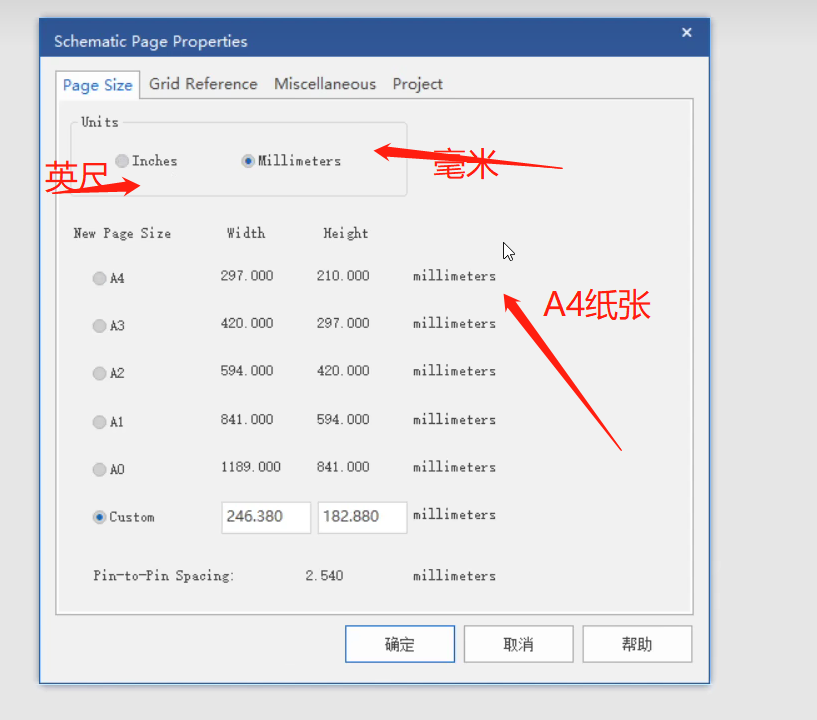

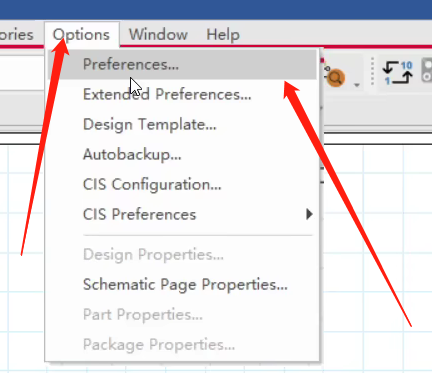

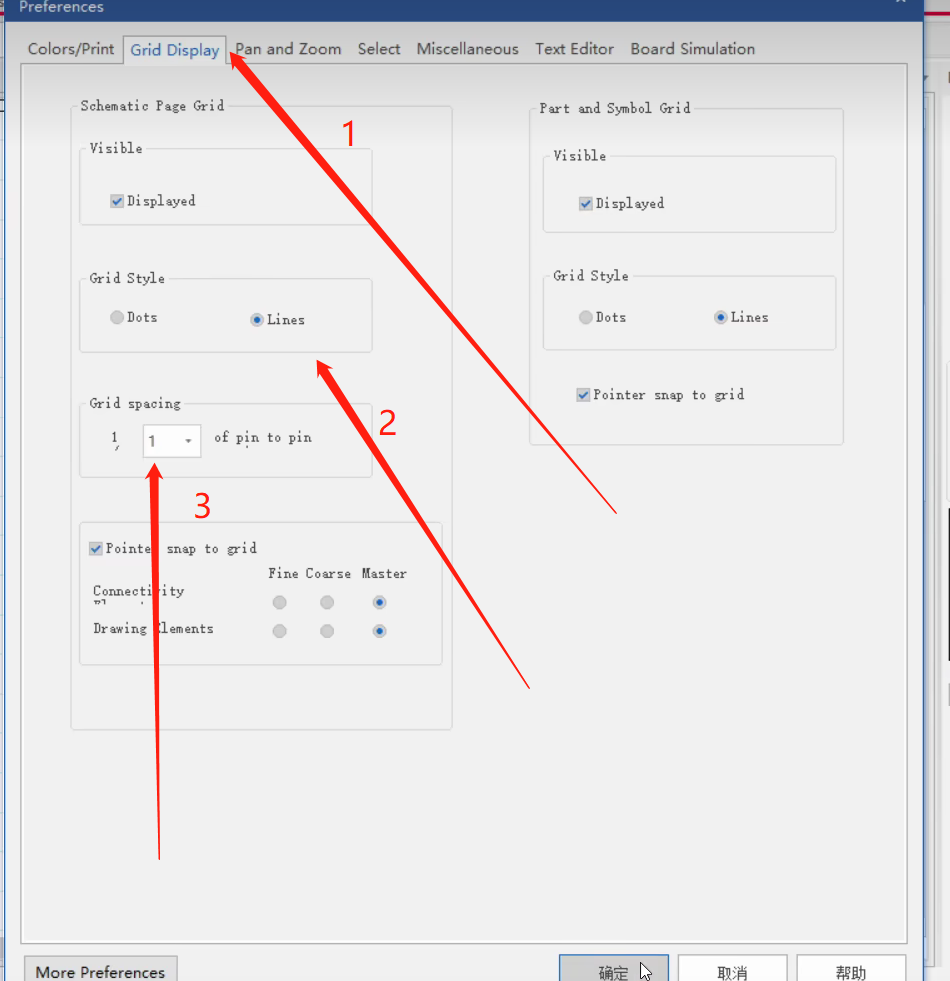

原理图格点设置如下:

4、原理图中的元器件操作

4.1 元器件旋转

- 选中元器件,按快捷键R

- 右击元器件,属性中点击Rotate

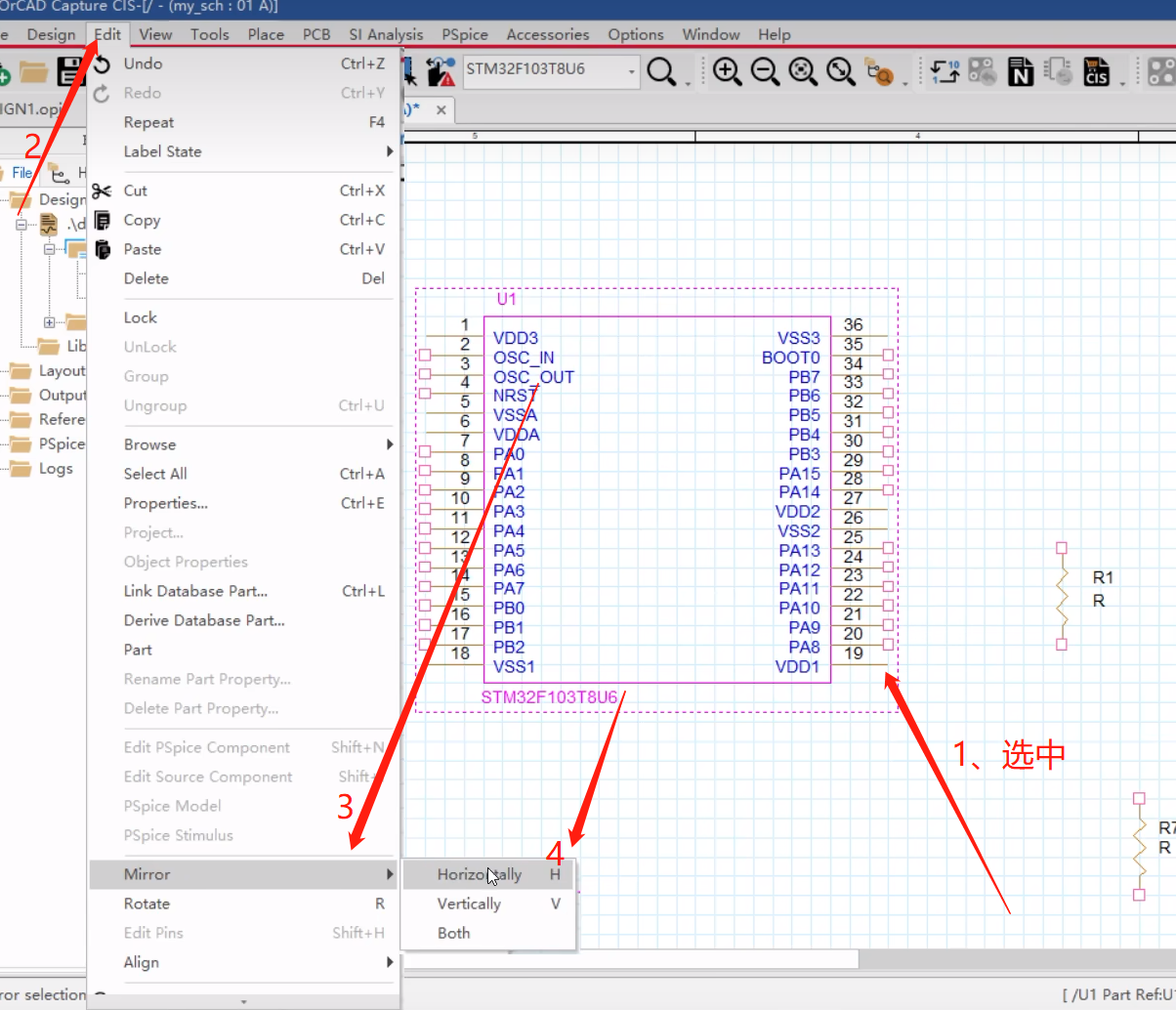

4.2 元器件镜像

- 菜单栏镜像

- 选中元器件,按快捷键H或者V

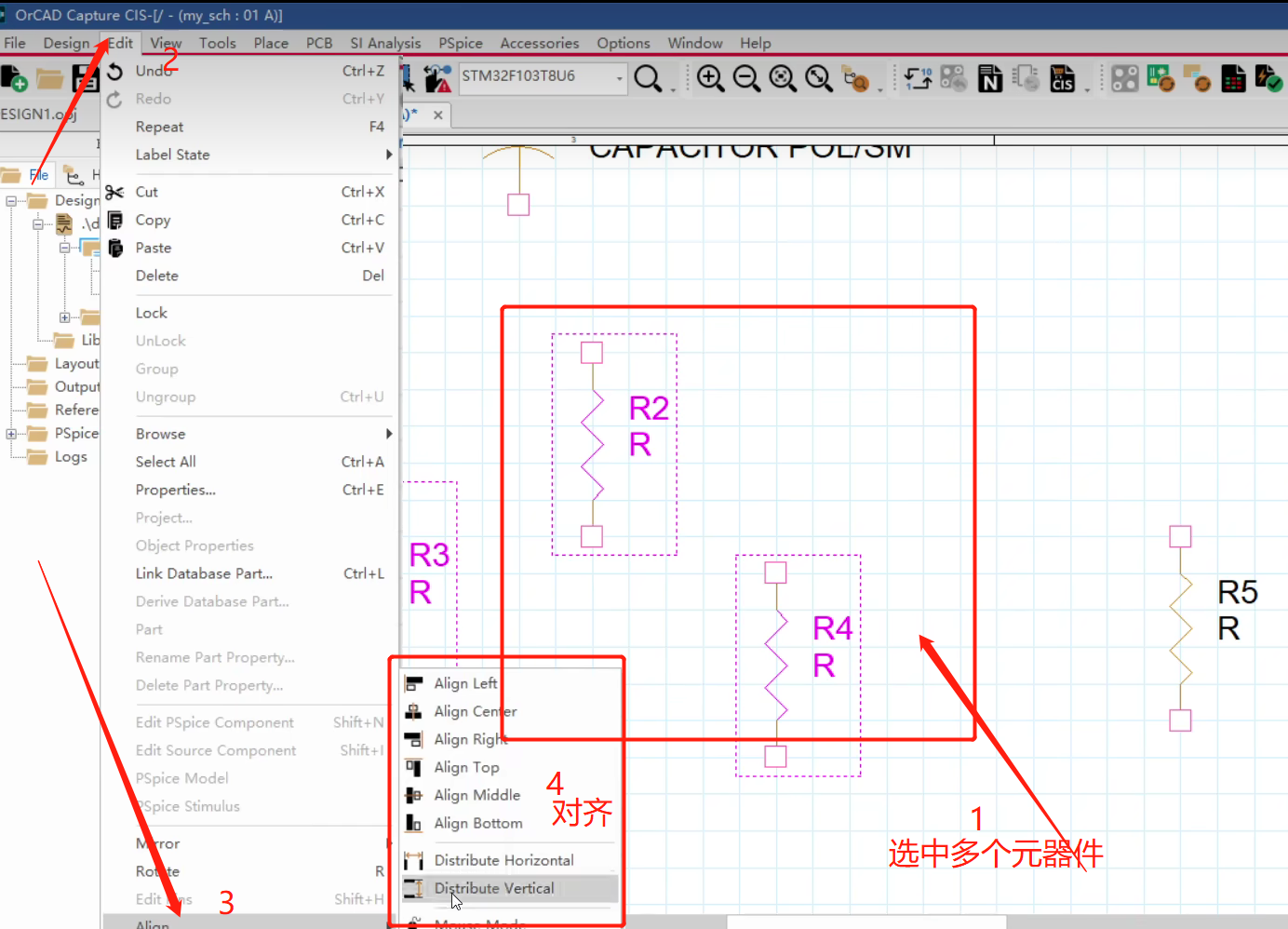

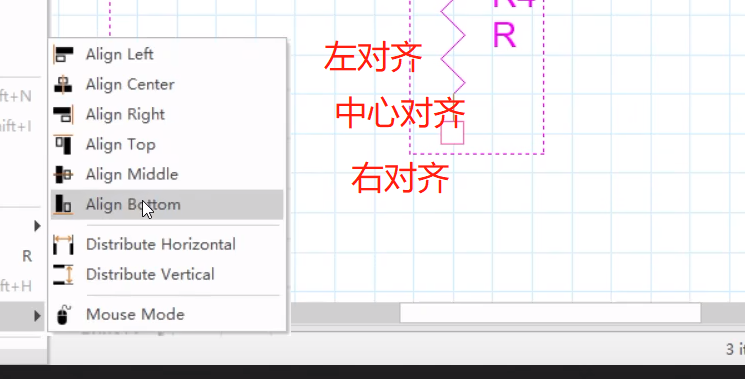

4.3 元器件对齐(PCB使用较多)

- 菜单栏方法对齐

- 快捷键对齐

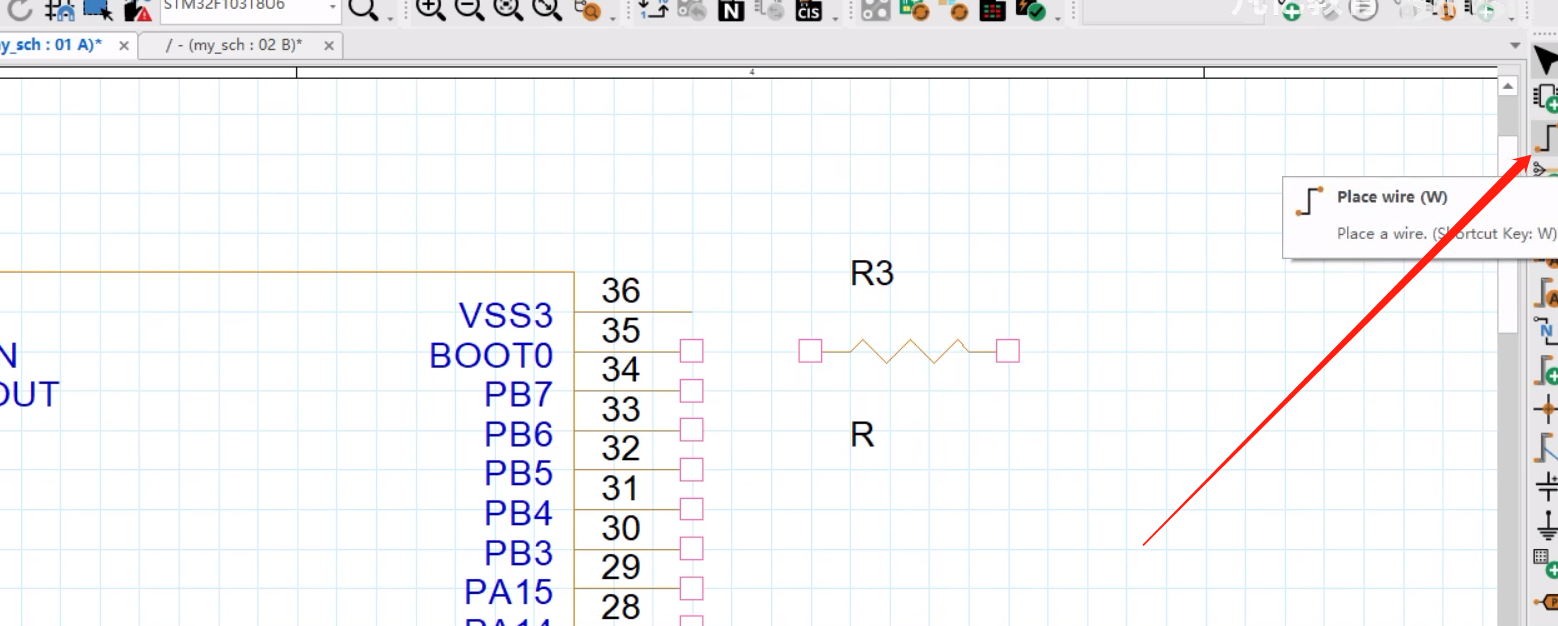

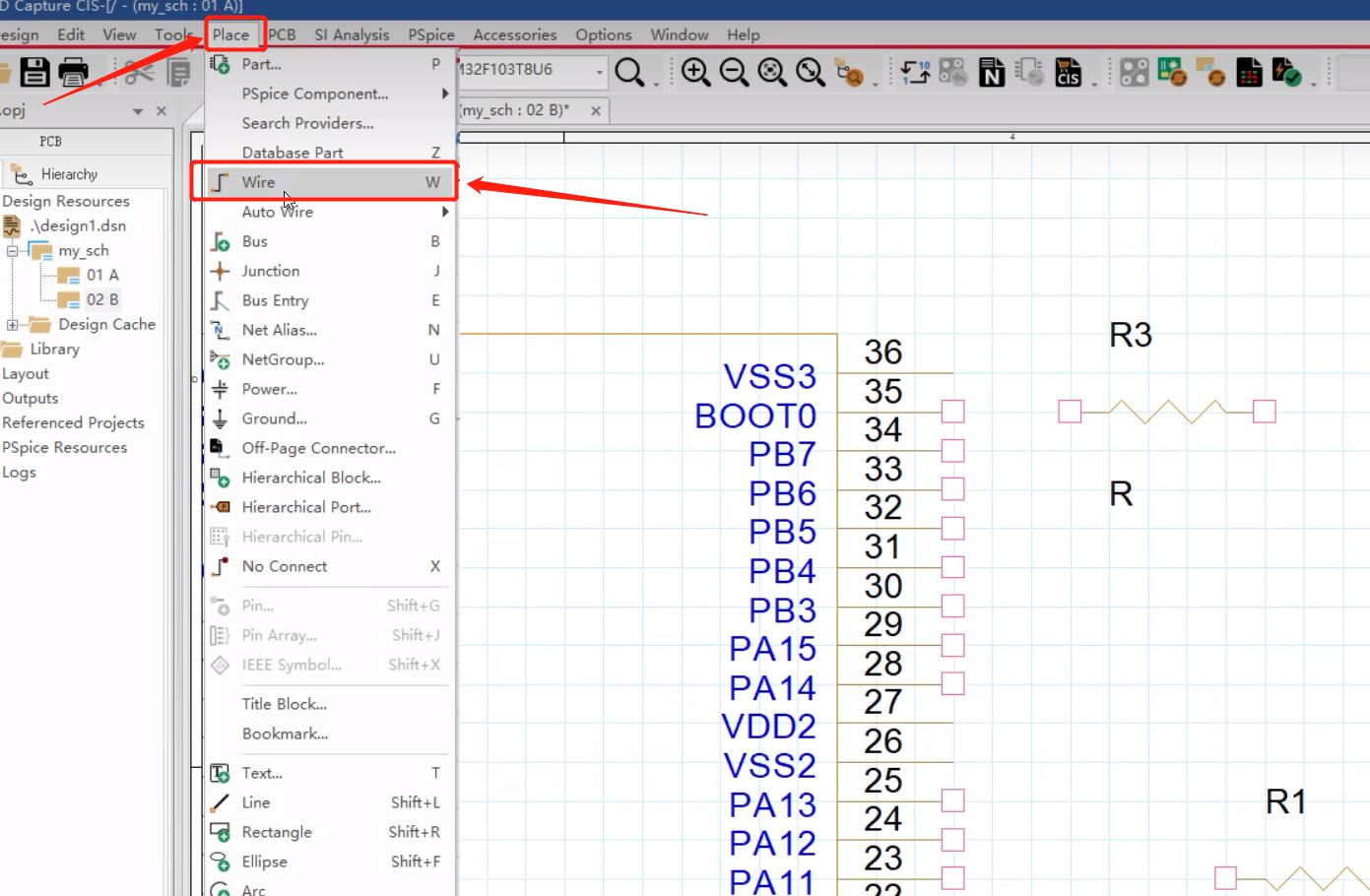

5、原理图中的元器件连线

5.1导线连接

方法一、

方法二、

方法三、快捷键 W

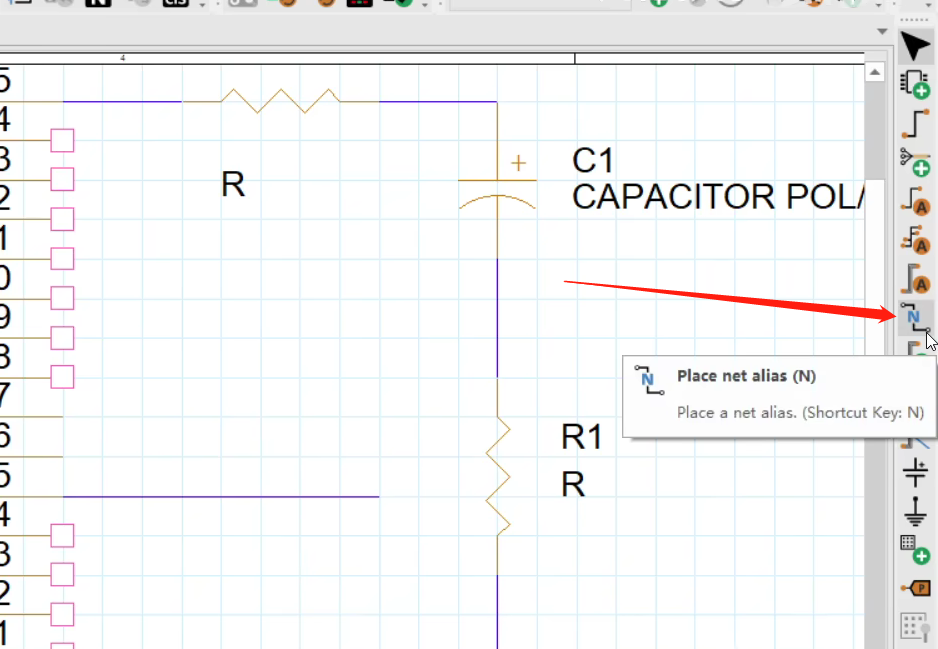

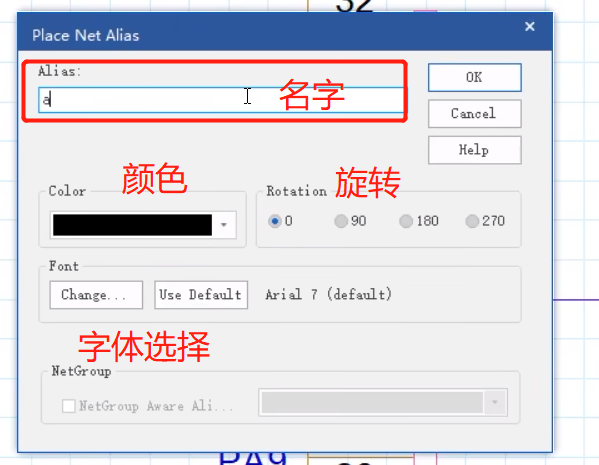

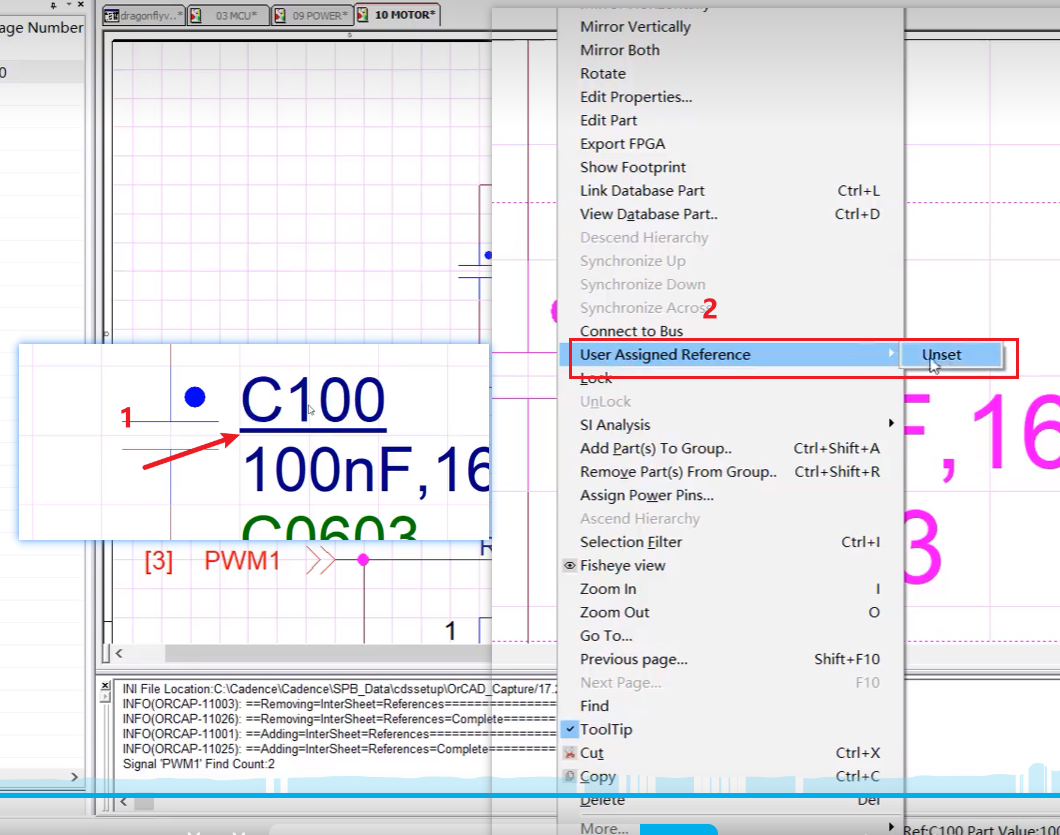

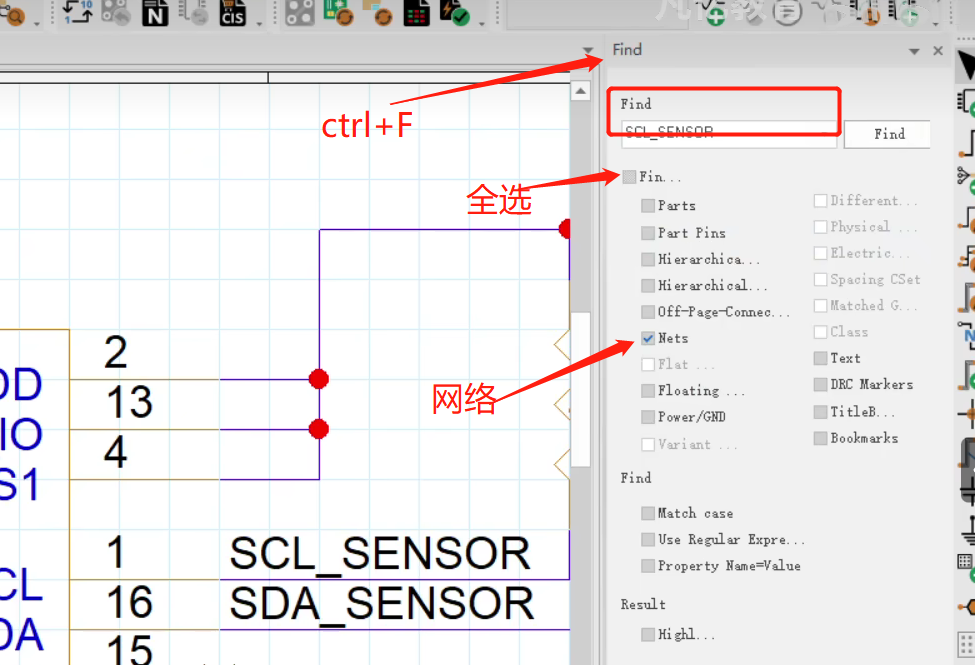

5.2网络标号

方法一、

5.2.1网络标号下的横线去除

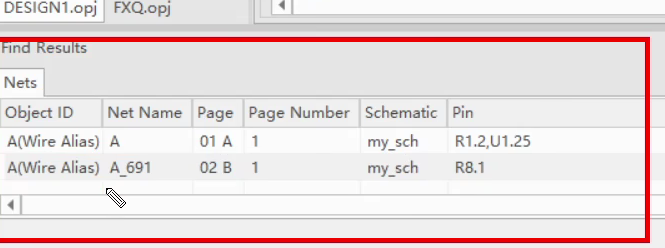

通过网络标号查找联通网络

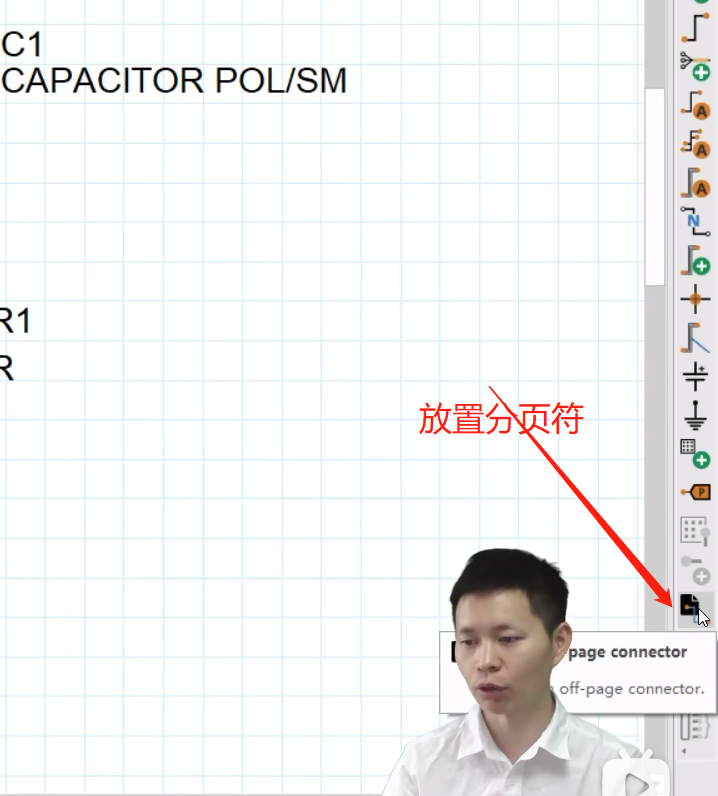

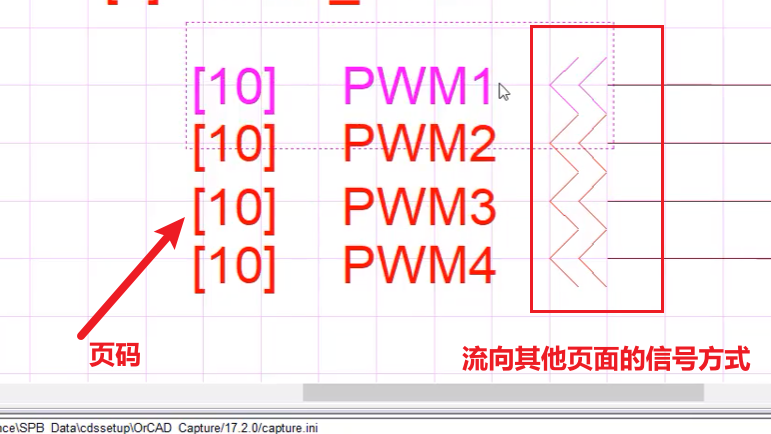

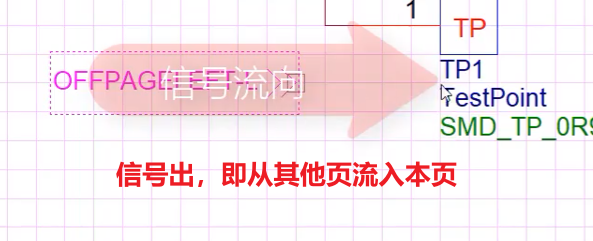

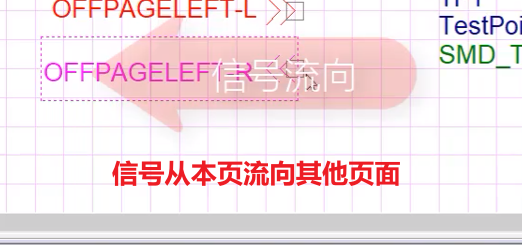

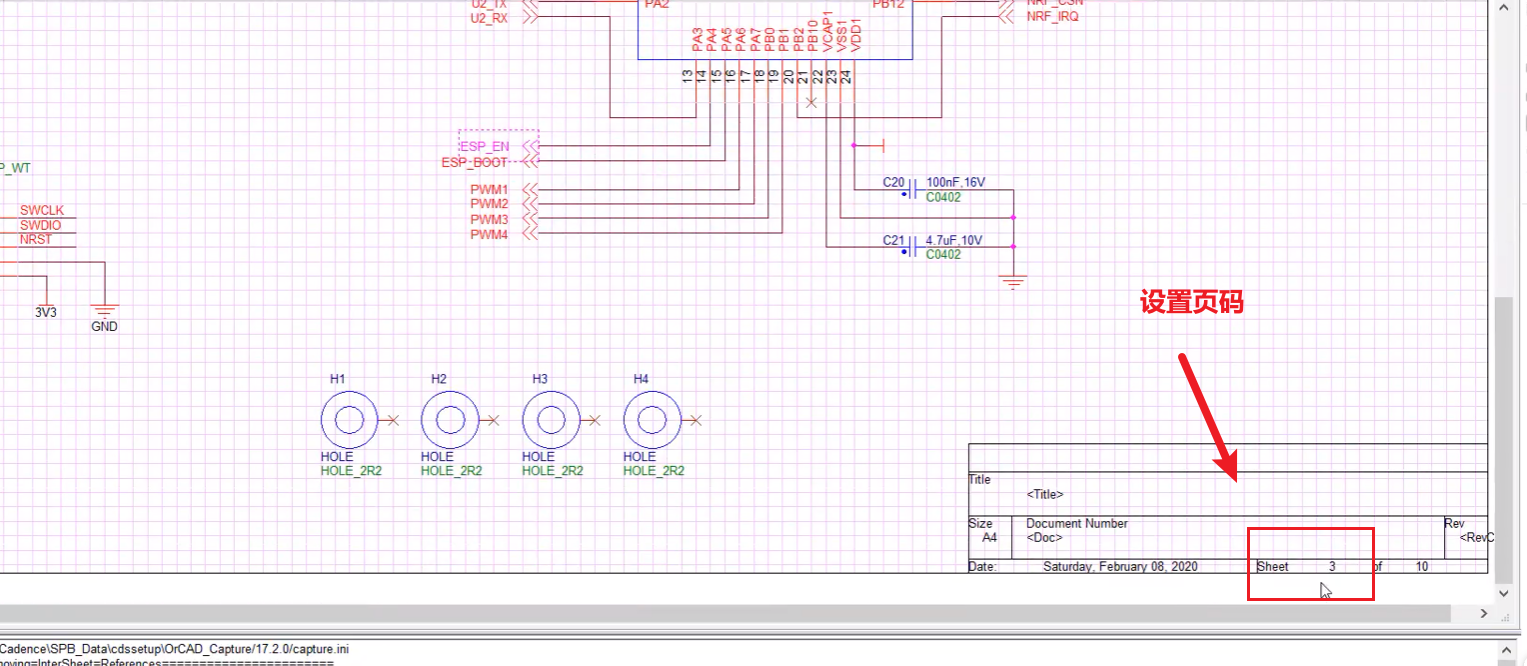

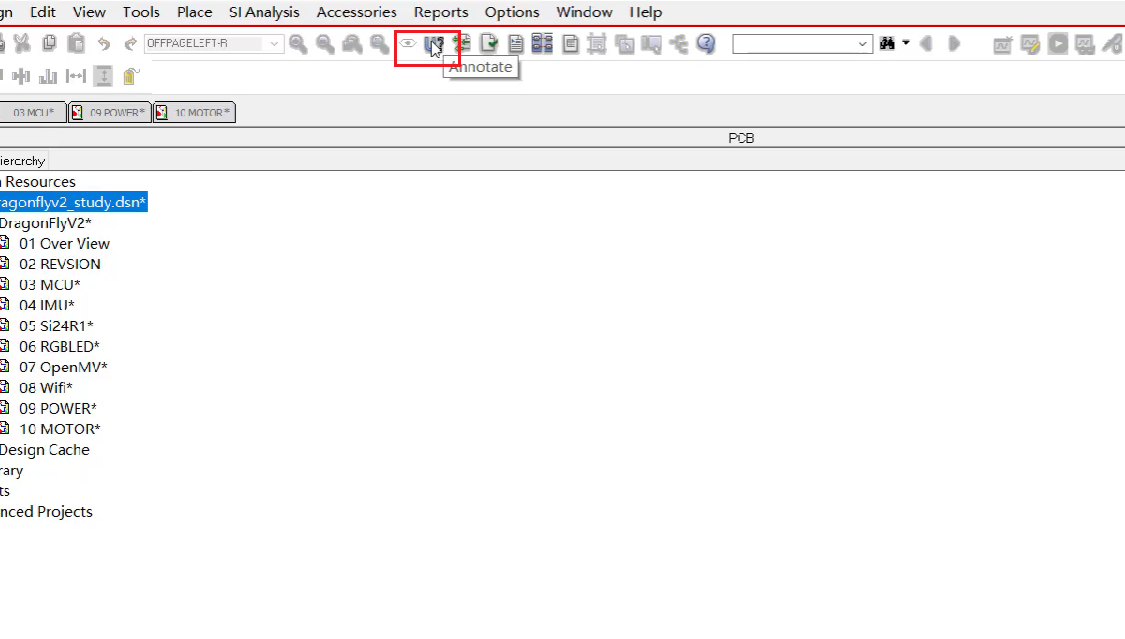

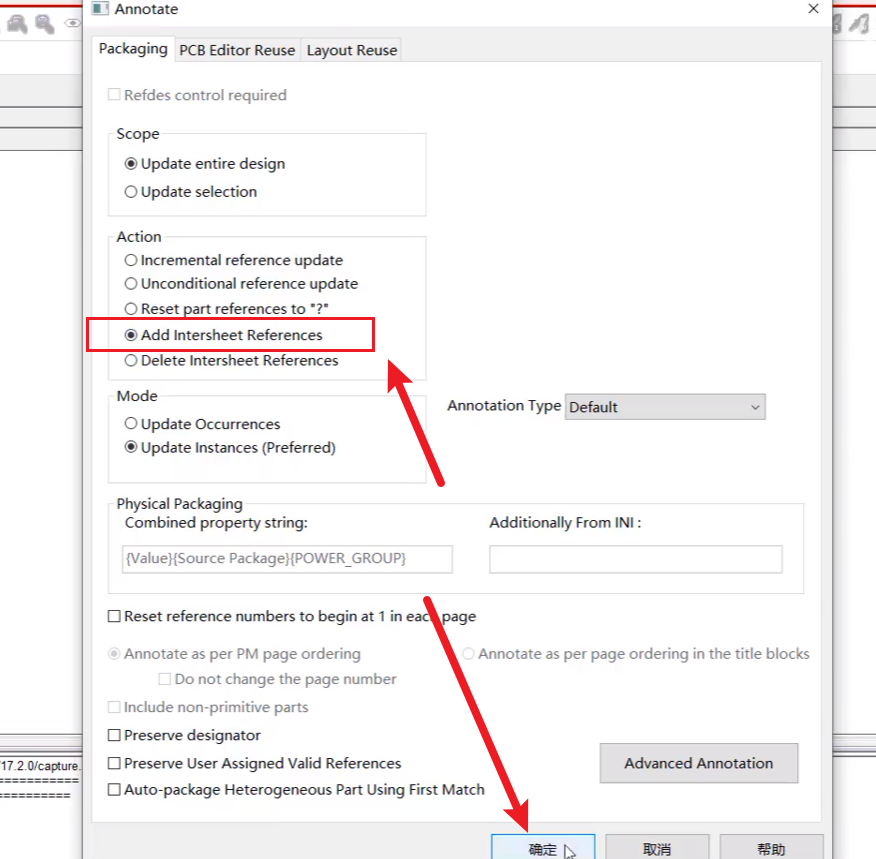

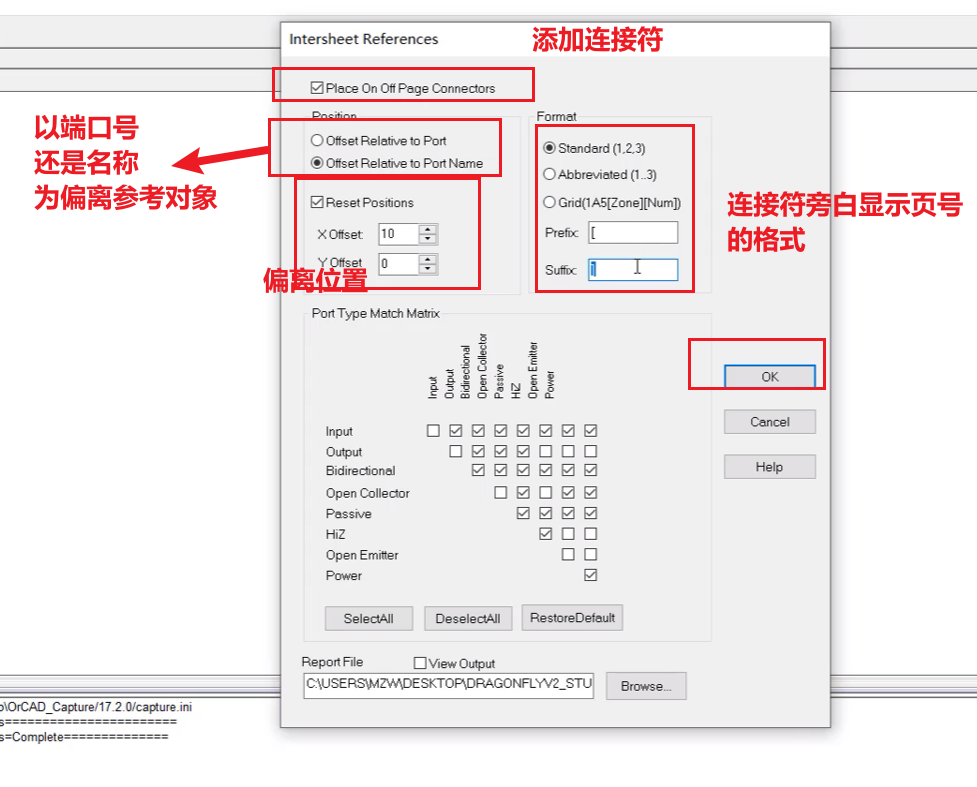

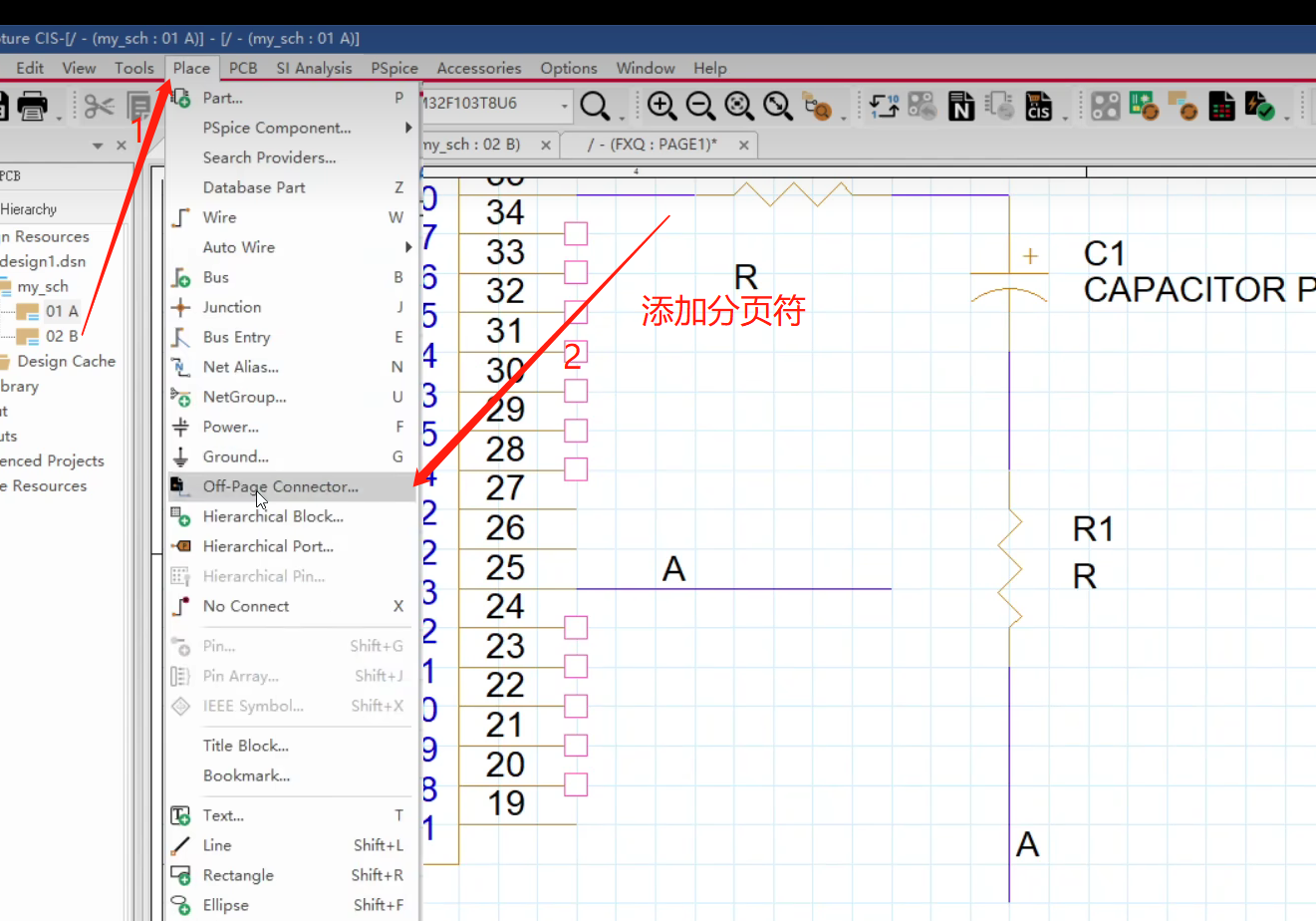

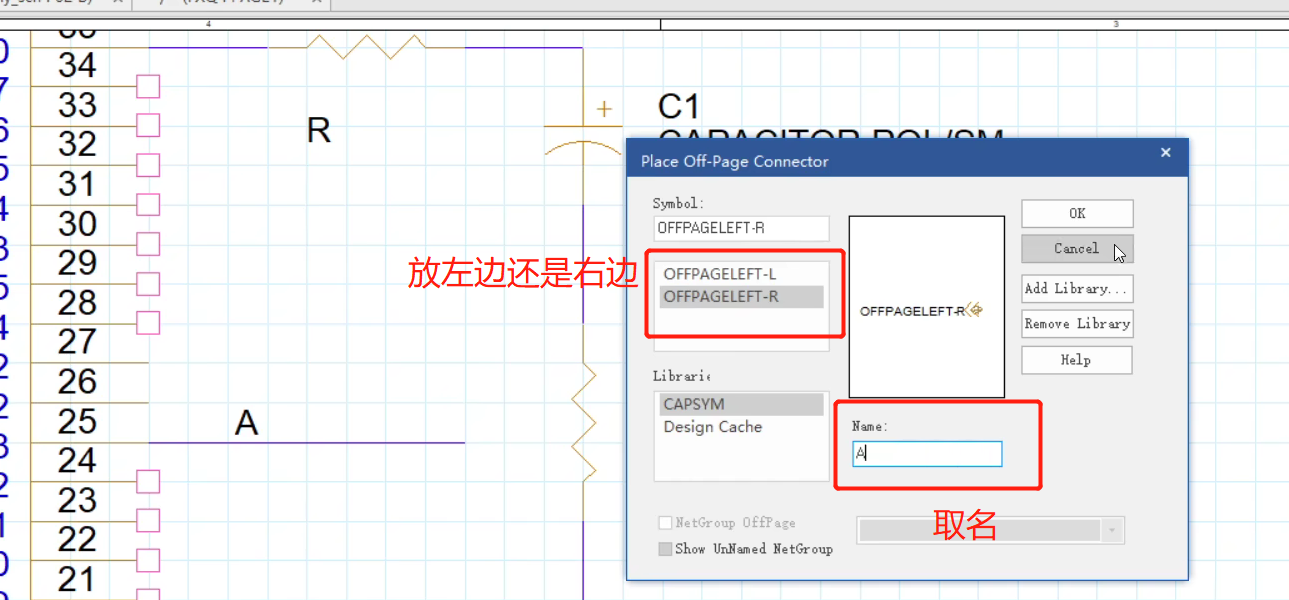

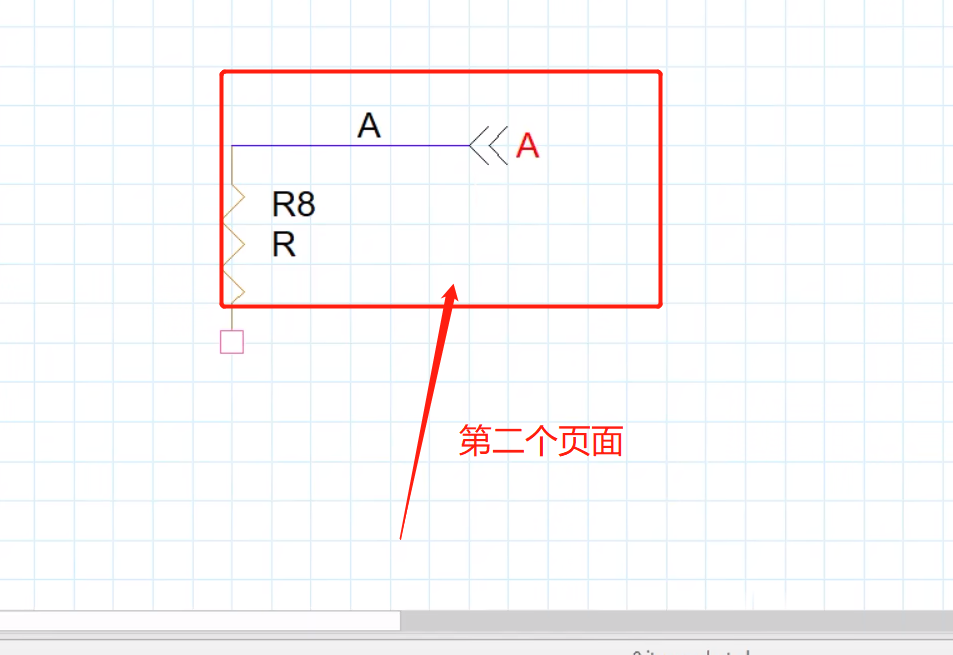

5.3 分页符(连接符)(添加到两个页面上)

未加分页符,不同页面的同一个网络标号没有联通

如何放置分页符????

方法一、

流程:

方法二、

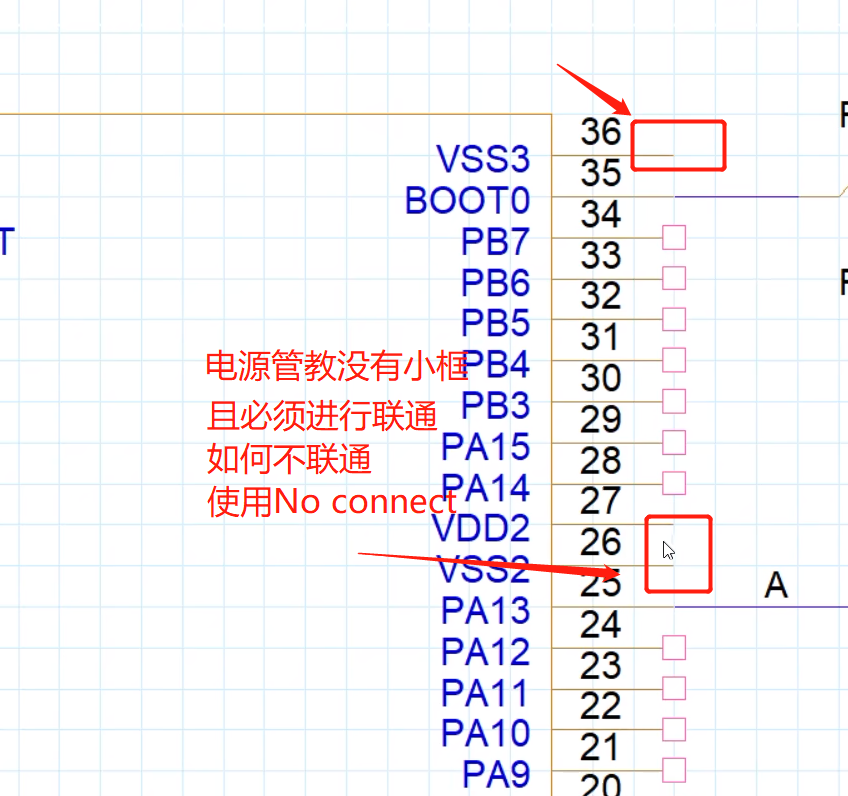

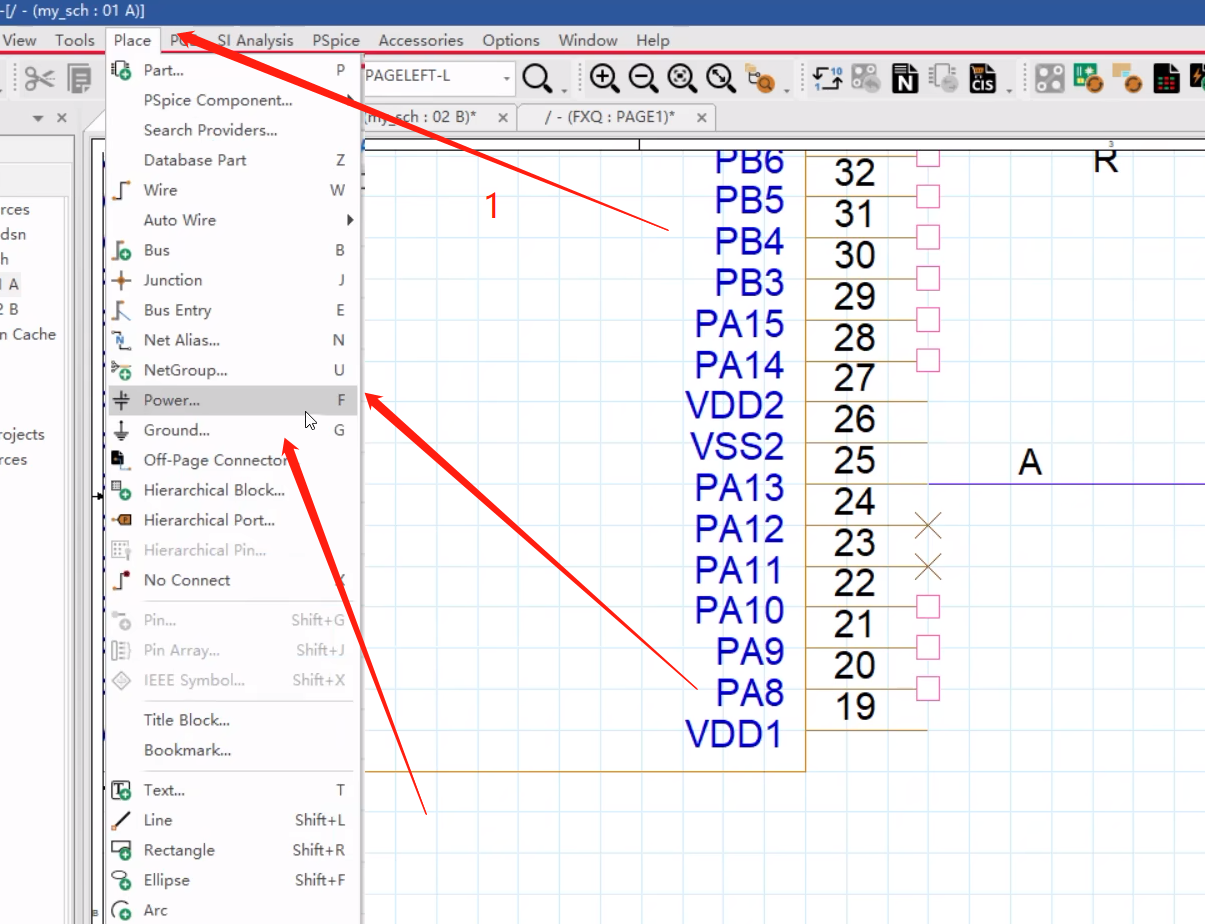

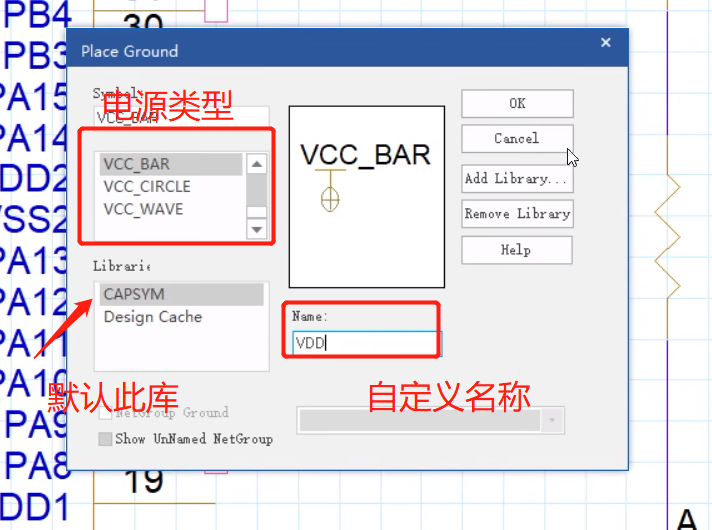

6、原理图中电源和地的联通

- 系统自带电源/地连接符的库,不用添加,直接点击放置电源/地的按钮放置;

- 电源/地是全局变量,不同的页面也可以进行连接,不用添加分页符;

- 自定义电源/地连接符的Name名称,即可将原理图上电源/地全部联通

电源管教是必须进行联通的,电源管脚不能放No Connect符号,上图中的文字错误

方法一、

方法二、快捷键

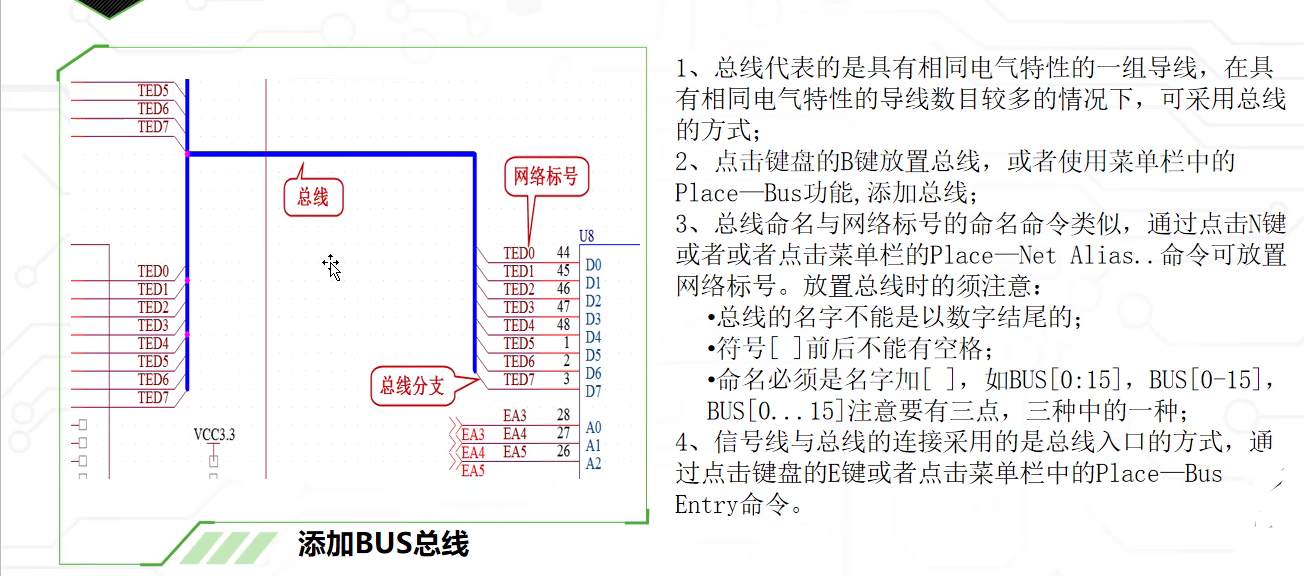

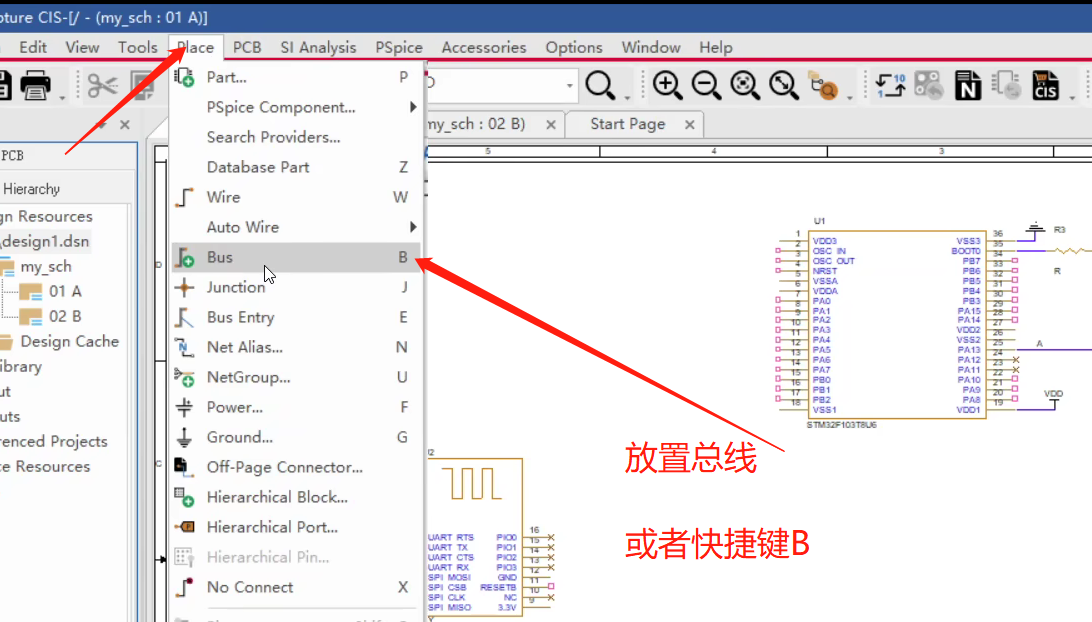

7、原理图中添加BUS

7.1 放置总线

点击键盘的B键放置总线,或者使用菜单栏中的Place一Bus功能,添加总线,绘制完成后点击右键,点击end wire

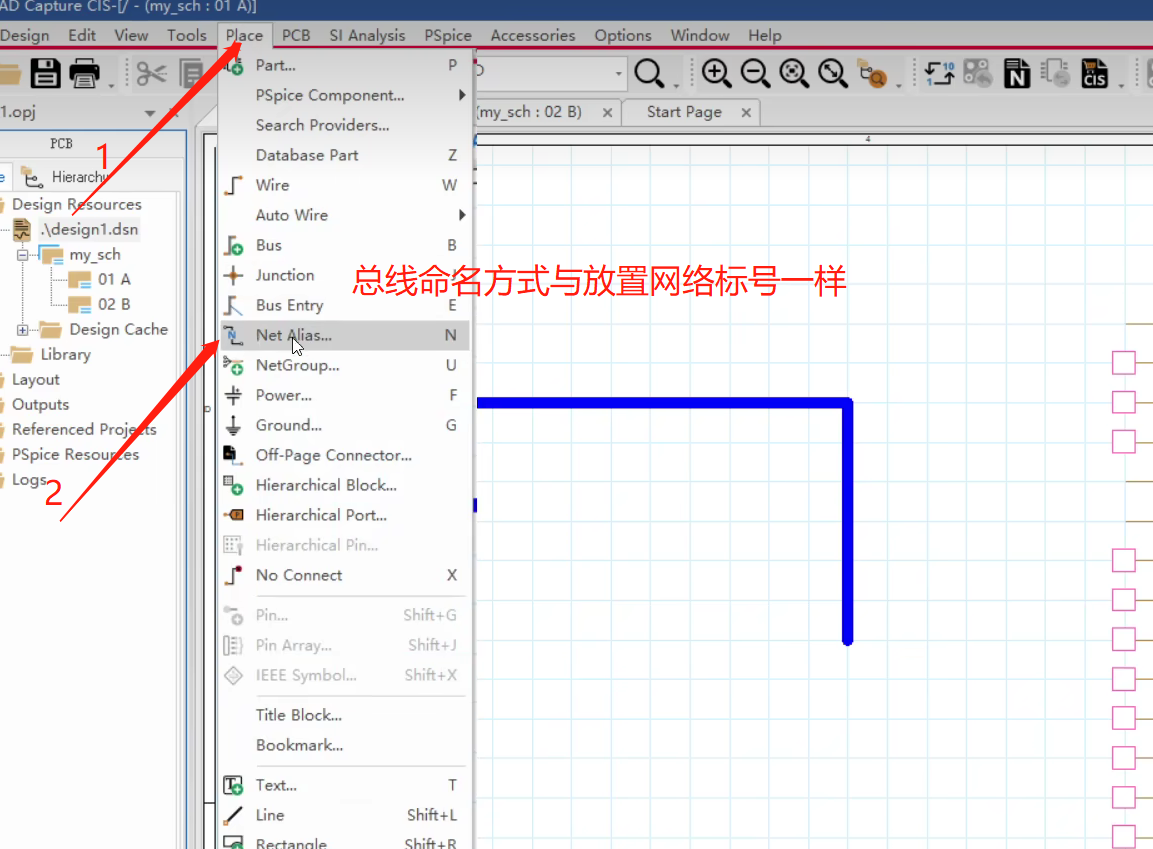

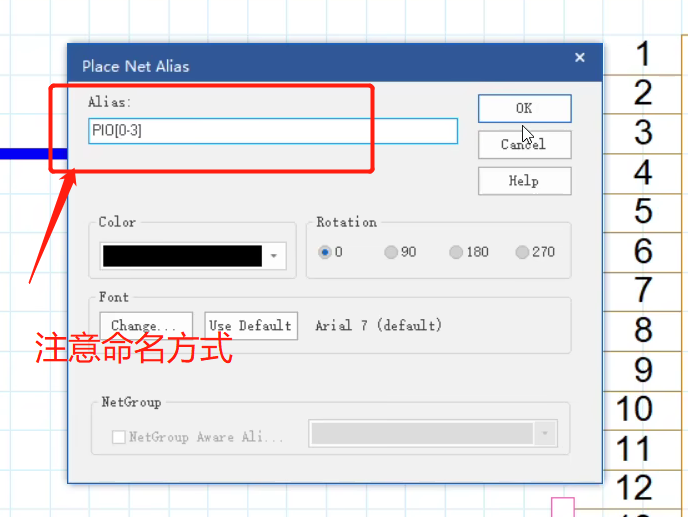

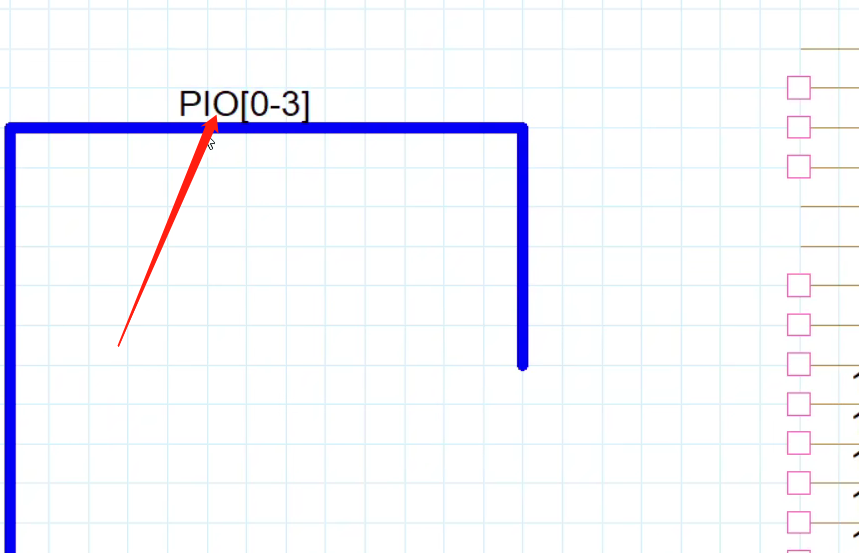

7.2 总线命名

总线命名与网络标号的命名命令类似,通过点击N键或者或者点击菜单栏的Place一Net Alias

1. 总线的名字不能是以数字结尾的

2. 符号[]前后不能有空格;

3. 命名必须是名字加[ ],如BUS[O:15],BUS[0-15],BUS[0...15] 注意要有三点,三种中的一种;

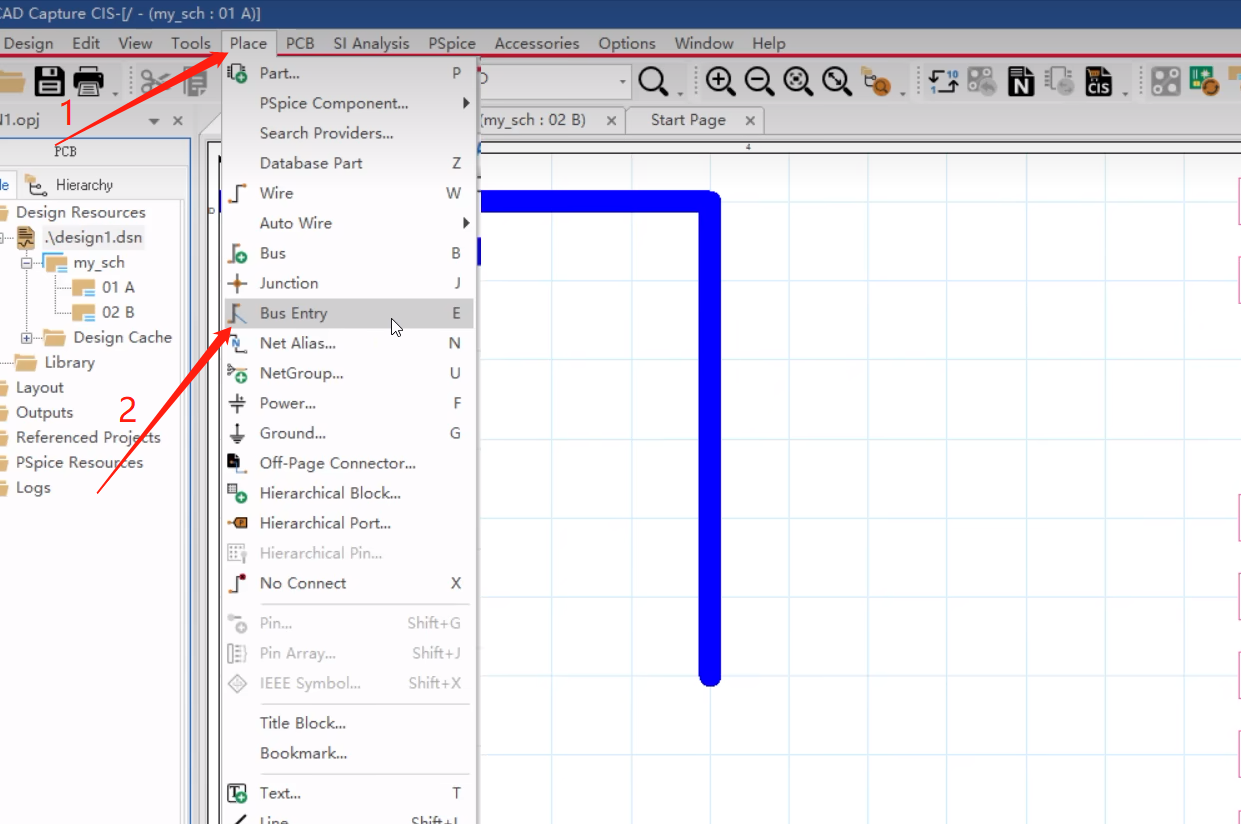

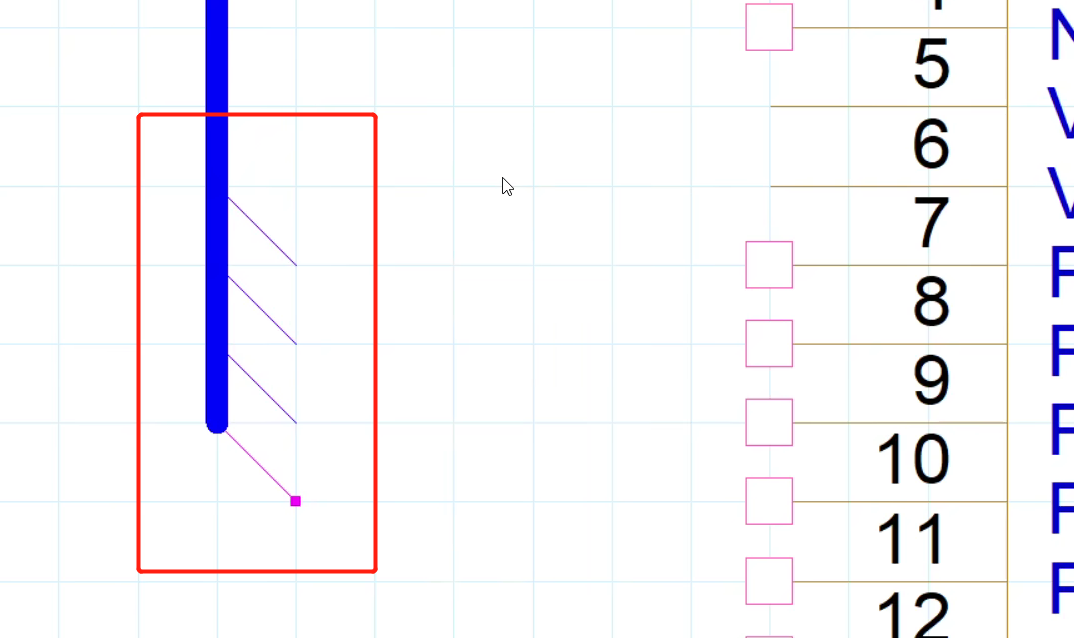

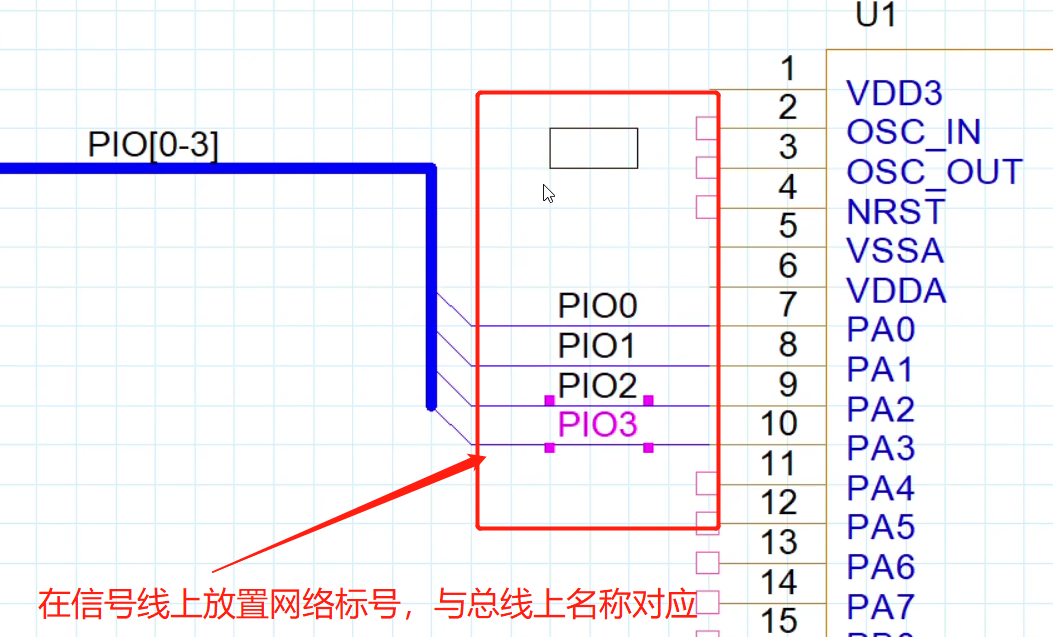

7.3 信号线与总线的连接

信号线与总线的连接采用的是总线入口的方式,通过点击键盘的E键或者点击菜单栏中的Place一BusEntry命令

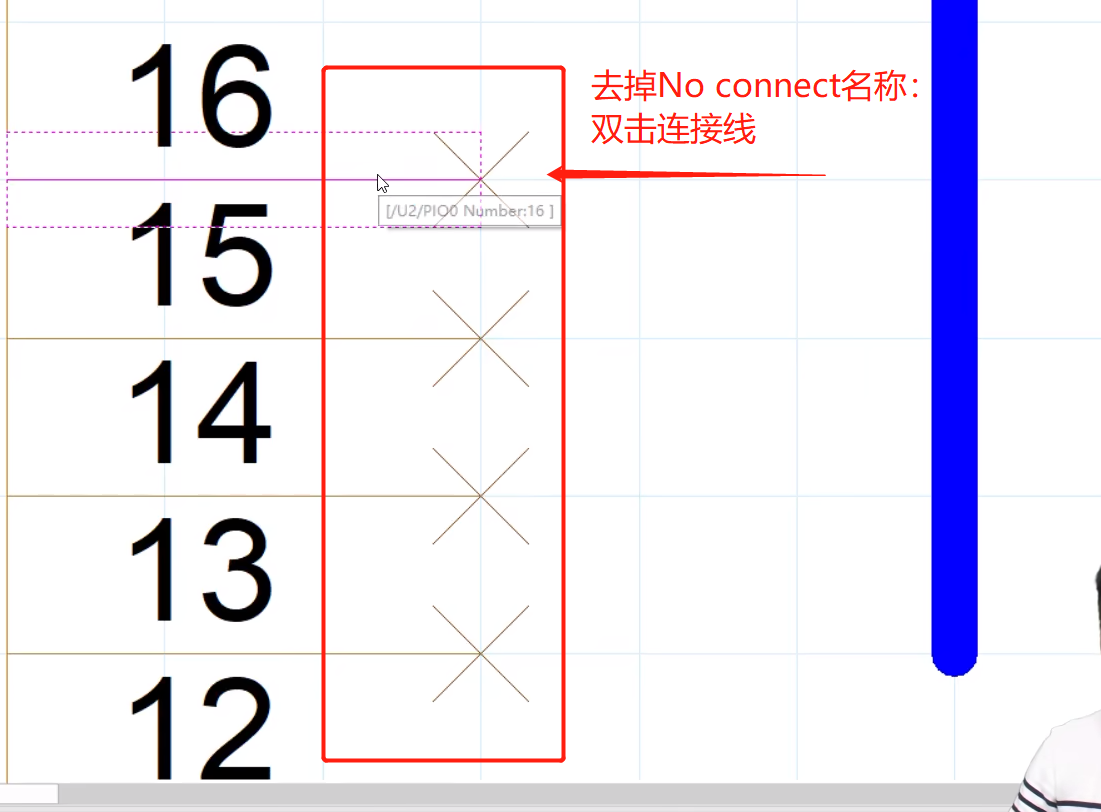

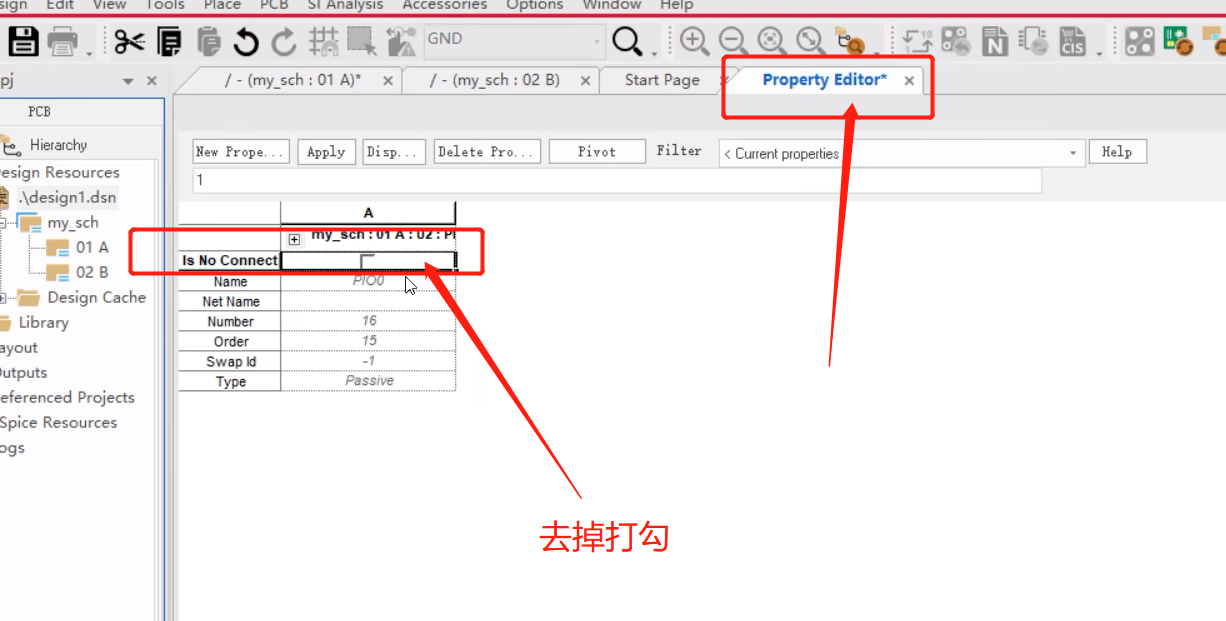

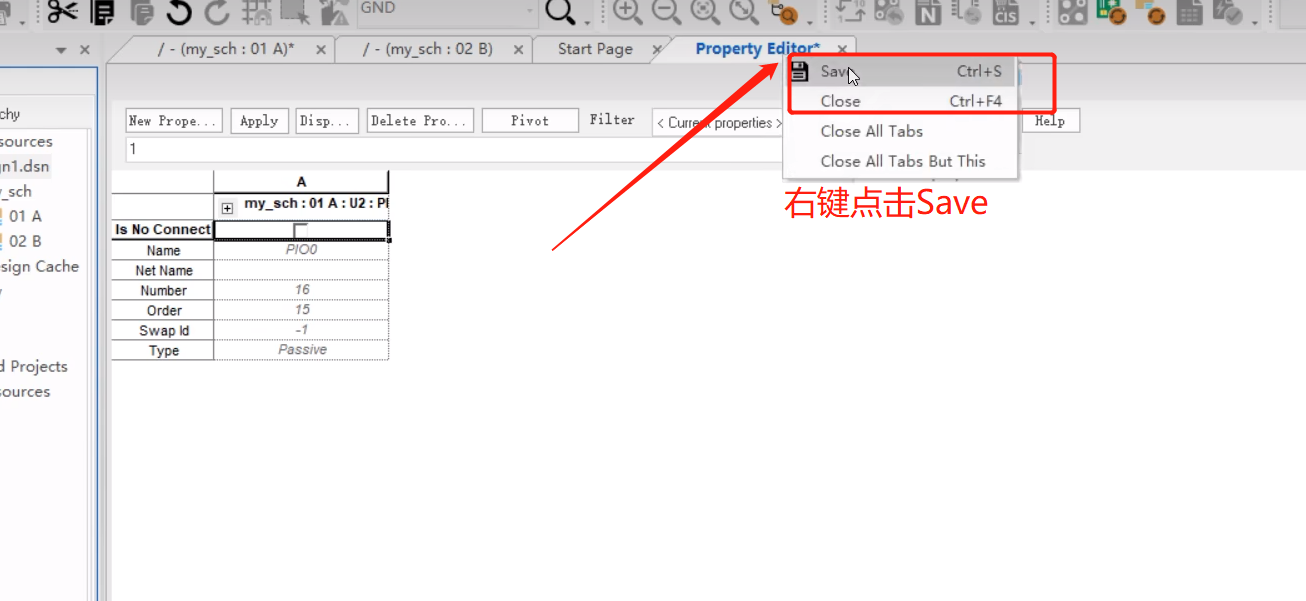

去掉No connect名称方法

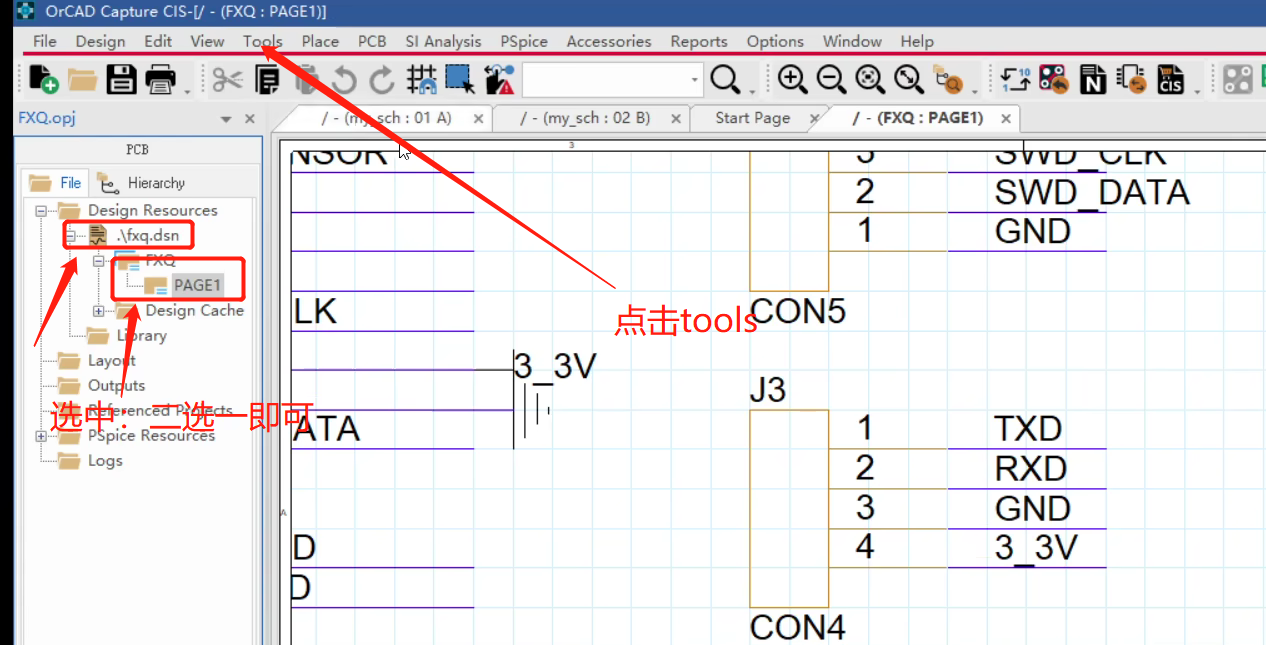

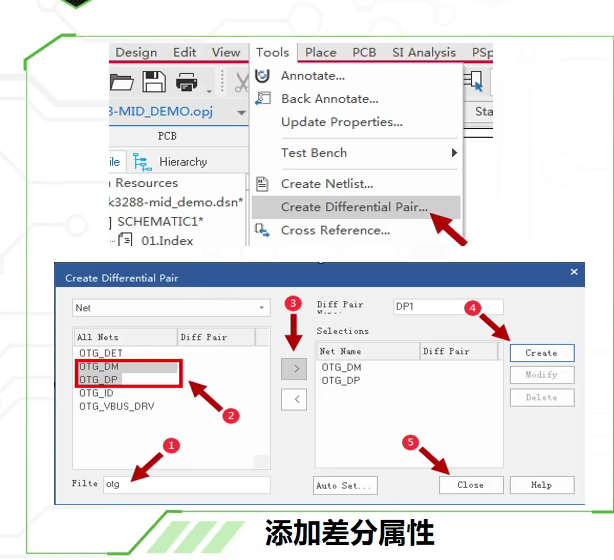

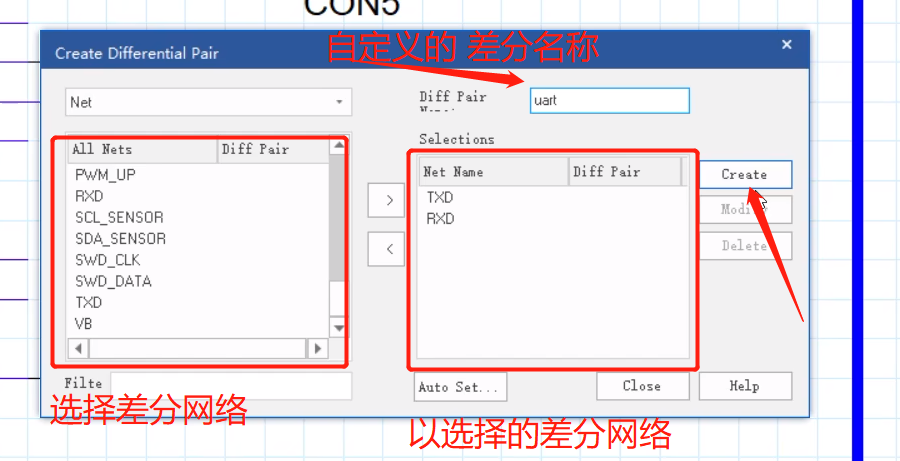

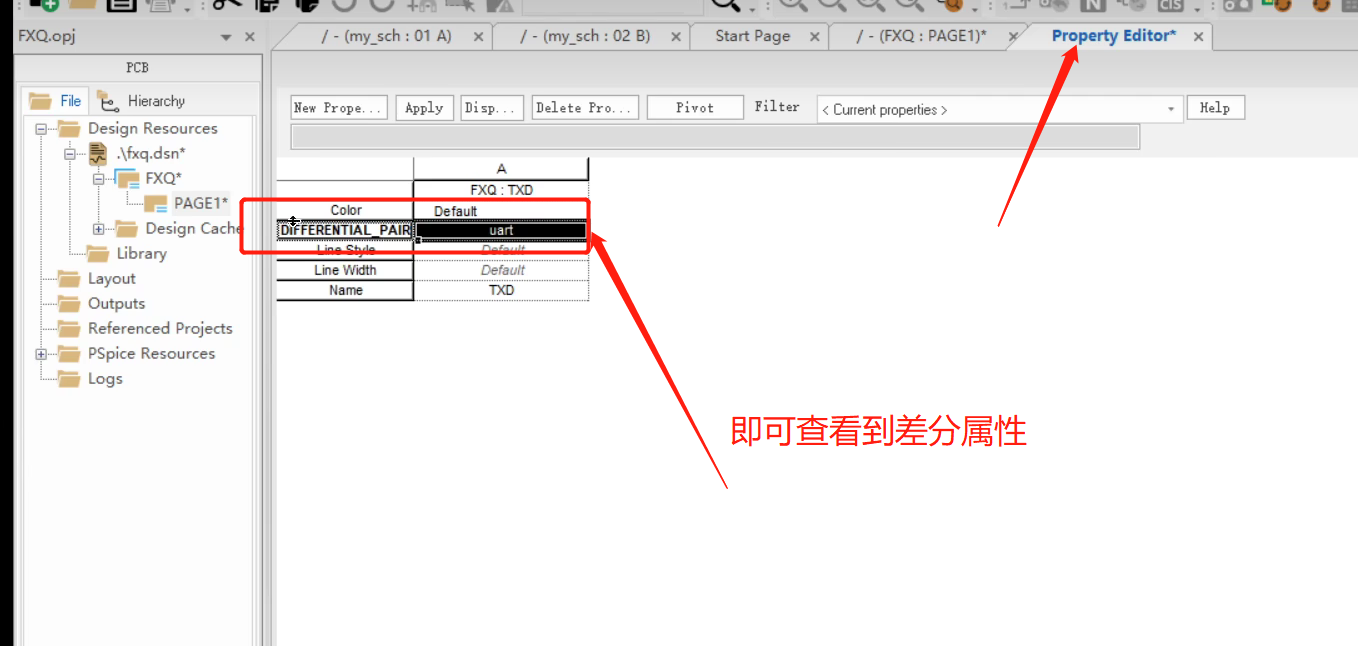

8、原理图中添加差分属性

1、鼠标左键单击选中一页原理图,然后执行菜单命令“Tools-Create Differential Pair...

2、在弹出的Create Differential Pair窗口中查找需要设置的网络名并添加到Selections中;

3、在D箭头处输入需要查找的大概网络名:

4、在@箭头处选择具体对应的网络名;

5、点击图箭头处的符号即可添加到Selections中,

6、点击4箭头处的Create即可自动创建好差分类

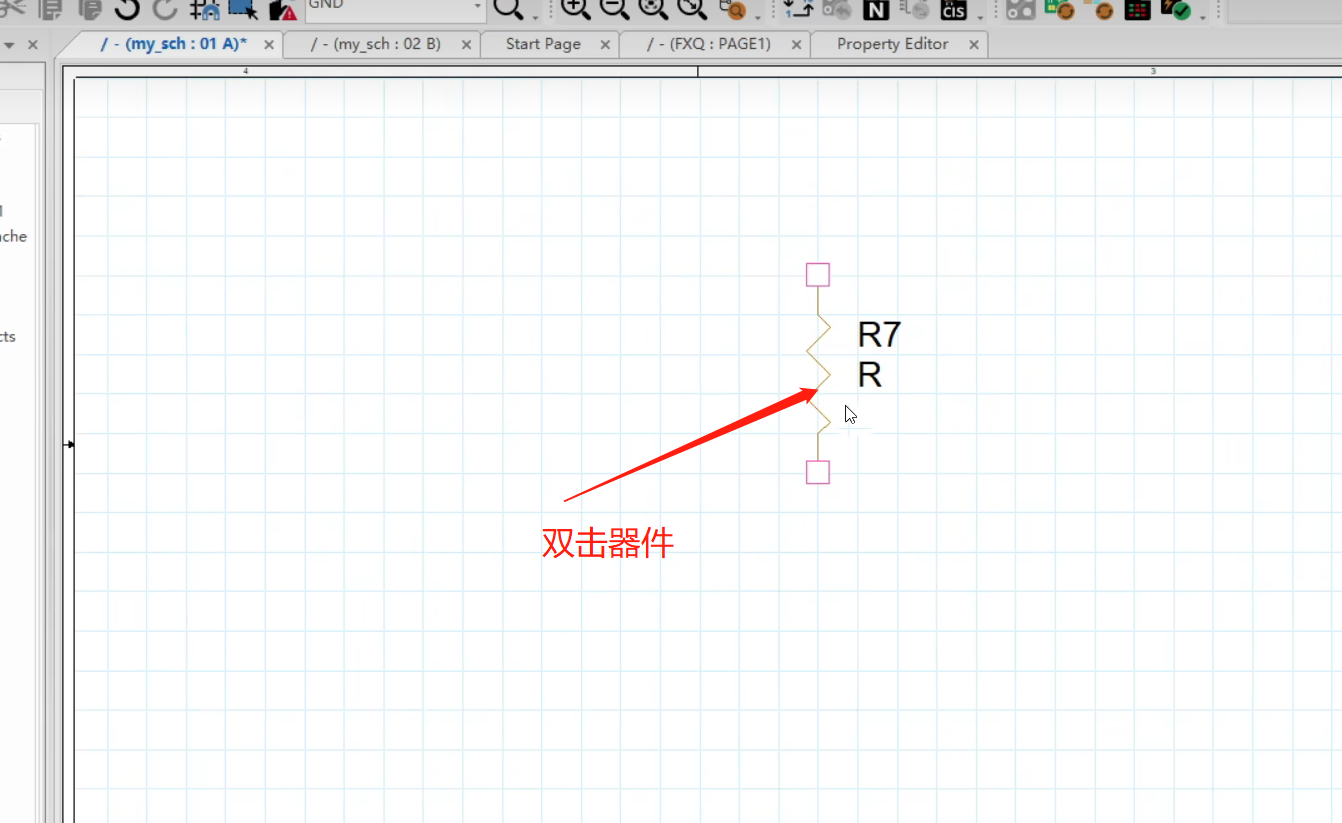

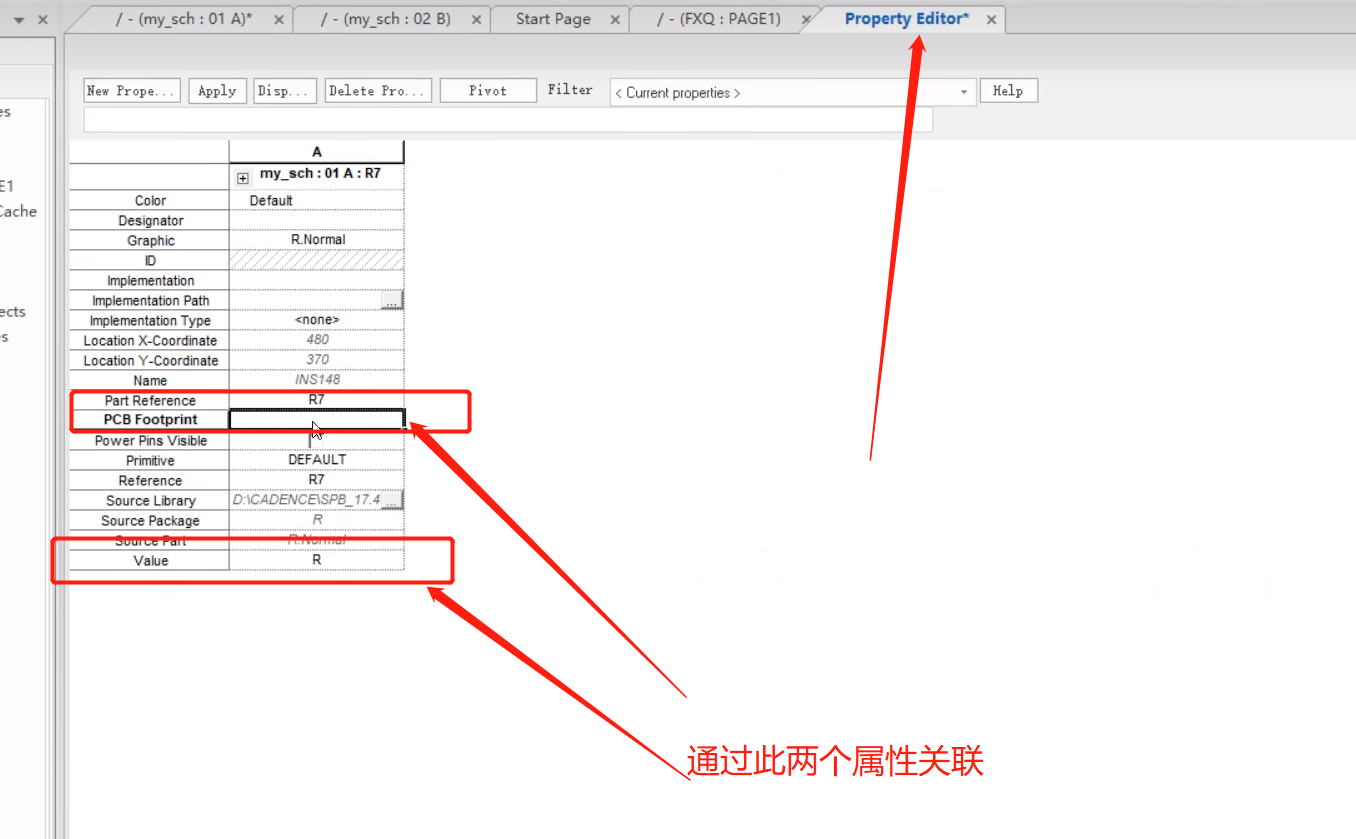

9、原理图中的元器件封装指定

footprint的封装名要与PCB中的库的封装名一致

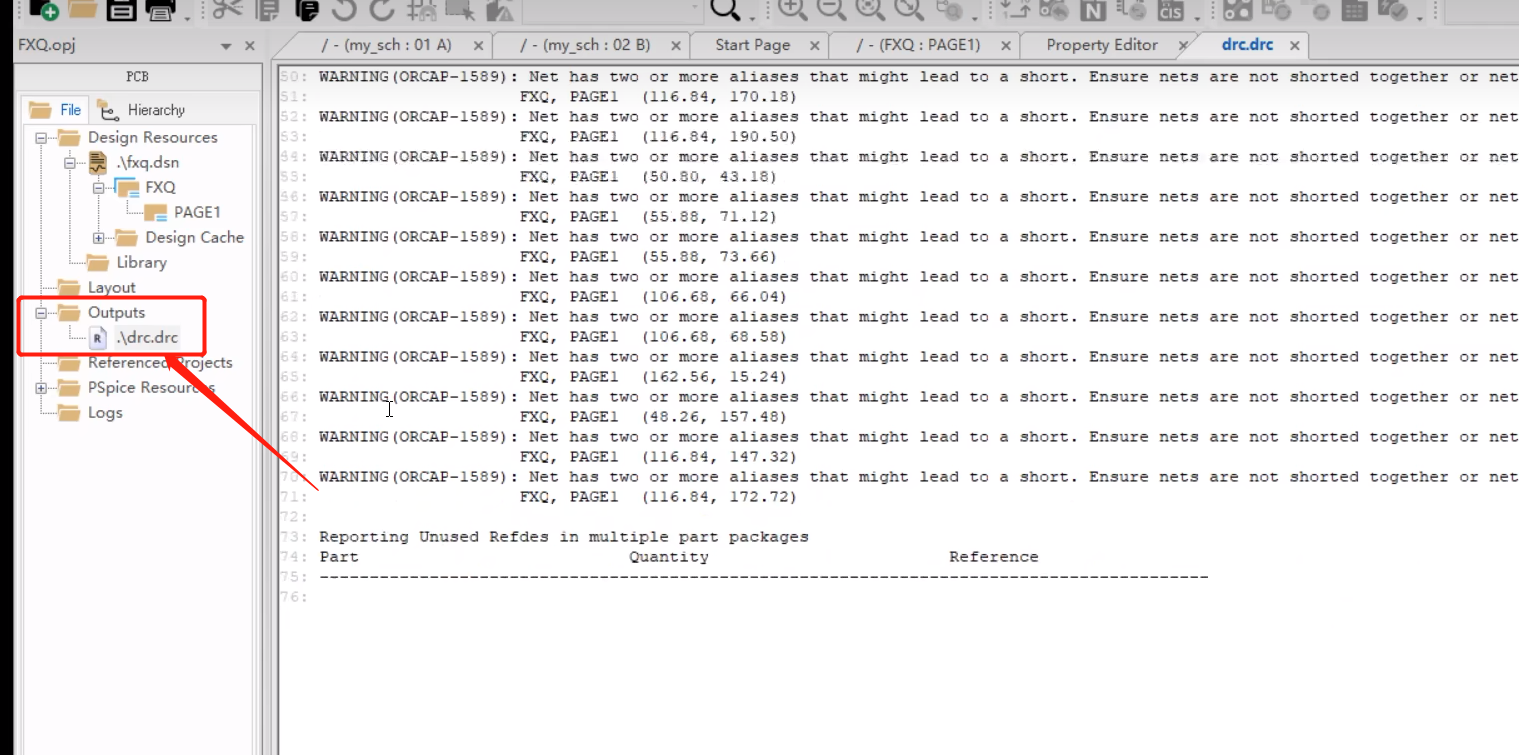

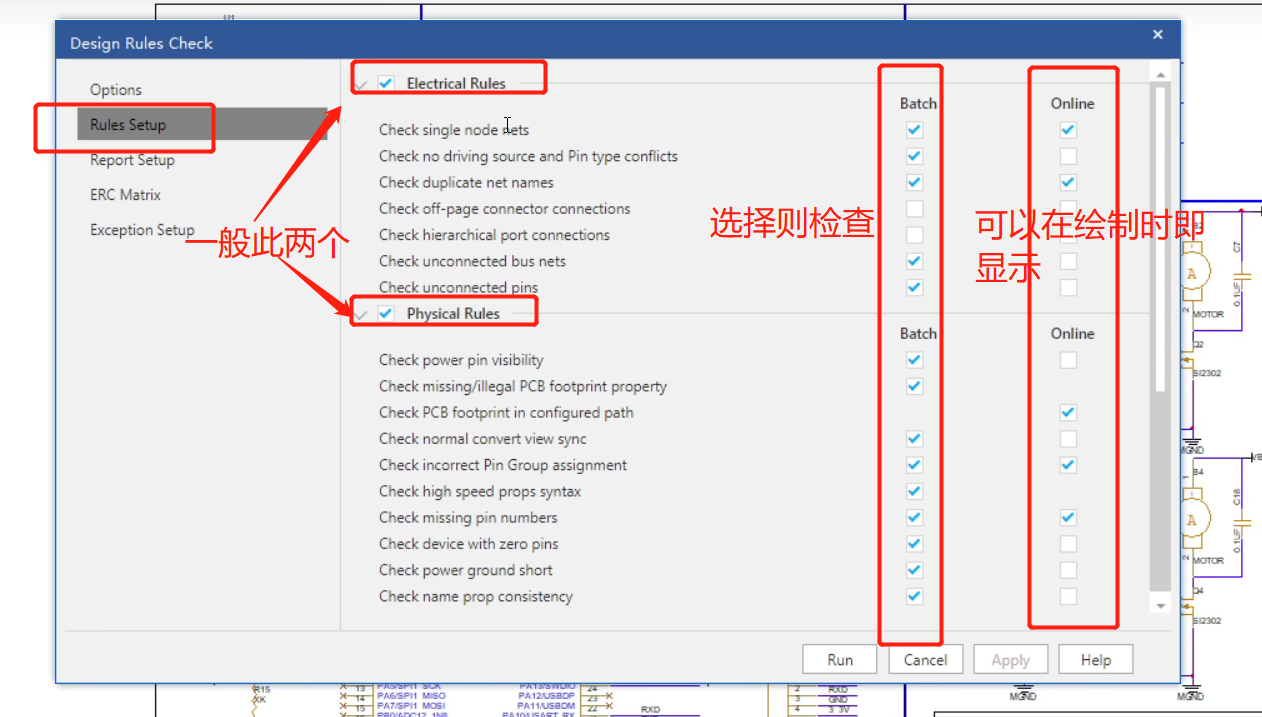

10、DRC检查工具

生成的报告的目录不能放在中文下面

- Check single node nets: 检查设计中的单端网络;

- Check no driving source and pin type: 检查器件属性无源管脚与有源管脚的连接是否正确

- Check duplicate net name : 检查重复的网络名称:

- Check off-page connector connect: 检测分页图纸间接口的连接性

- Check hierarchical port connection: 检测阶层端口的连接性:

- Check unconnected bus net: 检测没有连接的总线网络:

- unconnected pins: 检查没有连接的管脚:

- Check power pin visible: 检测电源属性的管脚是否显示了管脚名称与编号:

- CheckCheck missing/illegal PCB Footprint:检测封装名称是否填写。是否含有非法字符:

- Check Normal convert view system: 检测一个部件的正常视图上的pin号是否与转换视图上的pin号不同:

- Check incorrect pin group assignment: 检查同一个Pin Group的所有插脚是否有相同的类型;

- Check high speed props syntax: 在设计中检查网络高速属性的语法是否正确;

- Check missing pin number: 检测缺失管脚编号的管脚:

- Check device with zero pins::检测设计中是否含有零宽度的管脚:

- Check power ground short: 检测一个Part内部的电源网络名称是否有两个不同的网络标号名称

- Check Name Prop consistency: 检测层次原理结构中是否含有相同的网络名称:

- Report all net name: 报告所有网络的名称:

- Report off-grid object: 报告不在格点上是器件:

- Report hierarchical ports and off-page connection:T报告阶层端口和分页图纸间接口的连接

- Report Misleading Tap Connection: 报告易误解的连接。

- Report Visible unconnected power pins: 报告所有具有可见电源属性的管脚是否有连接.

- Report unused part packages: 报告原理图中未使用的器件part;

- Report invalid Refdes: 报告原理图中无效的器件位号:

- Report identical part references: 报告原理图相同的位号

Q & A ?

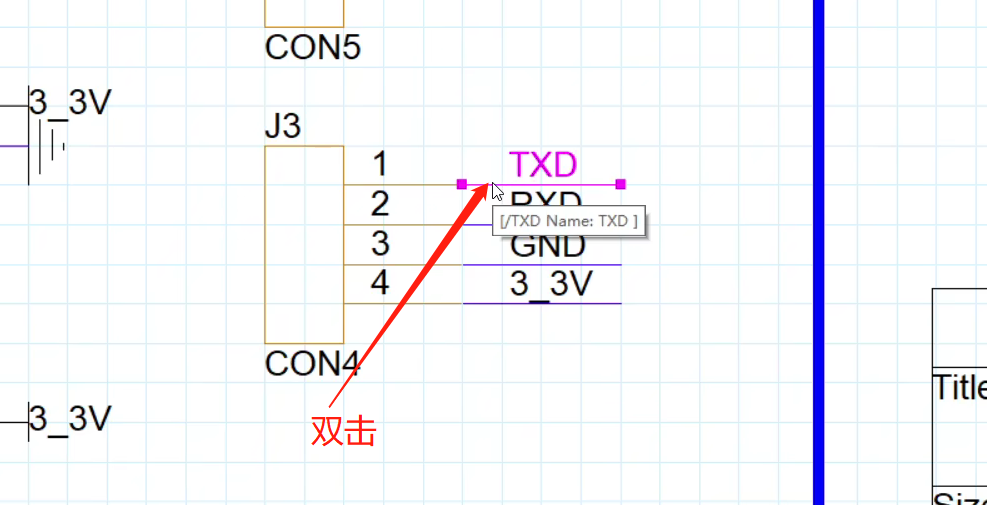

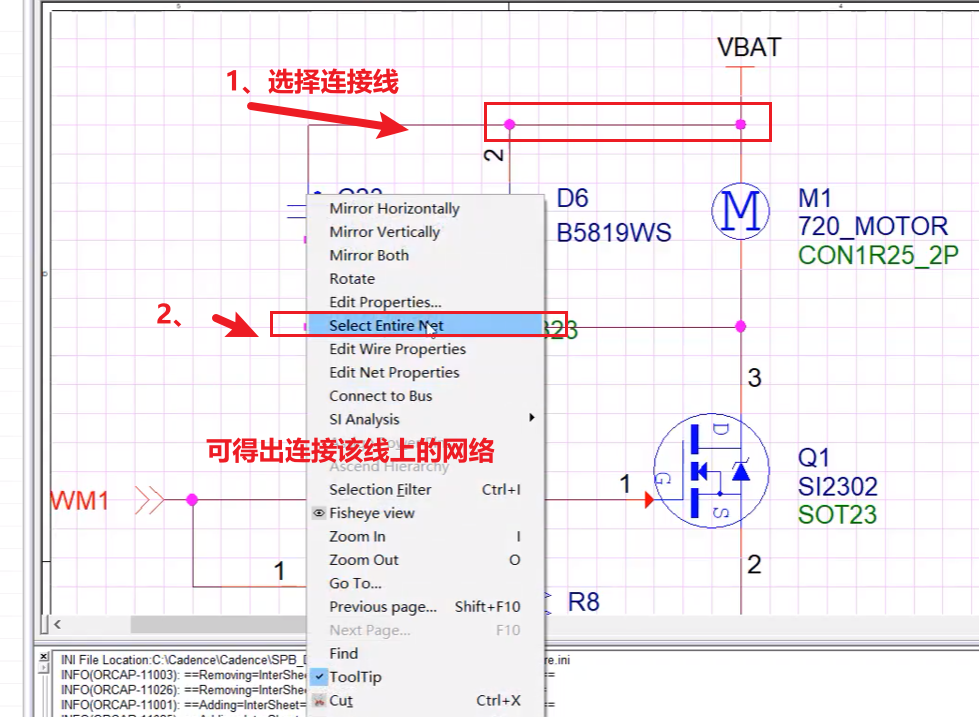

11、查看连接线上网络方法

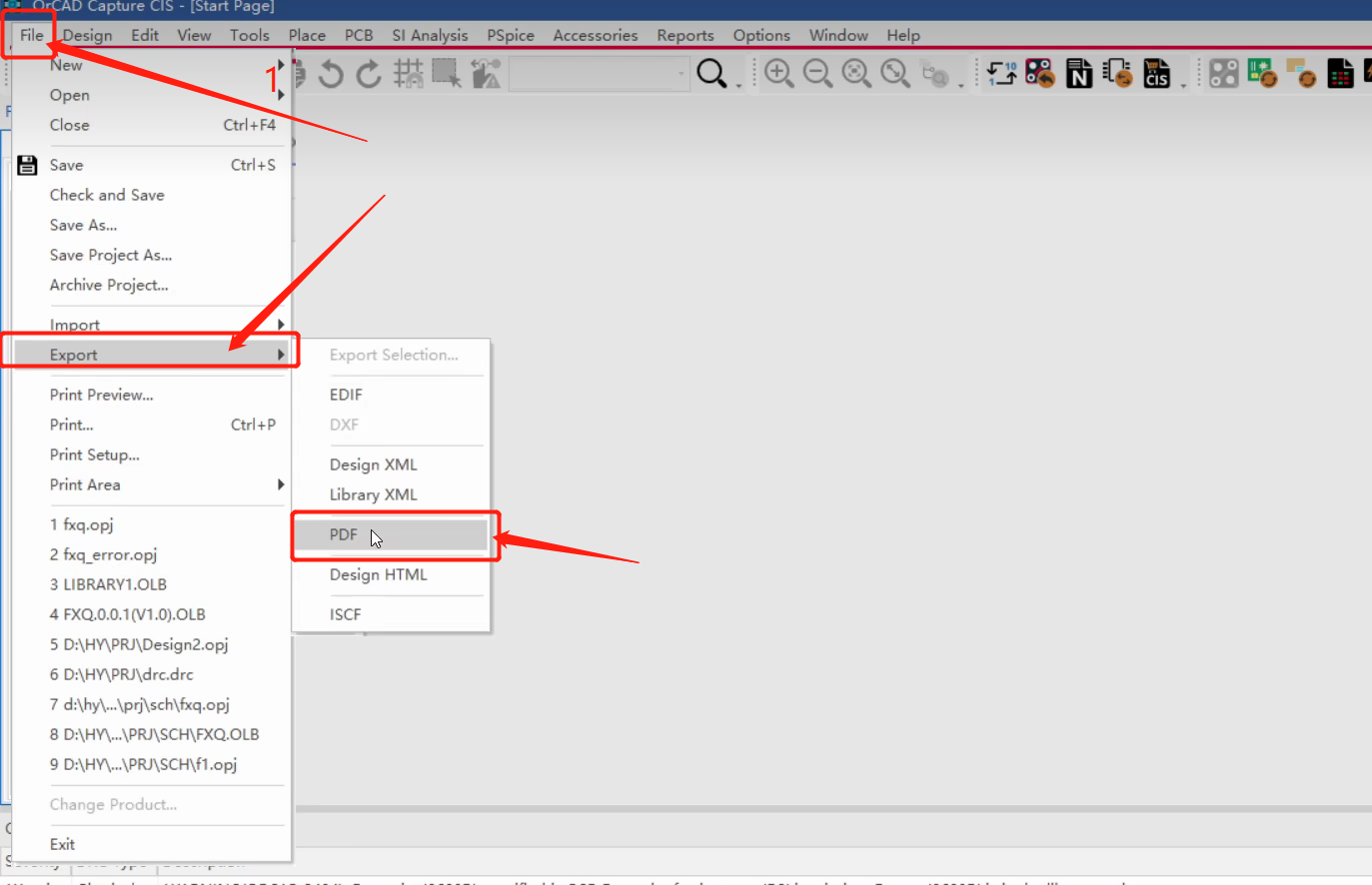

11、原理图导出PDF及BOM清单输出

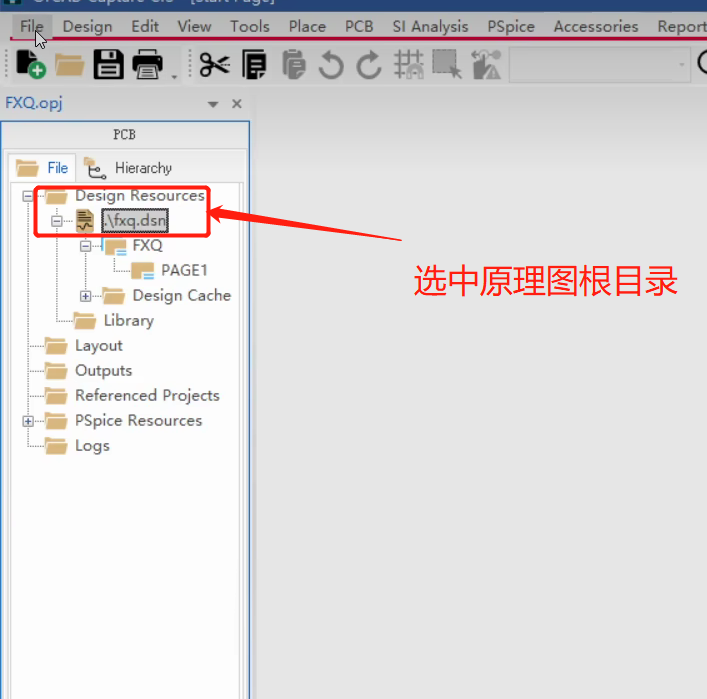

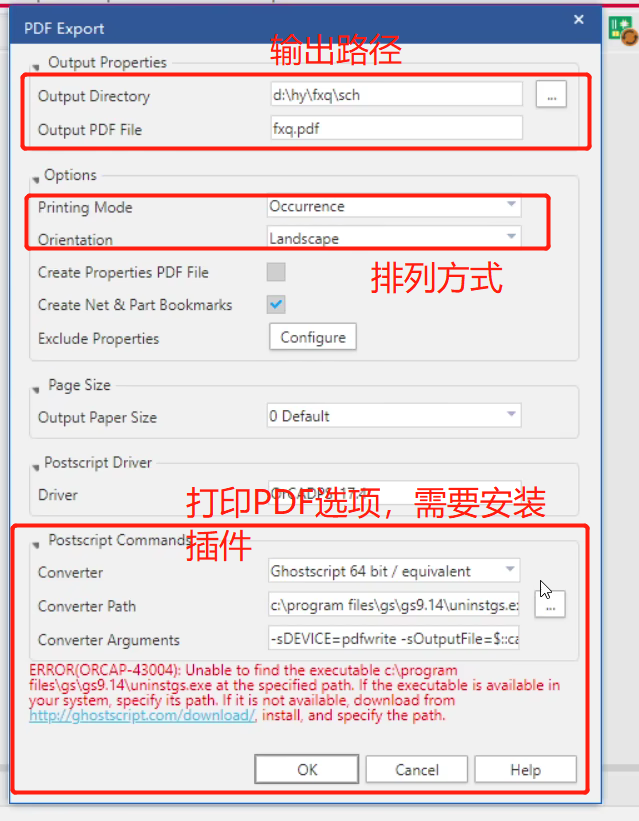

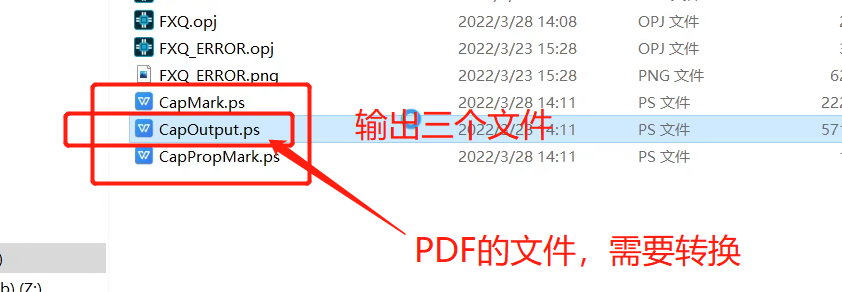

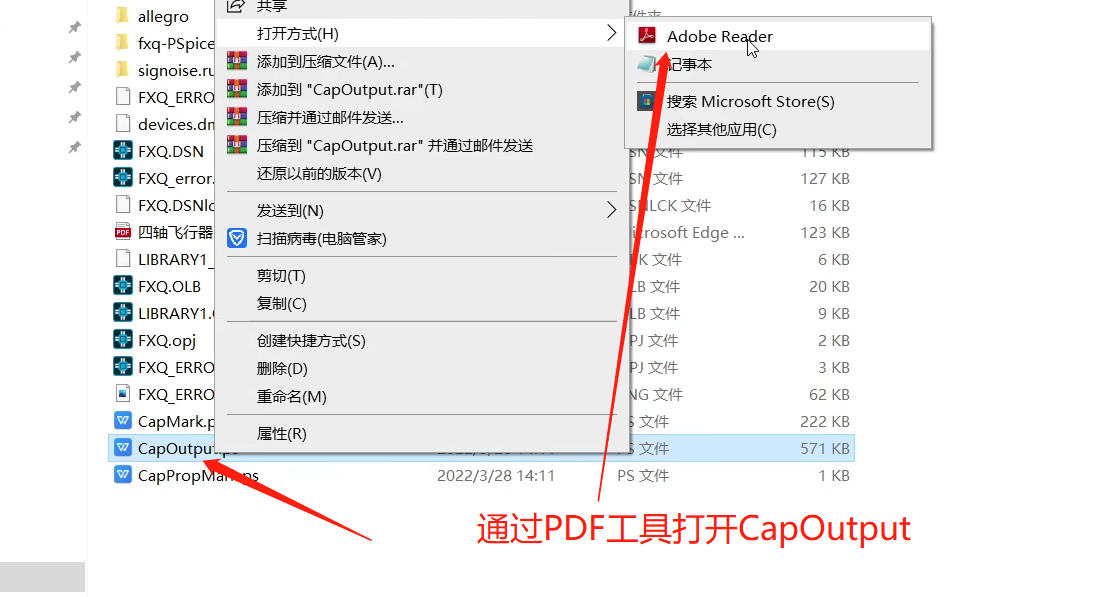

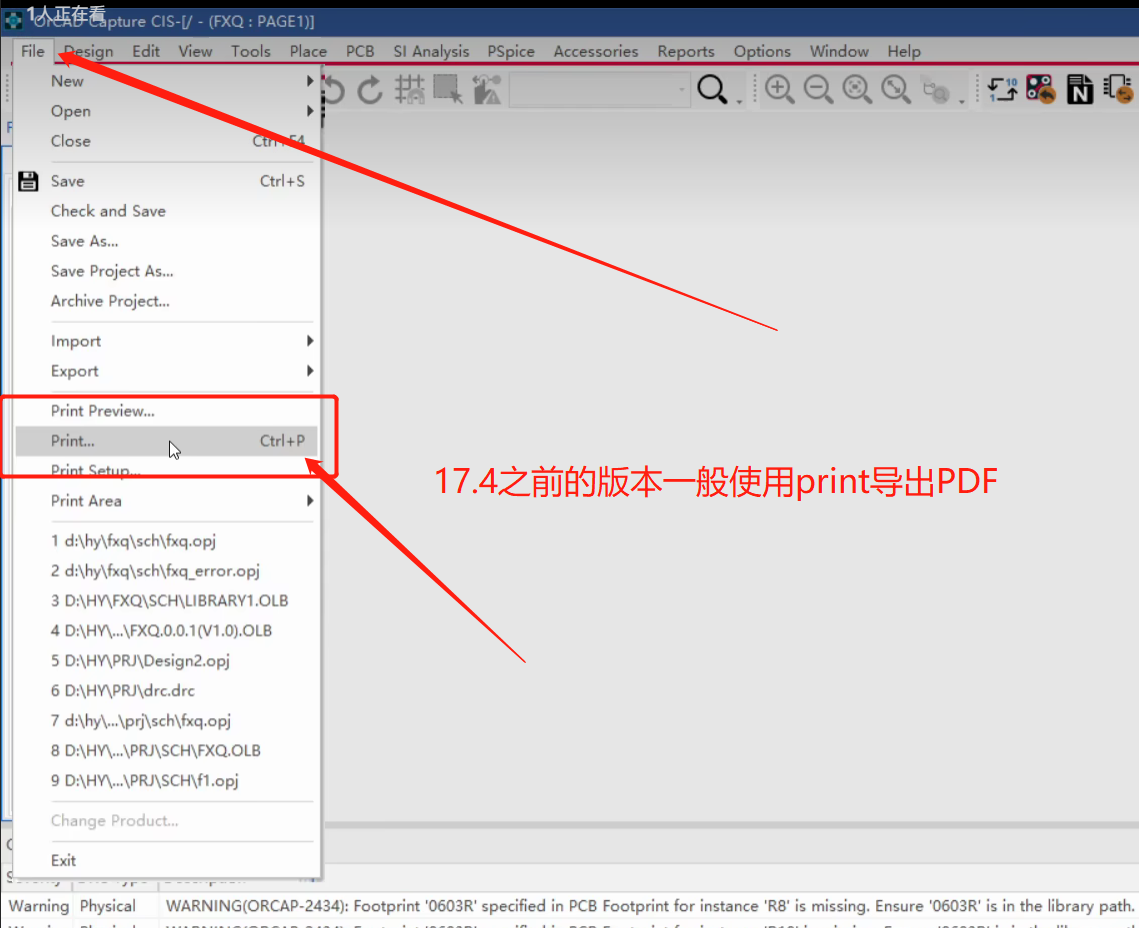

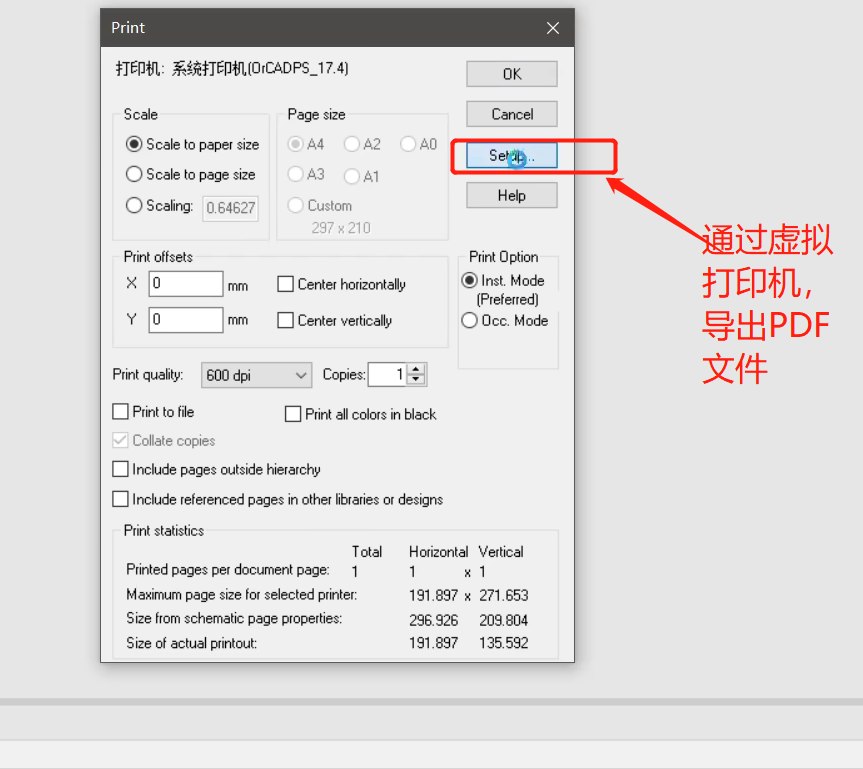

1、PDF输出

方式一、

方式二、

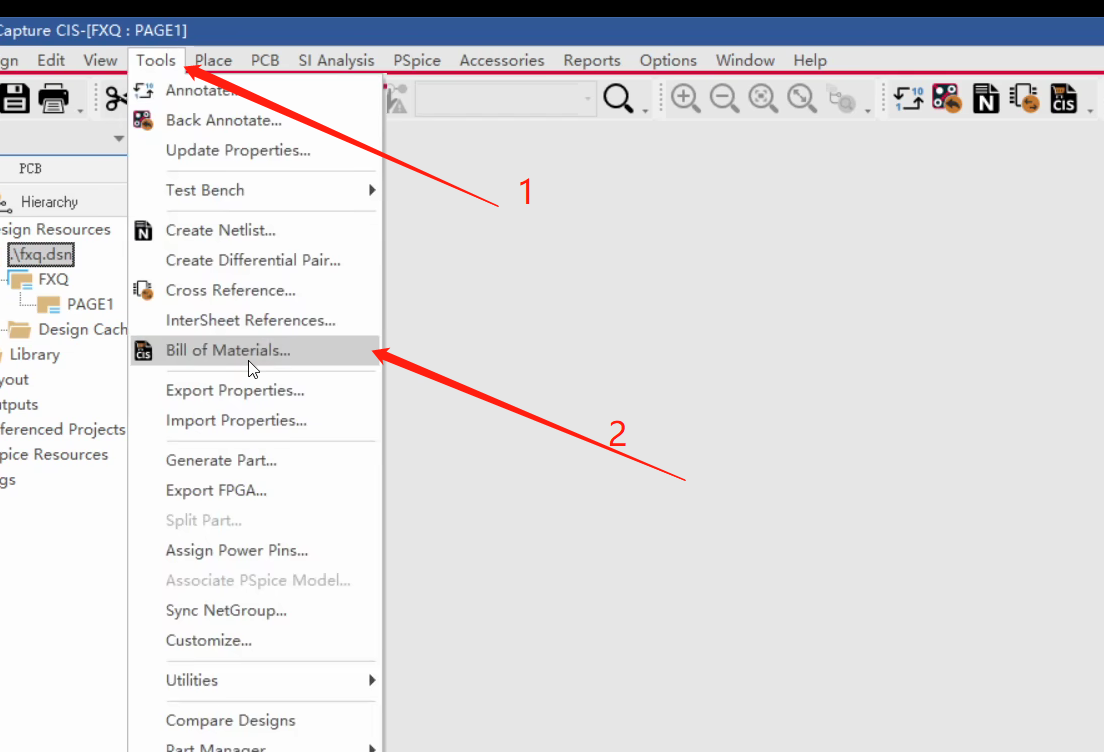

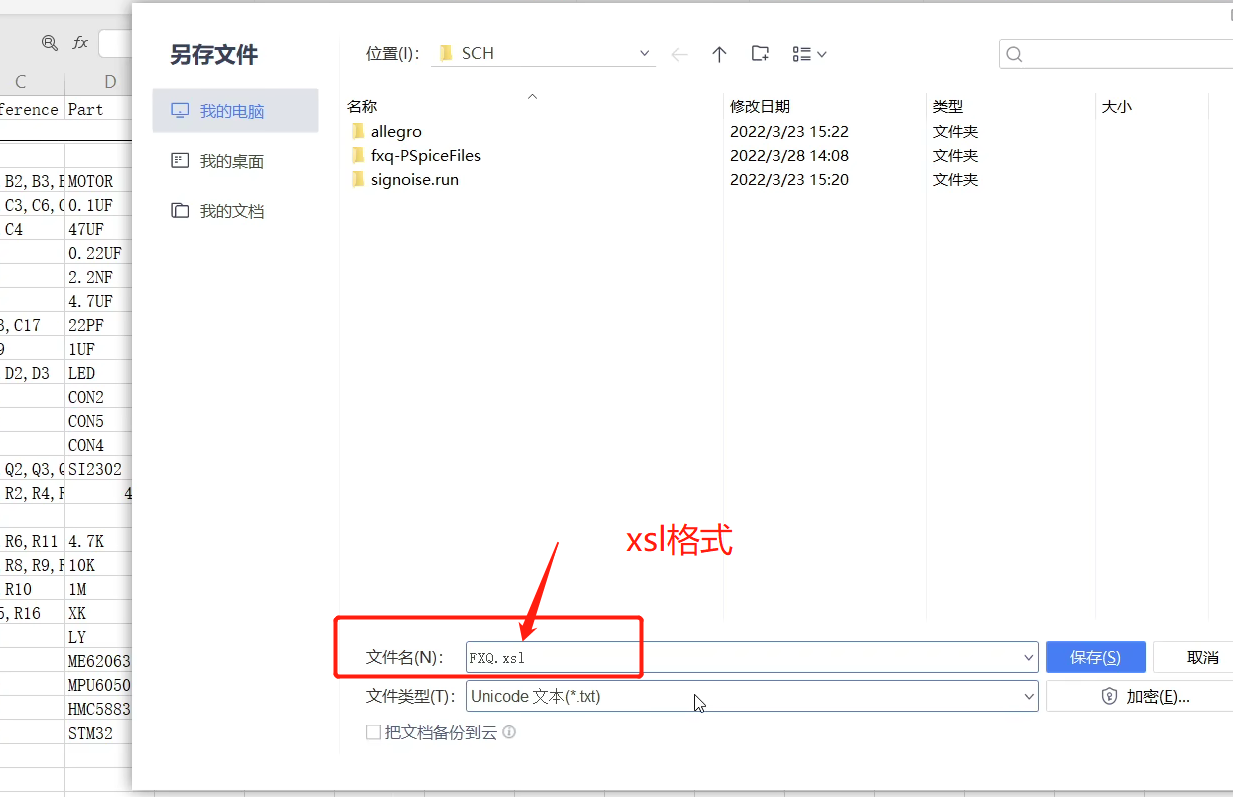

2、BOM清单输出

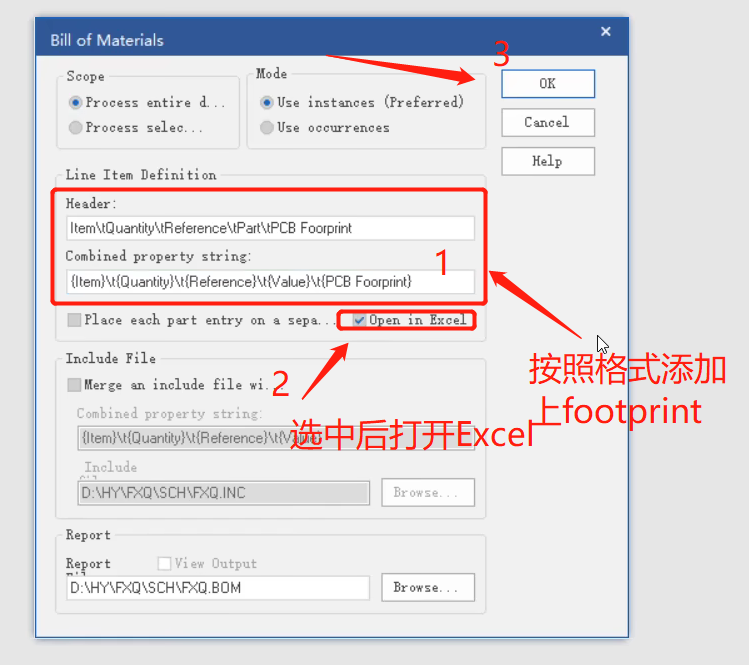

1、选中根目录以后,执行菜单命令Tools--Bi11of Materials···命令,来进行BOM清单的输出;

2、在Header以及Combined Property String栏中分别列出了需要输出的元素,依次是器件的数量、器件的位号、器件的属性值:

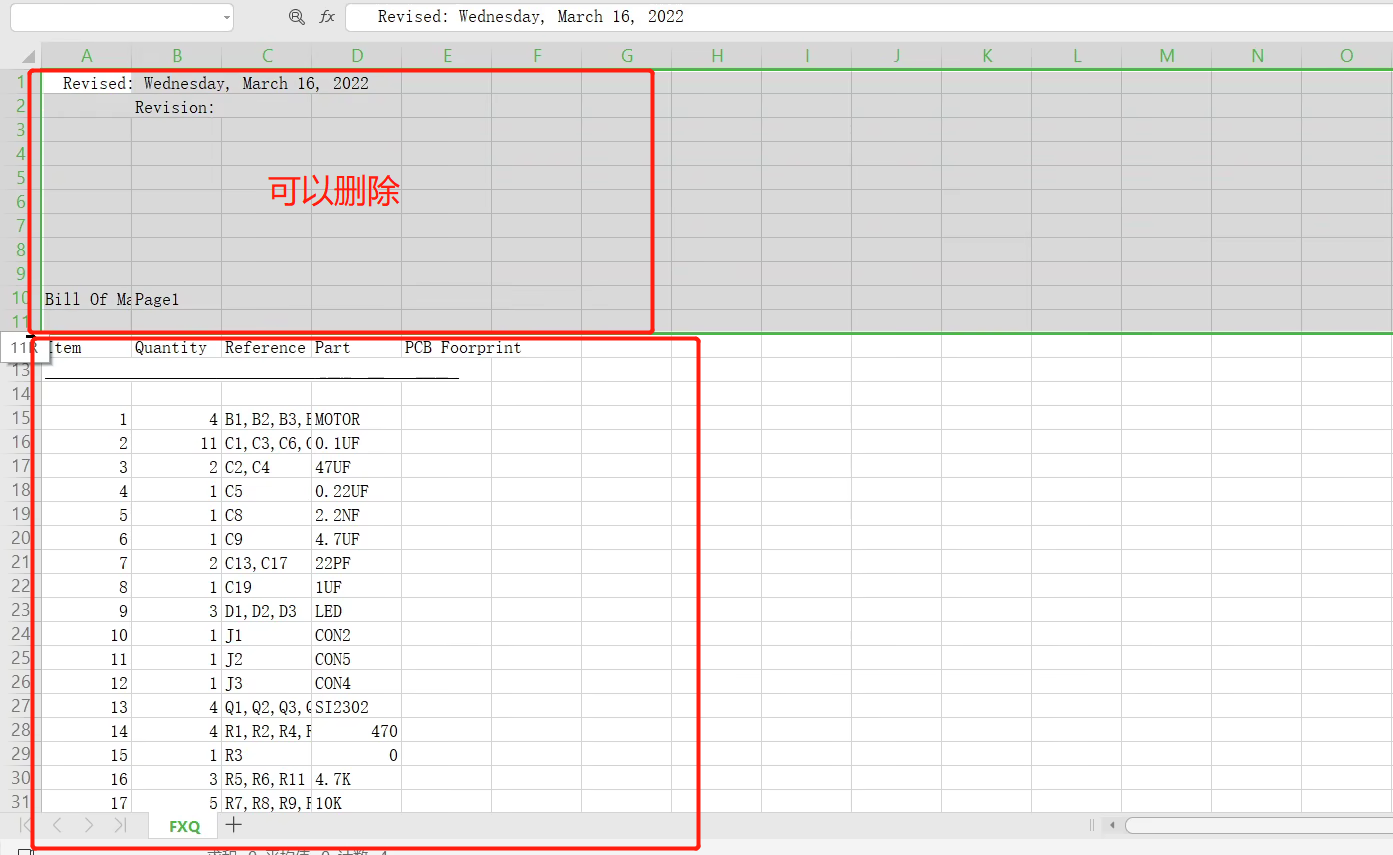

3、缺失器件的封装属性值,需要单独加上,格式就是跟Header以及Combined Property String栏致,勾选上Open in Excel,这样输出BOM清单就用EXCEL表格打开了,进行编辑整理,得到需要的BOM清单。

存放在原理图目录下

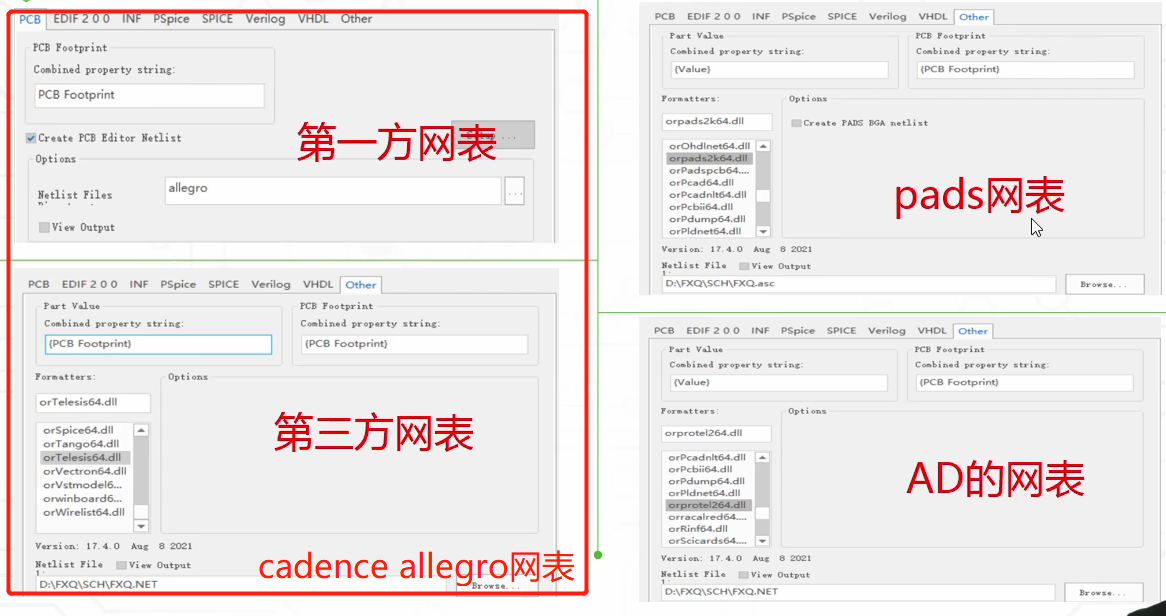

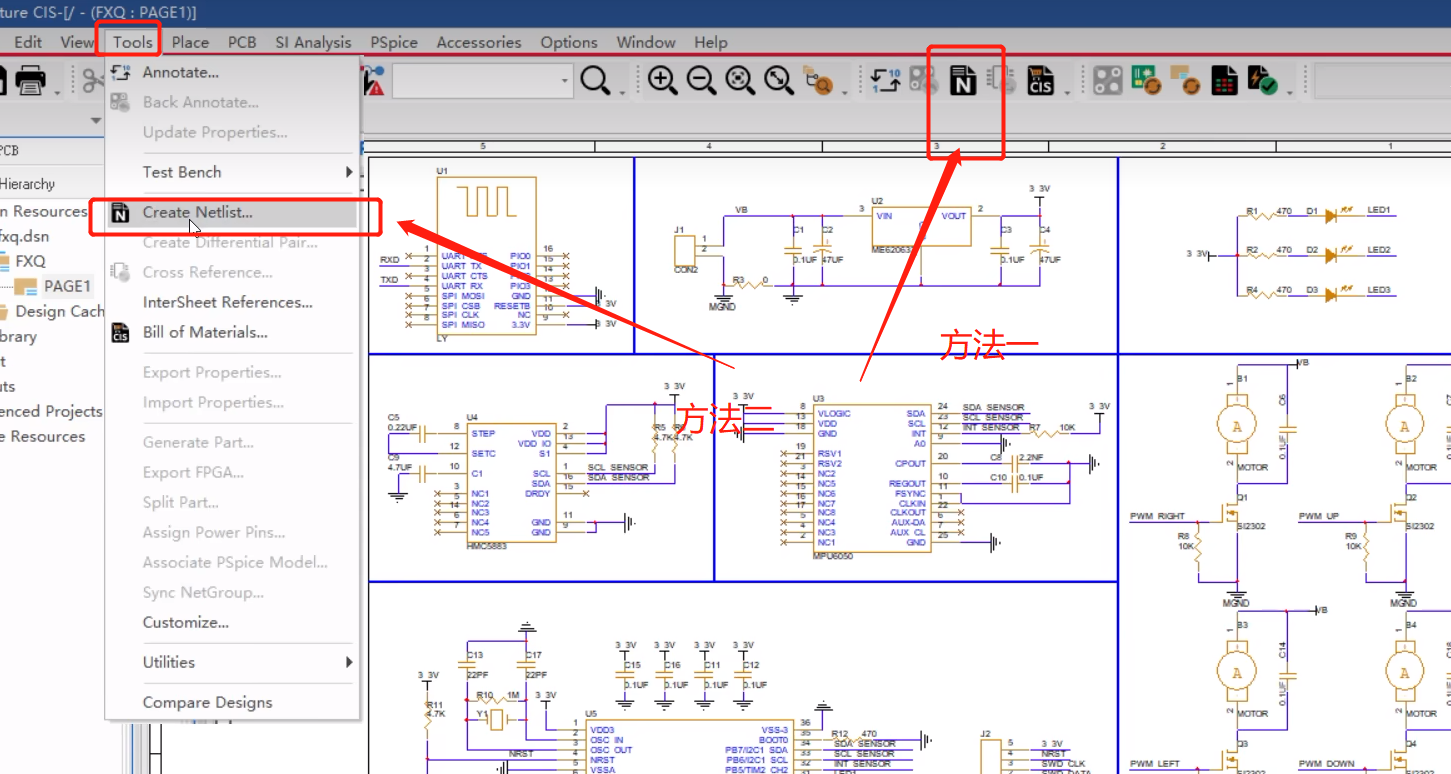

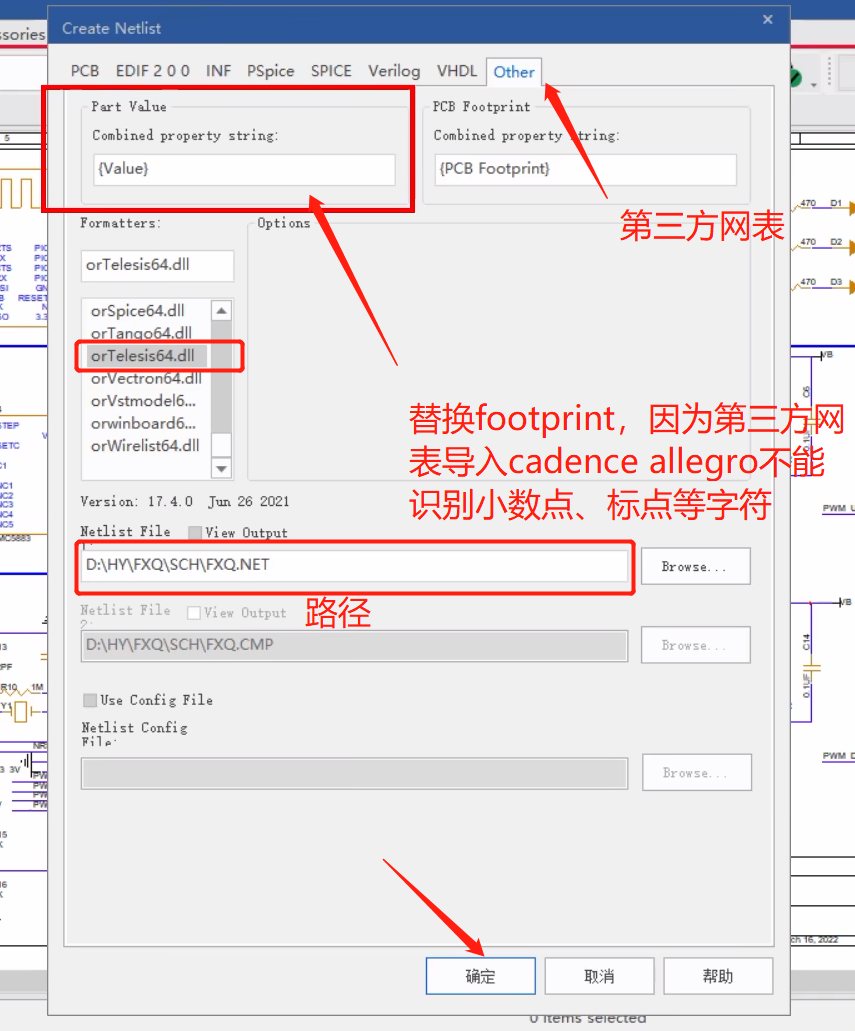

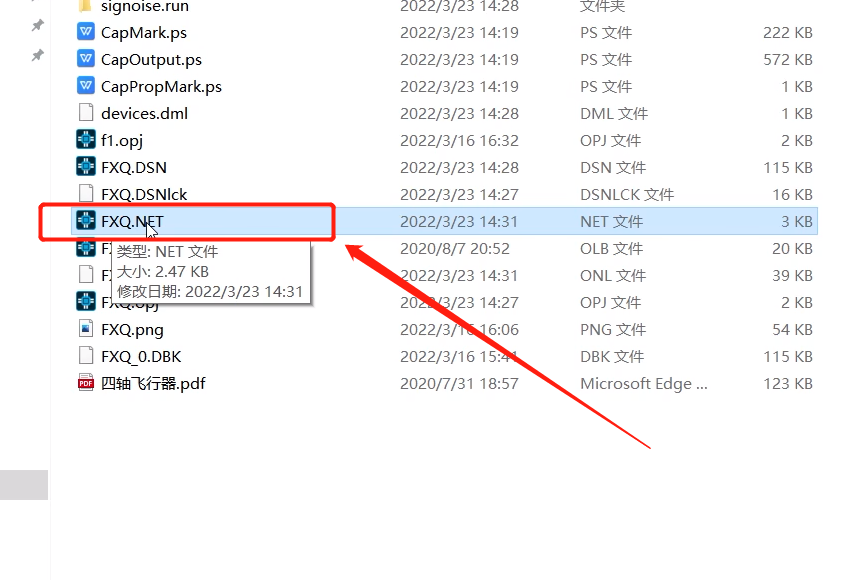

12、各类PCB网表的导出

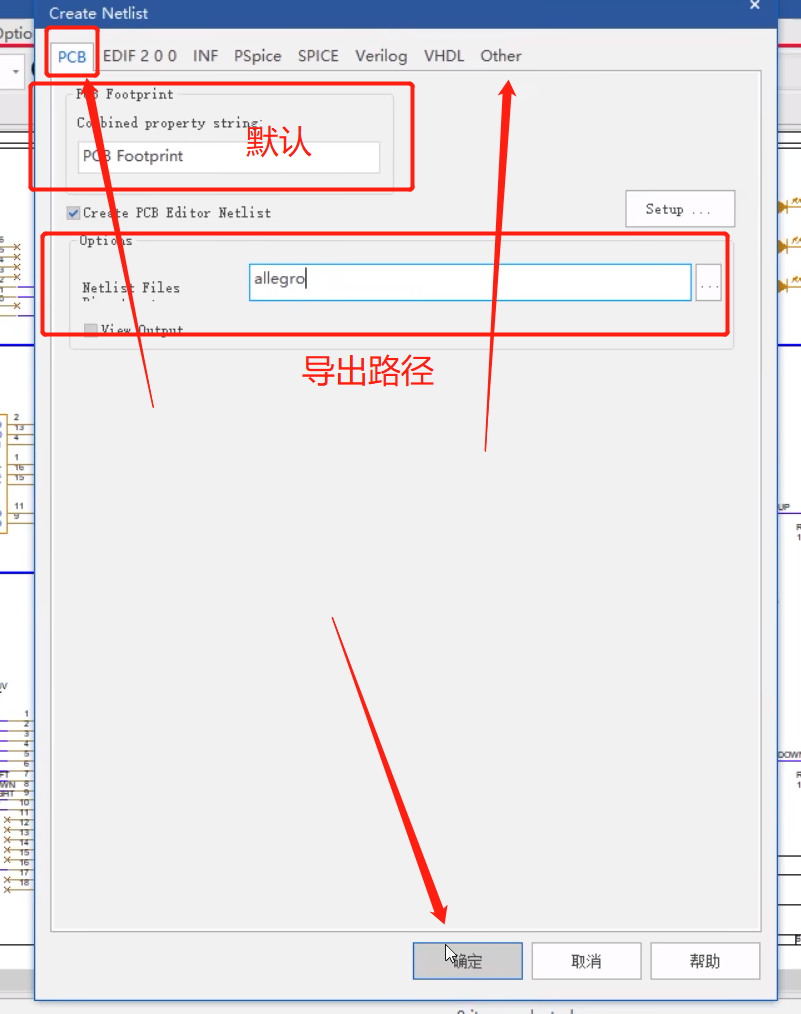

12.1 第一方网表

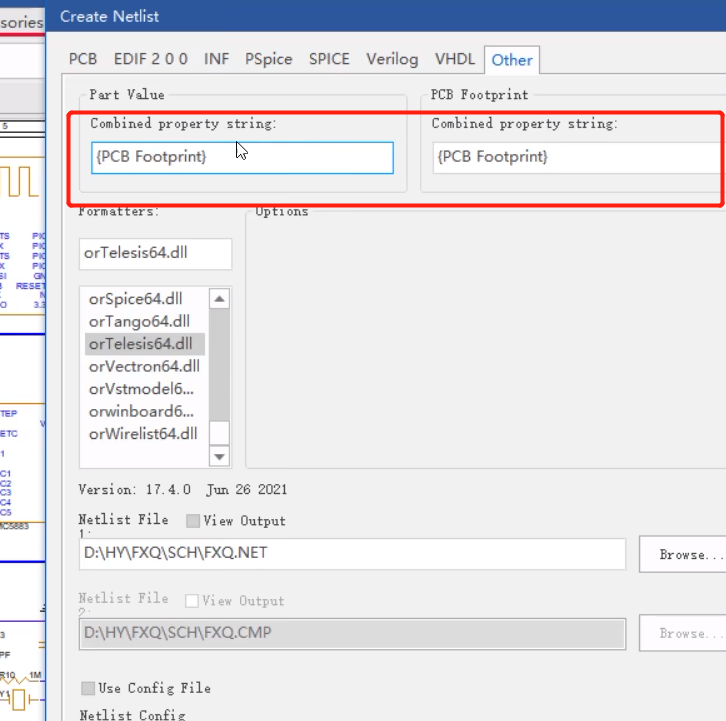

12.2第三方网表

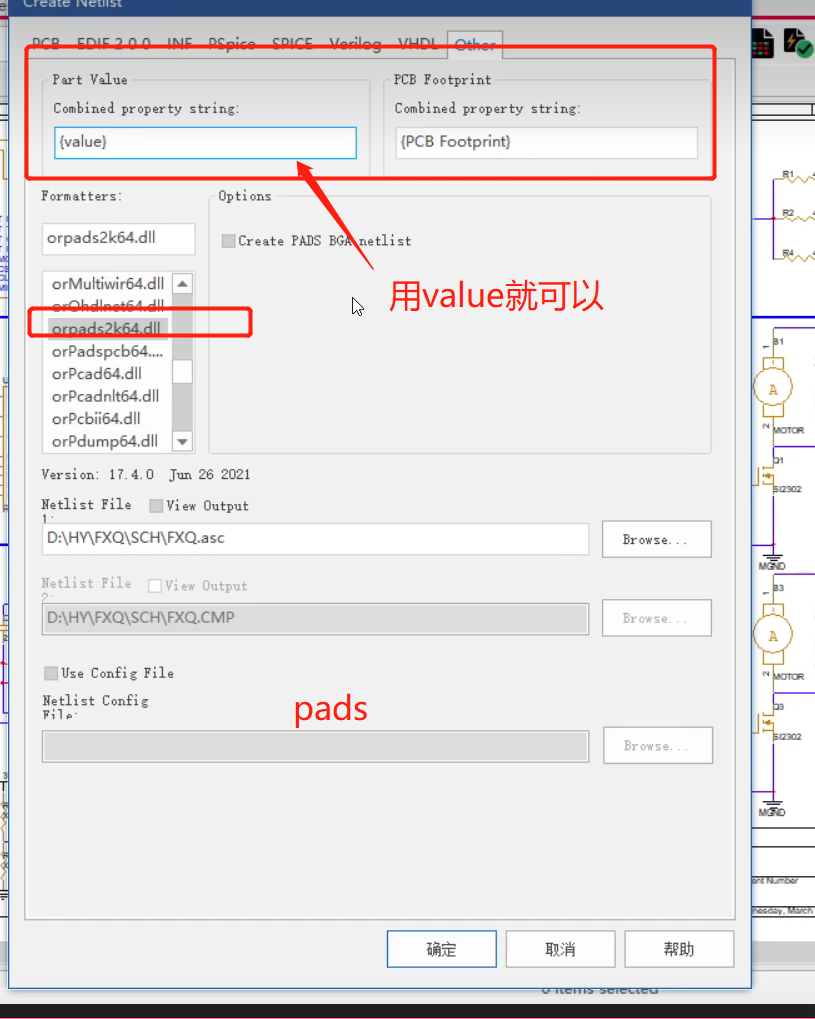

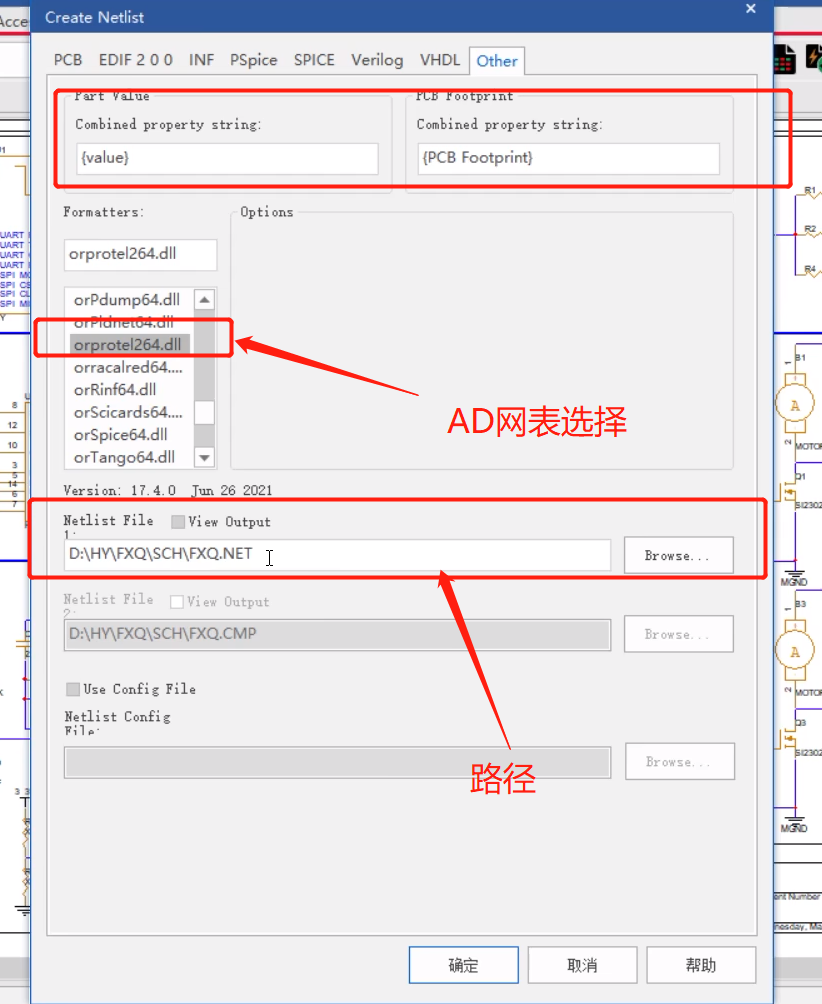

先选择formatters在进行替换Part Value

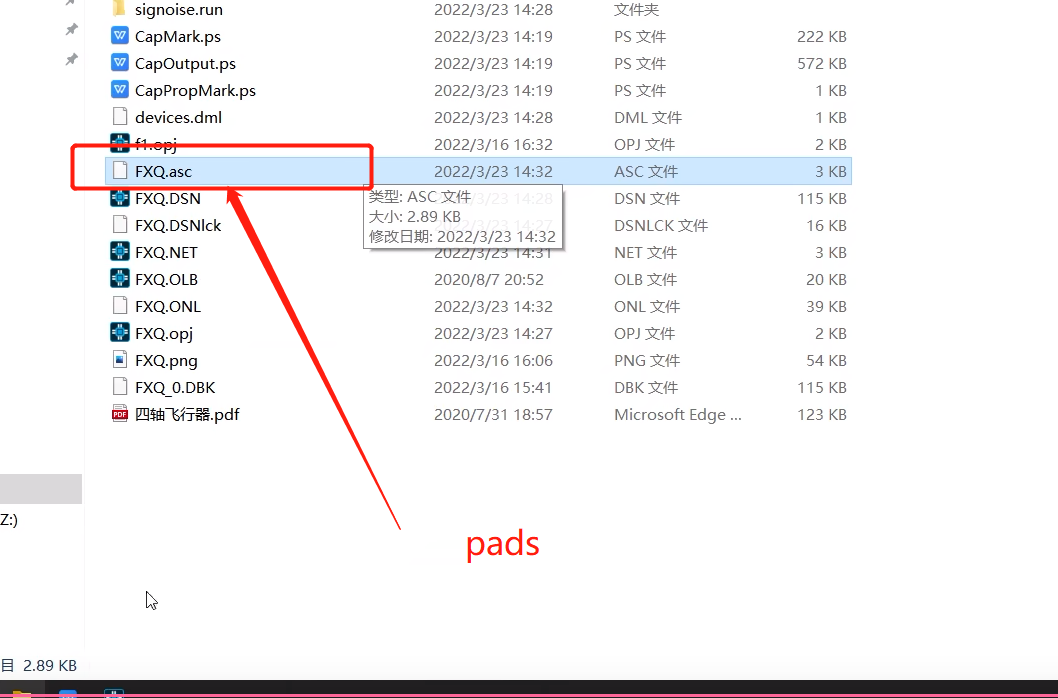

12.3 pads网表

12.4 AD网表

12.5 输出网表常见错误解析

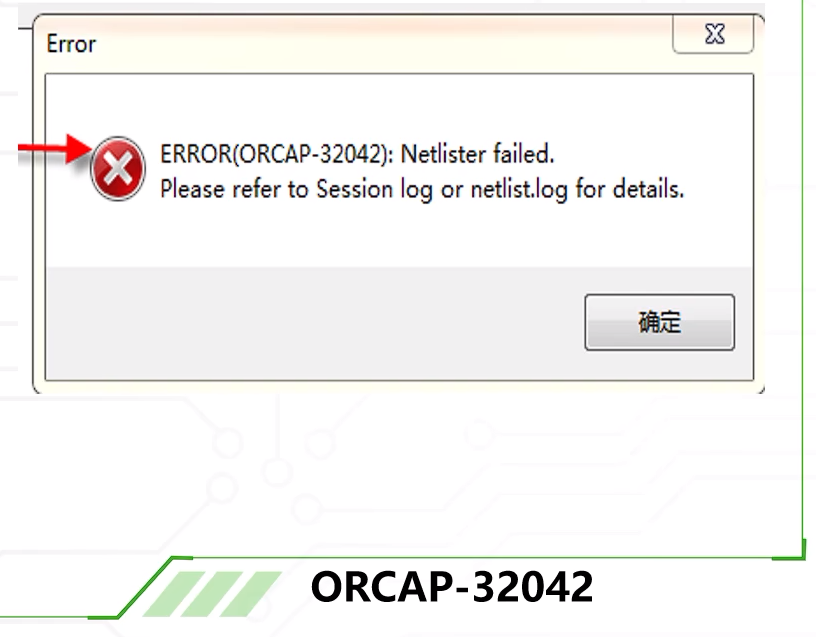

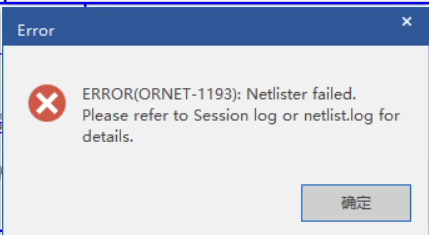

Q1:ORCAP-32042

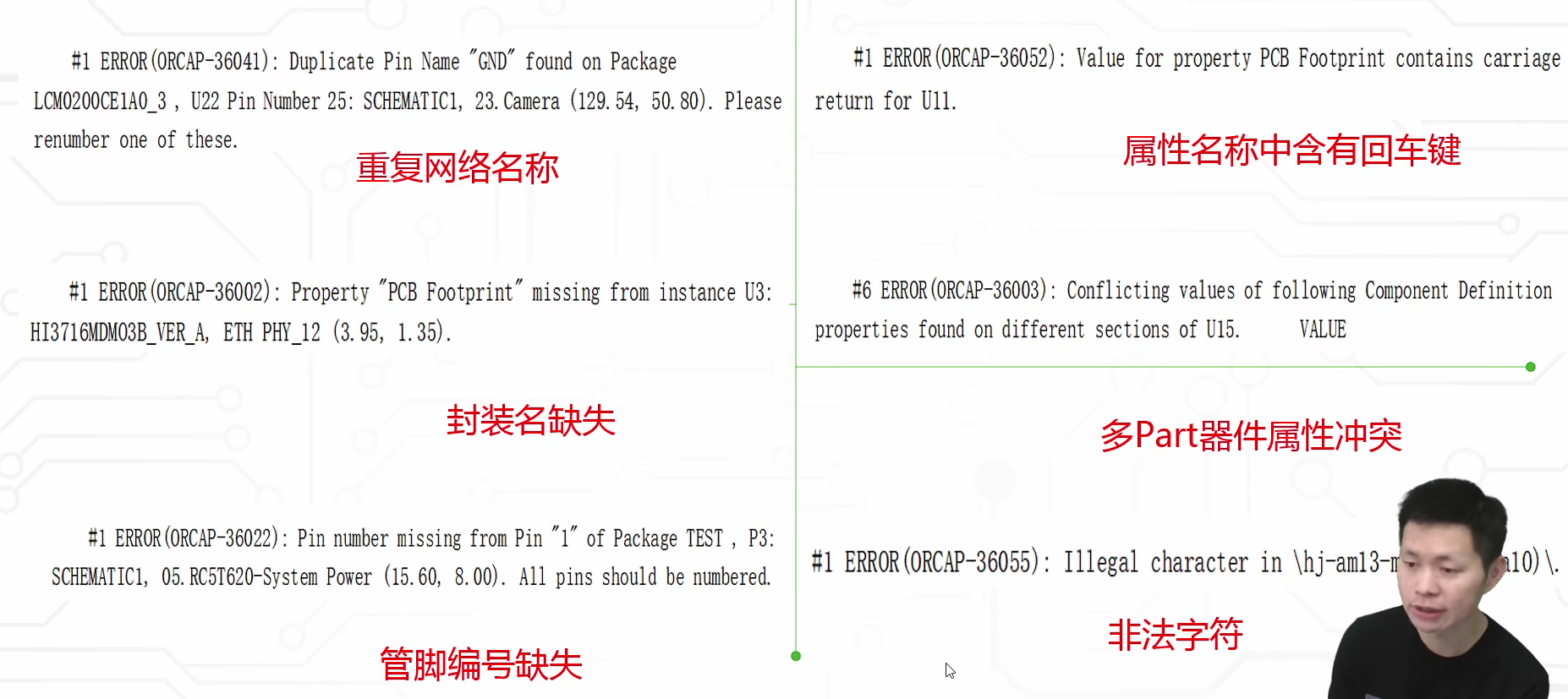

A1:使用Orcad软件进行输出Allegro第一方网表时,有时会出现一些错误,这个是表示原理图有错误,不满足Allegro软件的要求,不能输出网表,需要找到netlist.log这个文件,原理图中存在的错误在这有详细的描述,这个文件一般存储于输出网表的那个文件夹下,用写字本文件打开此文件,将列表中所列的错误解决掉,即可输出网表文件

常见错误??

本文来自博客园,作者:登云上人间,转载请注明原文链接:https://www.cnblogs.com/lj15941314/p/17201903.html