单片机之ARM Cortex‐M3处理器

一、介绍

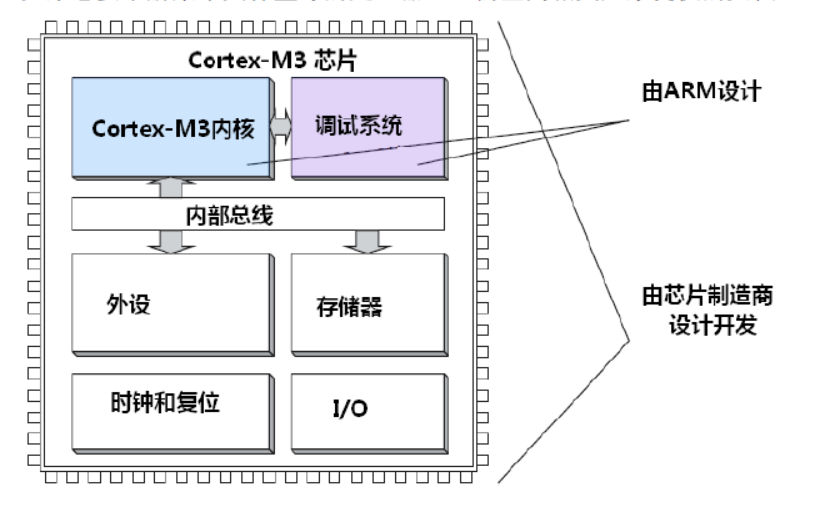

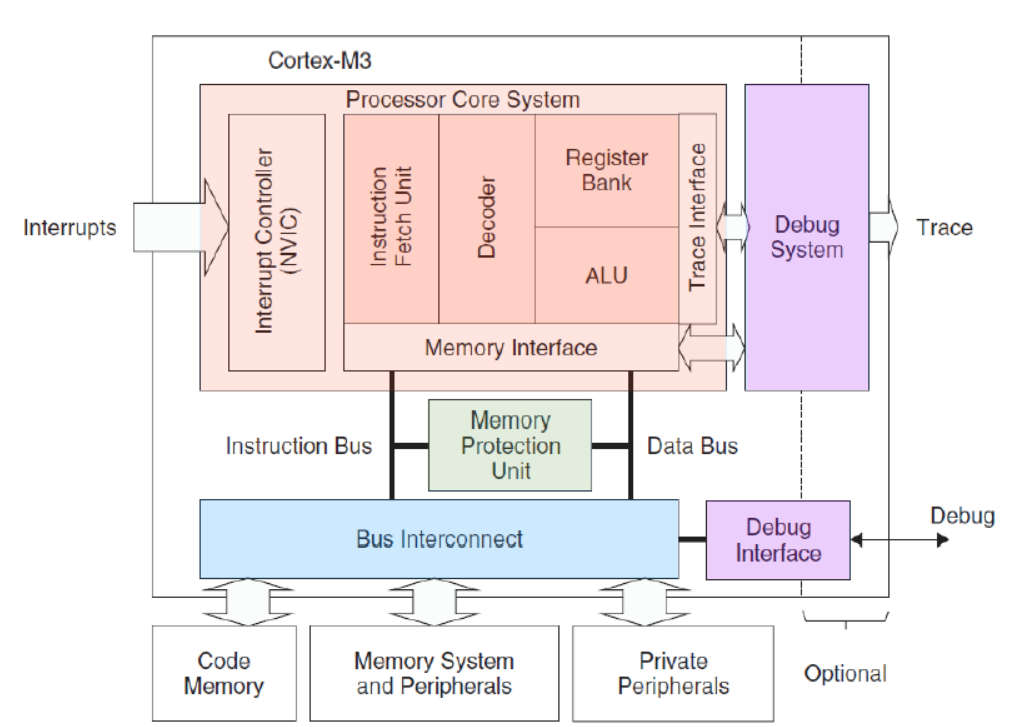

Cortex-M3 处理器内核 vs. 基于Cortex-M3的MCU

- Cortex‐M3处理器内核是单片机的中央处理单元(CPU)。

- 完整的基于CM3的MCU还需要很多其它组件。

- 在芯片制造商得到CM3处理器内核的使用授权后,它们就可以把CM3内核用在自己的硅片设计中,添加存储器,外设,I/O以及其它功能块。

- 不同厂家设计出的单片机会有不同的配置,包括存储器容量、类型、外设等都各具特色。

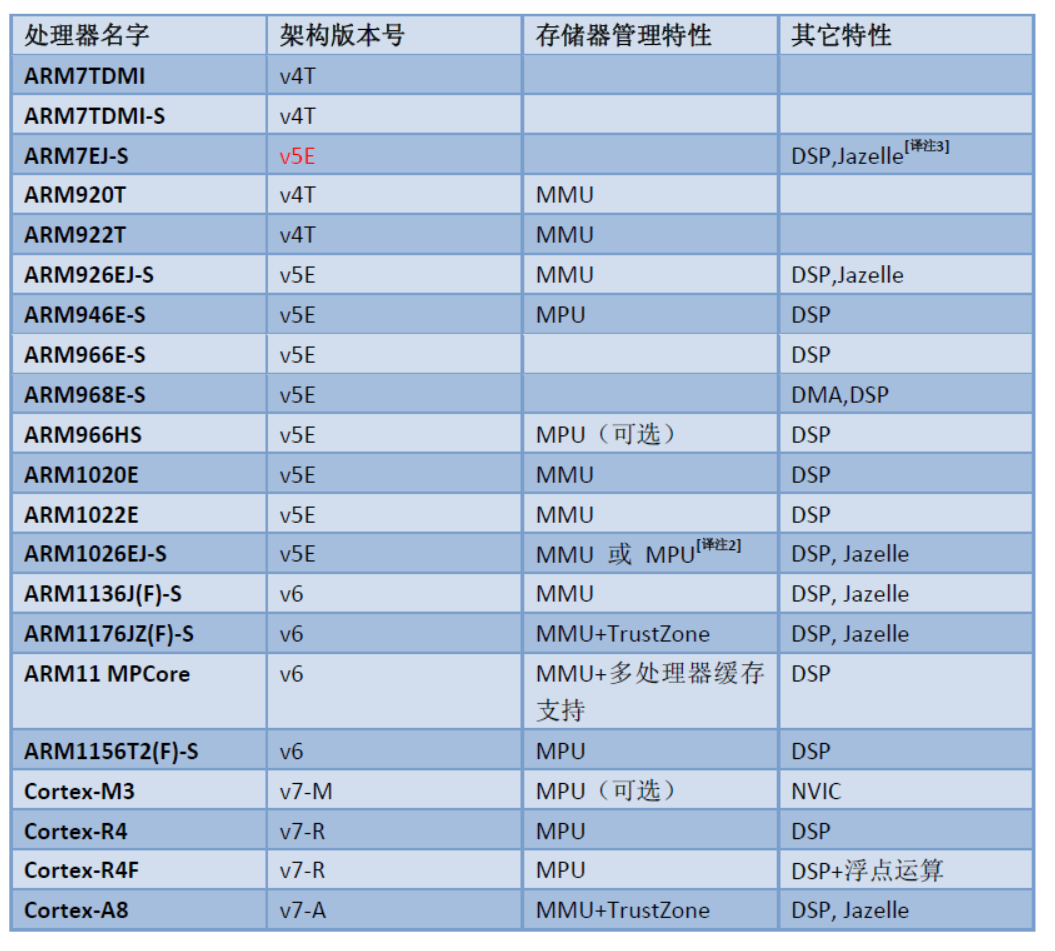

基于ARMv7的新架构

基于从ARMv6开始的新设计理念,ARM进一步扩展了它的CPU设计,出现ARMv7架构的新成果。内核架构首次从单一款式变成3种款式。

- 款式A(ARMv7‐A):设计用于高性能的“开放应用平台”——越来越接近电脑

- 款式R(ARMv7‐R):硬实时且高性能的处理器。

- 款式M(ARMv7‐M):用于深度嵌入的,单片机风格的系统中。

ARM处理器名字

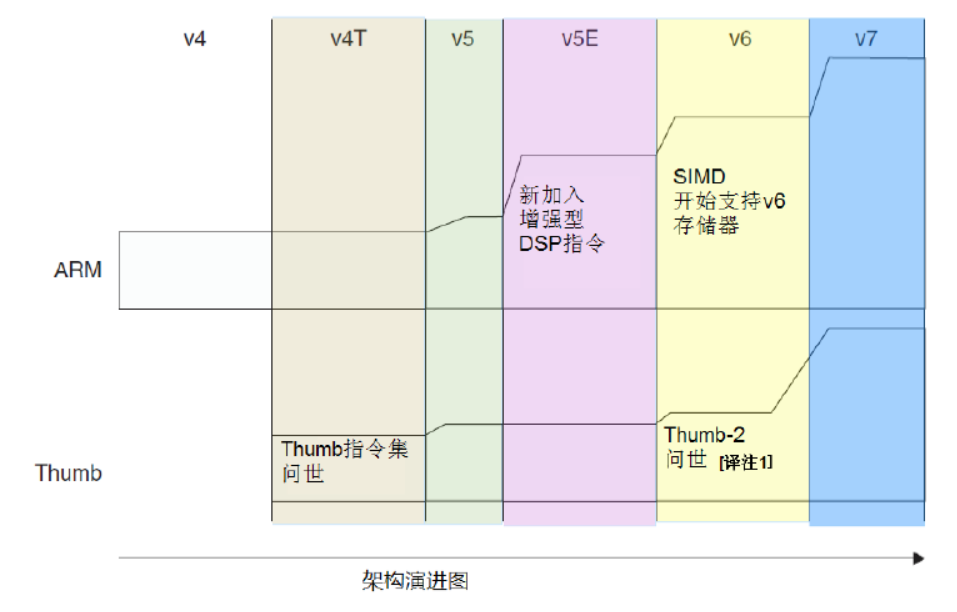

指令系统的开发

从ARM7TDMI开始,ARM处理器一直支持两种形式上相对独立的指令集,它们分别是:

- 32位的ARM指令集。对应处理器状态:ARM状态

- 16位的Thumb指令集。对应处理器状态:Thumb状态

Thumb指令集在功能上是ARM指令集的一个子集。

Thumb-2指令集体系体系结构(ISA)

- Thumb‐2是16位Thumb指令集的一个超集。

- 16位指令首次与32位指令并存。

- Cortex‐M3不支持32位ARM指令集。

- 在支持了both 16位和32位指令之后,处理器状态不需要在Thumb和ARM之间来回的切换。

书籍介绍:

- ARMv7‐M的私房秘密记录在《The ARMv7‐M Architecture Application Level Reference Manual》中,ARM已经将其公开。

- 《Cortex-M3 Technical Reference Manual》中记录了实现v7‐M时的很多细节和花絮。

- 《The Cortex‐M3 Technical Reference Manual》,深入处理器的内心,编程模型,存储器映射,还包括了指令时序。

- 《 The ARMv7‐M Architecture Application Level Reference Manual》第2版,对指令集和存储器模型都提供了最不嫌繁的说明。其它半导体厂家提供的,基于CM3单片机的数据手册。

- 《AMBA Specification 2.0》(第4版),它讲了更多AMBA接口的内幕,更多总线协议的细节。

- 《ARM Application Note 179: Cortex‐M3 Embedded SoftwareDevelopment》(第7版)一些编程技巧和提示。

二、ARM概论

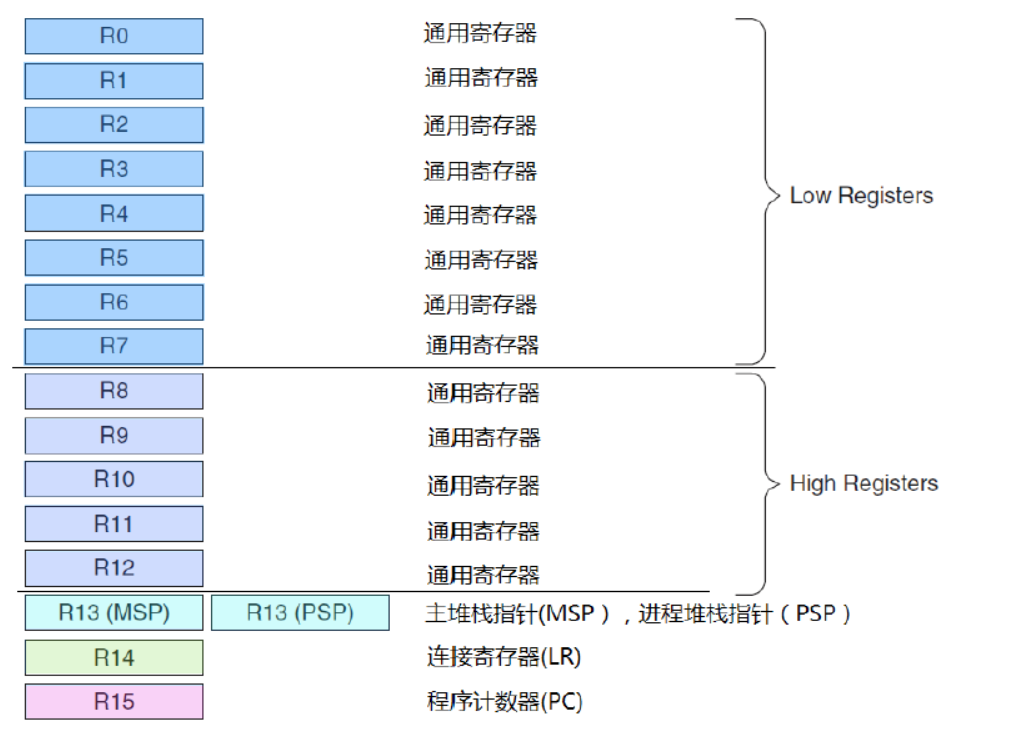

寄存器组

总论

- Cortex‐M3 处理器拥有R0‐R15 的寄存器组。

- R13 作为堆栈指针SP。

- SP 有两个,但在同一时刻只能有一个可以看到,即所谓的“banked”寄存器。

R0‐R12

- R0‐R12 都是32 位通用寄存器,用于数据操作。

- 绝大多数16 位Thumb 指令只能访问R0‐R7,32 位Thumb‐2 指令可以访问所有寄存器。

R0‐R7

- R0‐R7 被称为低组寄存器。

- 所有指令都能访问它们。

- 它们的字长全是32 位,复位后的初始值是不可预料的。

R8‐R12

- R8‐R12 被称为高组寄存器。

- 只有很少的16 位Thumb 指令能访问它们,32位的指令则不受限制。

- 字长是32 位,且复位后的初始值是不可预料的。

R13:两个堆栈指针

-

主堆栈指针(MSP),或写作SP_main:复位后缺省使用的堆栈指针,用于操作系统内核以及异常处理例程(包括中断服务例程)

-

进程堆栈指针(PSP),或写作SP_process:由用户的应用程序代码使用。

堆栈指针的最低两位永远是0,这意味着堆栈总是4 字节对齐的。 -

当引用R13(或写作SP)时,你引用到的是当前正在使用的那一个,另一个必须用特殊的指令来访问(MRS,MSR 指令)。

-

在ARM 编程领域中,

凡是打断程序顺序执行的事件,都被称为异常(exception)。 -

除了外部中断外,当有指令执行了“非法操作”,或者访问被禁的内存区间,因各种错误产生的fault,以及不可屏蔽中断发生时,都会打断程序的执行,这些情况统称为异常。

-

并不是每个应用都必须用齐两个堆栈指针。简单的应用程序只使用MSP就够了。

-

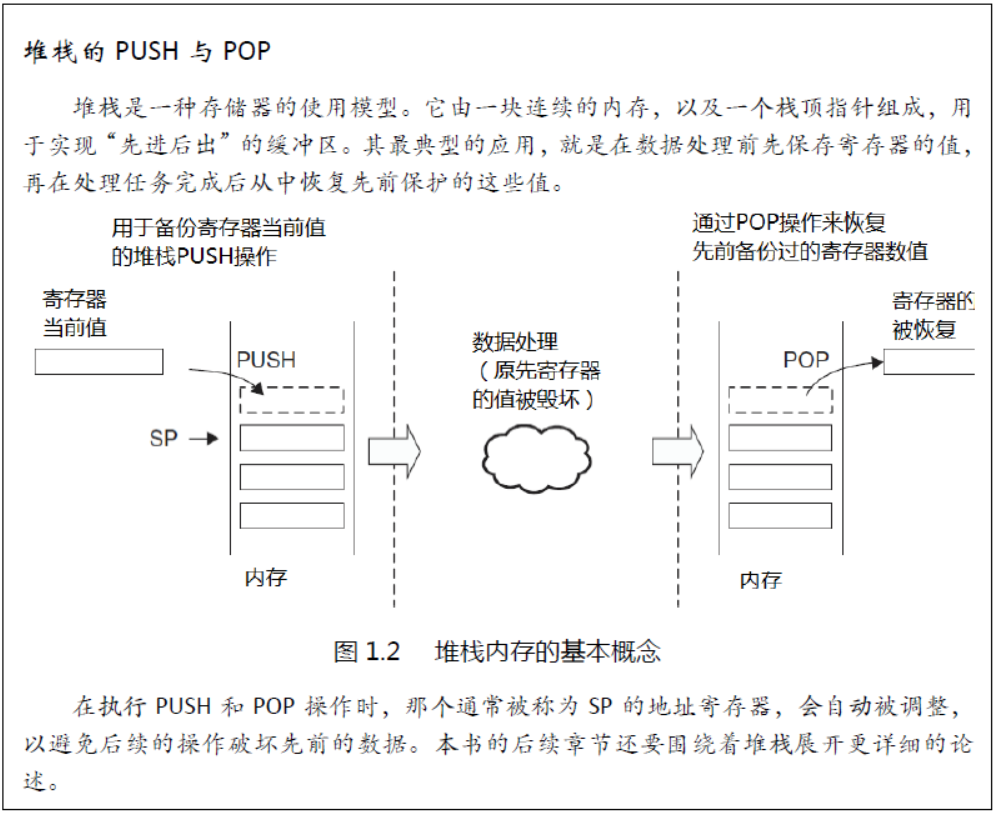

堆栈指针用于访问堆栈,并且PUSH 指令和POP 指令默认使用SP。

-

在Cortex‐M3 中,有专门的指令负责堆栈操作——PUSH 和POP。

PUSH {R0} ; *(--R13)=R0。R13 是long*的指针

POP {R0} ; R0= *R13++

R14:连接寄存器

- R14 是连接寄存器(LR)。

- 当呼叫一个子程序时,由

R14 存储返回地址。 - ARM 为了

减少访问内存的次数(访问内存的操作往往要3 个以上指令周期,带MMU和cache 的就更加不确定了),把返回地址直接存储在寄存器中。

R15:程序计数寄存器

- 指向

当前的程序地址。 - 如果修改它的值,就能改变程序的执行流。

- 读PC 时返回的值是当前指令的地址+4。

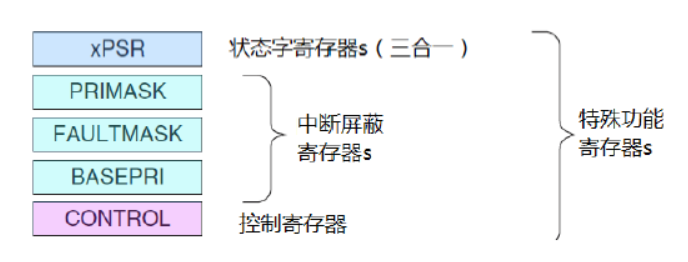

特殊功能寄存器

- Cortex‐M3 还在内核水平上搭载了若干特殊功能寄存器。

- Cortex‐M3 中的特殊功能寄存器包括:

- 程序状态寄存器组(PSRs 或xPSR)

- 中断屏蔽寄存器组(PRIMASK, FAULTMASK,以及BASEPRI)

- 控制寄存器(CONTROL)

它们只能被专用的MSR 和MRS 指令访问,而且它们也没有存储器地址。

| 寄存器 | 功能 |

|---|---|

| xPSR | 记录ALU 标志(0 标志,进位标志,负数标志,溢出标志),执行状态,以及当前正服务的中断号 |

| PRIMASK | 除能所有的中断——当然了,不可屏蔽中断(NMI)才不甩它呢。 |

| FAULTMASK | 除能所有的fault——NMI 依然不受影响,而且被除能的faults 会“上访”,见后续章节的叙述。 |

| BASEPRI | 除能所有优先级不高于某个具体数值的中断。 |

| CONTROL | 定义特权状态(见后续章节对特权的叙述),并且决定使用哪一个堆栈指针 |

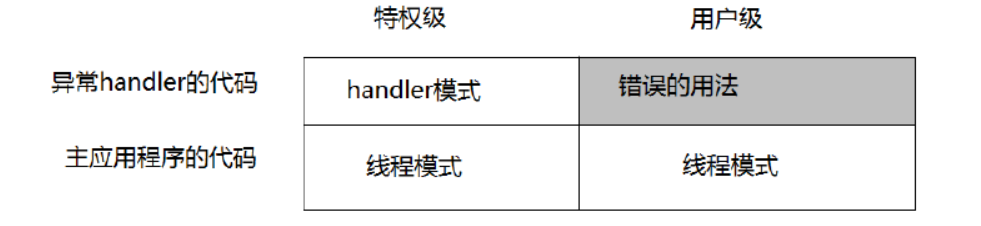

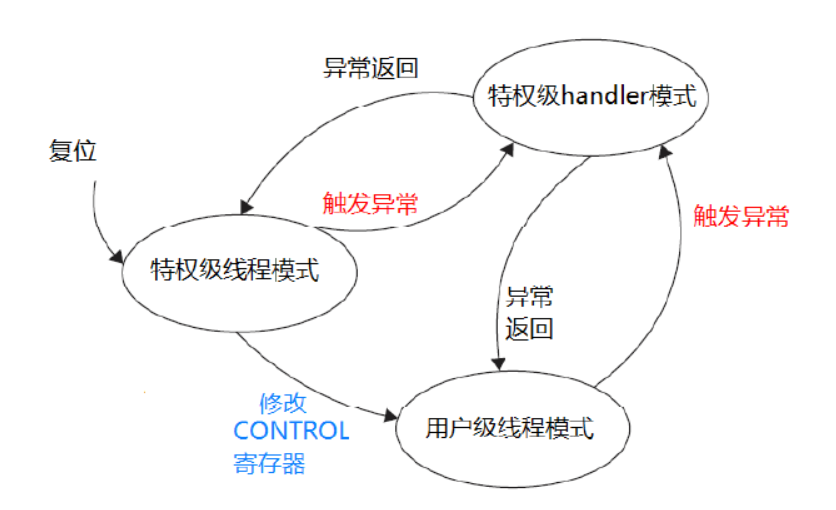

操作模式和特权极别

-

两种操作模式分别为:处理者模式(handler mode)和线程模式(thread mode)。

-

引入两个模式的本意,是用于

区别普通应用程序的代码和异常服务例程的代码——包括中断服务例程的代码。 -

Cortex‐M3 的另一个侧面则是特权的分级——特权级和用户级。

-

提供一种存储器访问的保护机制,

使得普通的用户程序代码不能意外地,甚至是恶意地执行涉及到要害的操作。

- 在CM3 运行主应用程序时(线程模式),既可以使用特权级,也可以使用用户级;

- 异常服务例程必须在特权级下执行。

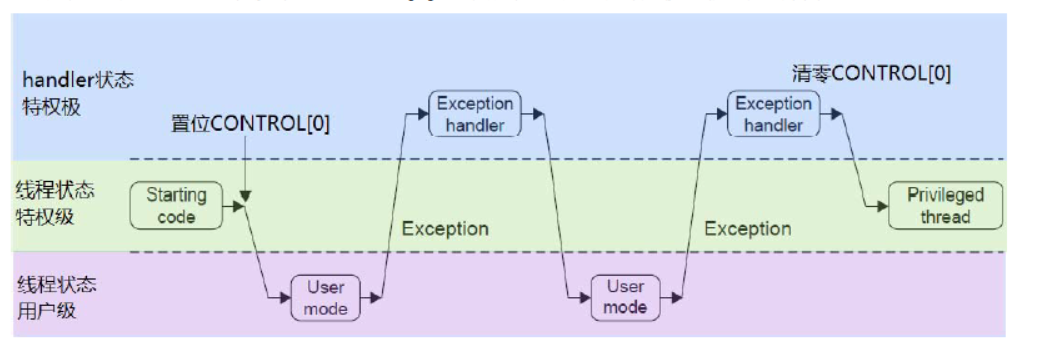

- 复位后,处理器默认进入线程模式,特权极访问。

合法的操作模式准换图如下:

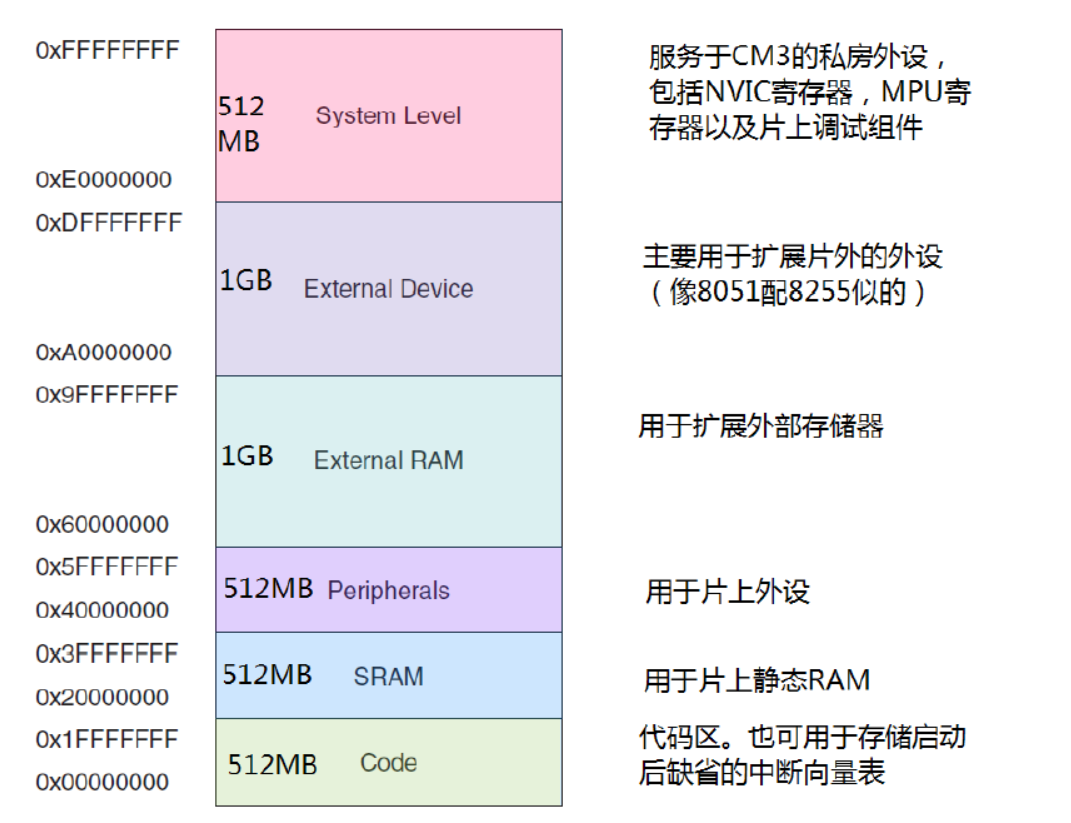

存储器映射

-

Cortex‐M3 支持4GB 存储空间。

-

通过把片上外设的寄存器映射到外设区,就可以简单地以访问内存的方式来访问这些外设的寄存器,从而控制外设的工作。

-

所有这些设备均使用固定的地址。

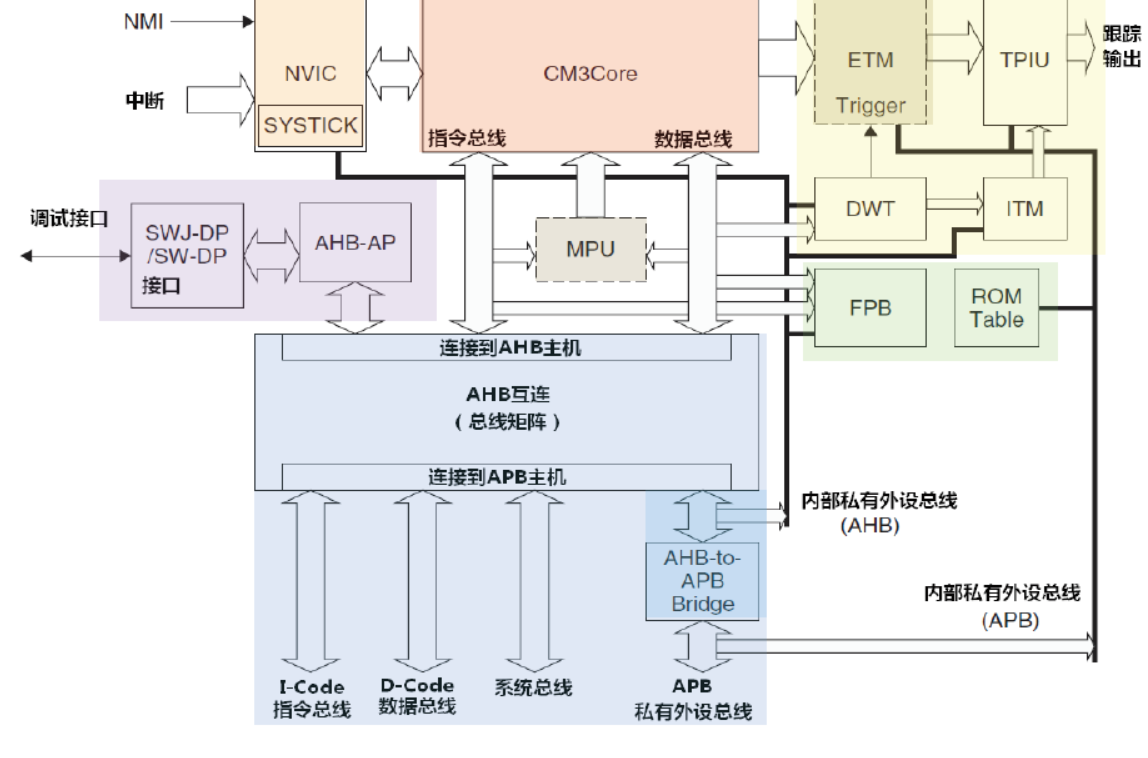

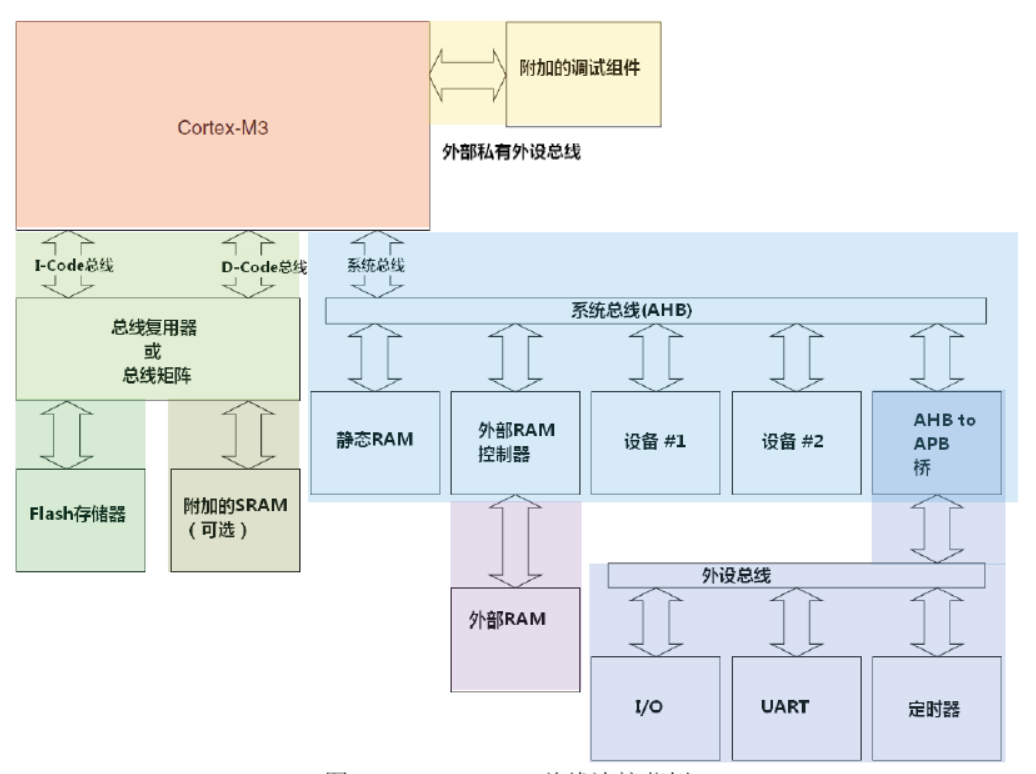

总线接口

Cortex‐M3 内部有若干个总线接口,以使CM3 能同时取址和访内(访问内存):

- 指令存储区总线(两条)

I‐Code 总线和D‐Code 总线,负责对代码存储区的访问。前者用于取指,后者用于查表等操作。 - 系统总线

系统总线用于访问内存和外设,覆盖的区域包括SRAM,片上外设,片外RAM,片外扩展设备,以及系统级存储区的部分空间。 - 私有外设总线

私有外设总线负责一部分私有外设的访问,主要就是访问调试组件。

存储器保护单元(MPU)

-

可以对

特权级访问和用户级访问分别施加不同的访问限制。 -

当检测到犯规(violated)时,MPU 就会产生一个fault 异常,可以由fault异常的服务例程来分析该错误,并且在可能时改正它。

-

最常见的就是由操作系统使用MPU,以使特权级代码的数据,包括操作系统本身的数据不被其它用户程序弄坏。

-

MPU 在保护内存时是按区管理的。

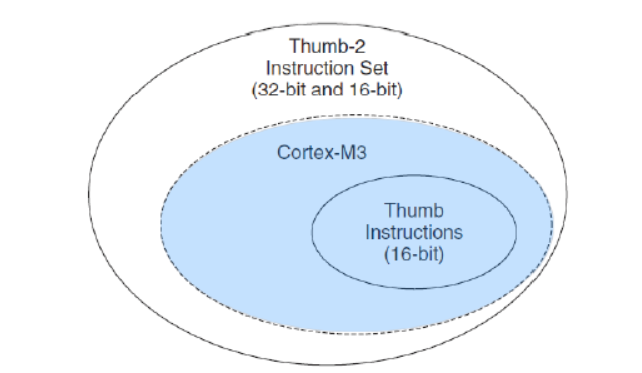

指令集

- Cortex‐M3 只使用Thumb‐2 指令集。

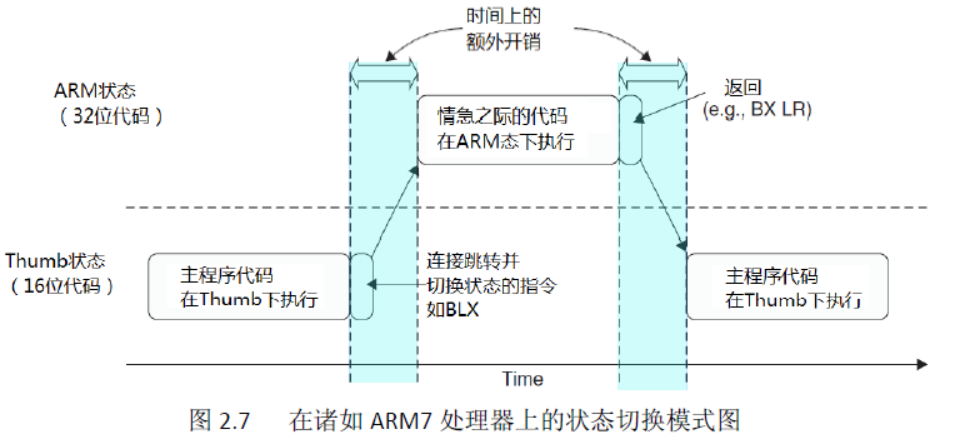

- 以前使用ARM指令和Thumb指令两种状态下的切换操作:

- 缺点即:增加时间上的额外开销。

中断和异常

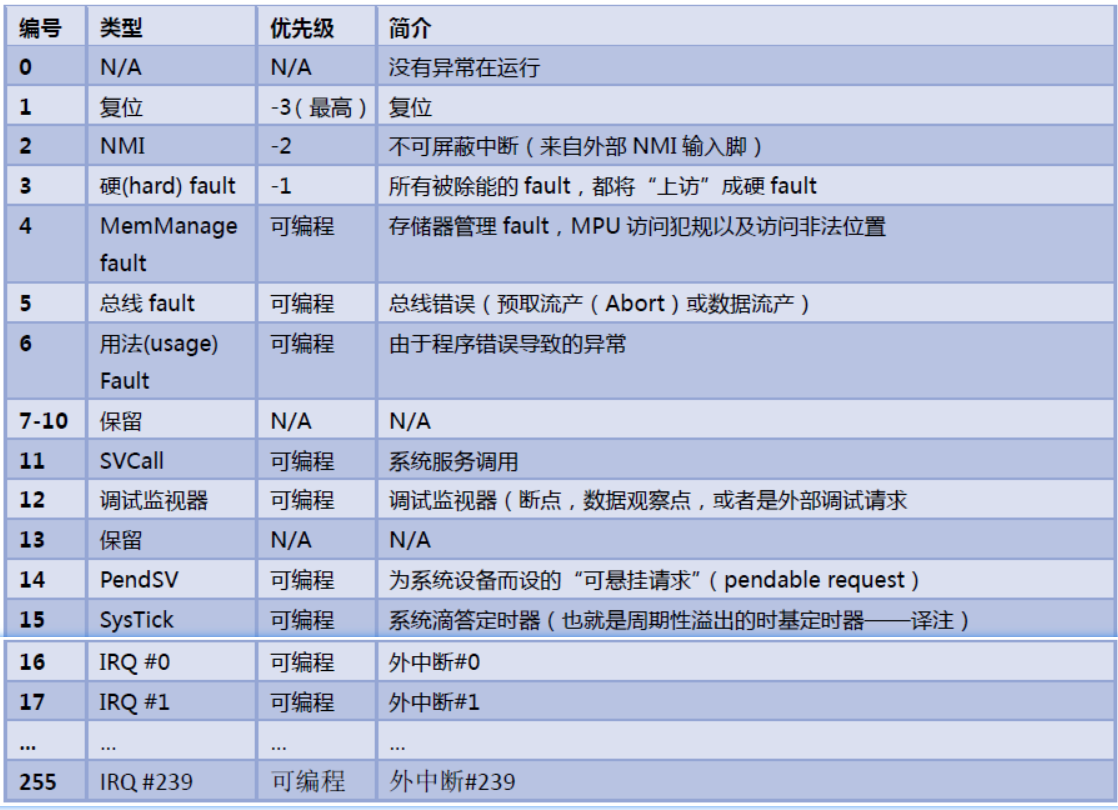

- 支持11 种系统异常(保留了4+1 个档位),外加240 个外部中断输入。

- CM3 的所有中断机制都由NVIC 实现。

- 具体使用了多少个是由芯片生产商决定。

- CM3 还有一个NMI(不可屏蔽中断)输入脚。当它被置为有效(assert)时,NMI 服务例程会无条件地执行。

调试支持

- 最主要的就是程序执行控制,包括

停机(halting)、单步执行(stepping)、指令断点、数据观察点、寄存器和存储器访问、性能速写(profiling)以及各种跟踪机制。 - 不同于以往的ARM 处理器,内核本身不再含有JTAG 接口。

- 取而代之的是CPU 提供称为

“调试访问接口(DAP)”的总线接口。 - 可以

访问芯片的寄存器,也可以访问系统存储器,甚至是在内核运行的时候访问。 - 对此总线接口(DAP)的使用,是由一个调试端口(DP)设备完成的。

- DPs 不属于CM3 内核,但它们是在芯片的内部实现的。

- 可用的DPs 包括

SWJ‐DP(既支持传统的JTAG 调试,也支持新的串行线调试协议),另一个SW‐DP(去掉了对JTAG 的支持),ARM CoreSignt 产品家族的JTAG‐DP 模块。

三、ARM基础

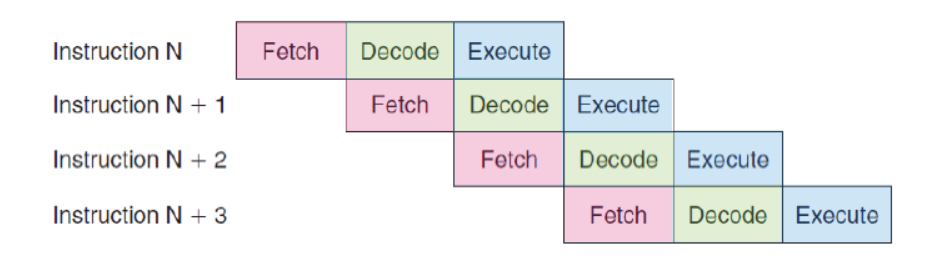

流水线

- Cortex‐M3 处理器使用一个3 级流水线。流水线的3 级分别是:取指,解码和执行。

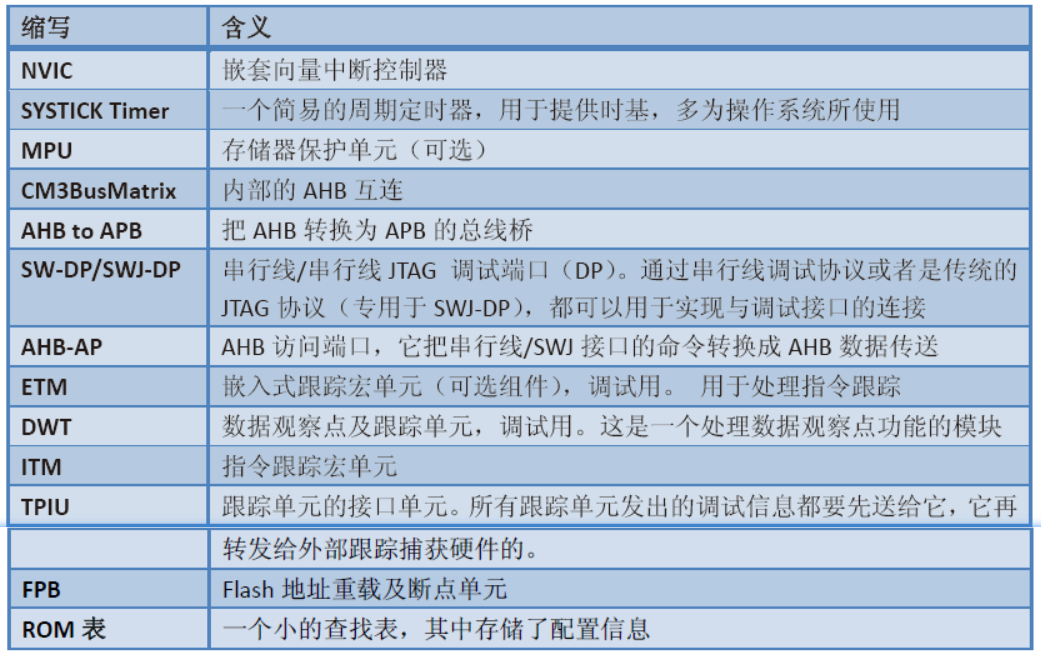

Cortex-M3 处理器系统方框图

Cortex-M3 的总线接口

I-Code 总线

- 基于AHB‐Lite 总线协议的32 位总线,负责在0x0000_0000 –0x1FFF_FFFF 之间的取指操作。

- 取指以字的长度执行,即使是对于16 位指令也如此。

- CPU 内核可以一次取出两条16 位Thumb 指令。

D-Code 总线

- 基于AHB‐Lite 总线协议的32 位总线,负责在0x0000_0000 –0x1FFF_FFFF 之间的数据访问操作。

- 处理器的总线接口会把非对齐的数据传送都转换成对齐的数据传送。因此,连接到D‐Code 总线上的任何设备都只需支持AHB‐Lite 的对齐访问,不需要支持非对齐访问。

系统总线

- 基于AHB‐Lite 总线协议的32 位总线,负责在0x2000_0000 –0xDFFF_FFFF 和0xE010_0000 – 0xFFFF_FFFF 之间的所有数据传送。

- 支持取指和数据访问,所有的数据传送都是对齐的。

外部私有外设总线

- 基于APB 总线协议的32 位总线。此总线来负责0xE004_0000 – 0xE00F_FFFF 之间的私有外设访问。

- 只留下了0xE004_2000‐E00F_F000 这个区间用于配接附加的(私有)外设。

调试访问端口总线

- 基于“增强型APB 规格”的32 位总线。

- 专用于挂接调试接口,例如SWJ‐DP 和SW‐DP。

各总线典型的连接方式

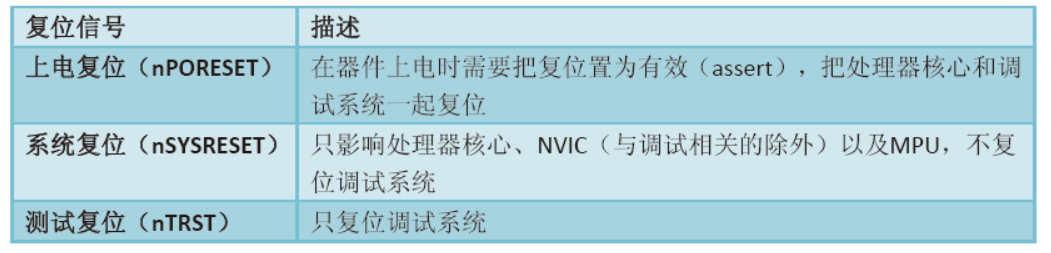

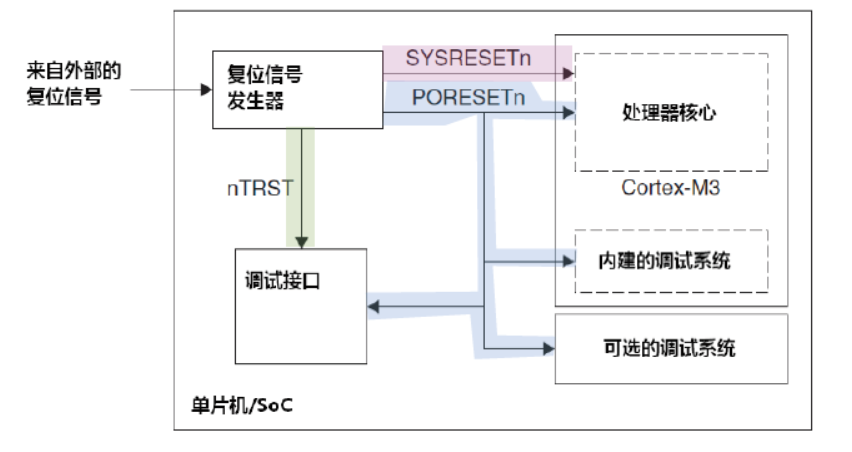

复位信号

本文来自博客园,作者:登云上人间,转载请注明原文链接:https://www.cnblogs.com/lj15941314/articles/arm_arche.html