IIC

问题

iic进行数据传输时,是高电平采样,还是上升沿采样?

https://www.eda365.com/forum.php?mod=viewthread&tid=138687&page=1#pid1090025

概述

IIC是Inter-Integrated Circuit的缩写,是一种两线接口,半双工总线。

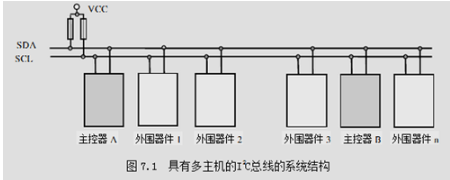

主从设备

从器件专用地址码:系统中所有的外围器件都具有一个7位的“从器件专用地址码”,其中高4位为生产厂家定义的器件类型;低3位为用户定义的器件引脚定义地址。

主控器件通过地址码建立多机通信的机制,从而不需要片选信号。所有器件都挂载在总线上,有主设备和从设备的区别,二者都可以进行数据传输。

支持多主控:任何能够进行发送和接收的设备都可以成为主总线。

主设备

要求:必须带有CPU的逻辑模块,同一总线上同一时刻只能有一个主端;

主要用于驱动SCL;

发起传输;

从设备

要求:总线上可以有多个从端,数量受地址空间和总线最大电容的限制;

不能发起传输,传输受主设备控制;

从设备对主设备产生响应;

时序

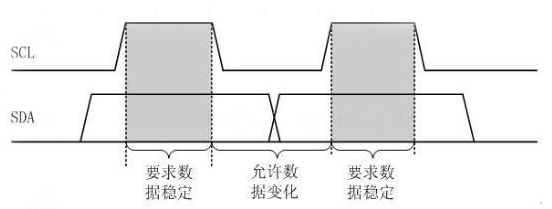

要求:传输过程中,SCL高有效时SDA不能发生变化。

IIC总线进行数据传输器件,在SCL为高电平时,SDA数据必须保持稳定,只有SCL为低电平时,SDA才允许变化。

信号线

IIC总线使用两条双向的信号线,一条是数据线Serial Data Line(SDA),另一条是时钟线Serial Clock Line(SCL)。

SCL:边沿触发,上升沿将数据输入到每个EEPROM中,下降沿驱动EEPROM器件输出数据。

SDA:双向数据线,为OD门,与其他任意数量的OD门与OC门成“线与”关系。

Open Collector(OC):集电极开路,对于三极管而言。

Open Drain(OD):漏极输出,对于MOS管而言。

空闲状态

IIC总线的SDA和SCL同时处于高电平时,总线处于空闲状态。此时各器件的输出级场效应管处于截止状态,即释放总线。由两条信号线各自的上拉电阻把电平拉高。

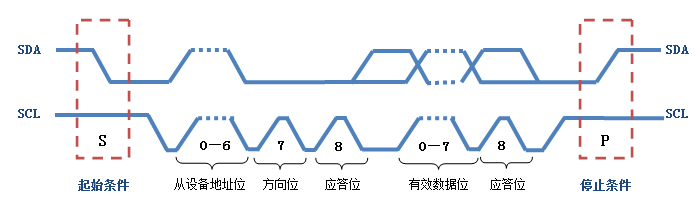

起始位与停止位

起始信号(必要):当SCL为高,SDA下降沿时进行数据传输。起始信号是一种电平跳变时序信号,不是电平信号。

停止信号(非必要):当SCL为高,SDA上升沿时停止数据传输。停止信号也是一种电平跳变时序信号,而不是一个电平信号。

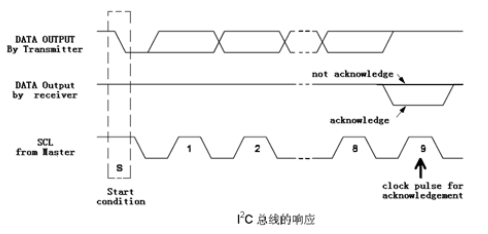

应答位

背景:发送端每发送一个字节,就在时钟脉冲的第9个时钟周期释放数据线(高电平);而接收端反馈一个应答信号。

信号:应答信号为低电平(有效应答位ACK)时,表示接收端已经成功接收了该字节;若应答信号为高电平(非应答位)时,表示接收器接收该字节没有成功。

接收端SDA要求:接收端在第9个时钟脉冲之前的低电平期间将SDA拉低,并确保在该时钟的高电平期间为稳定的低电平。

主设备为接收端时:在收到最后一个字节后,发送一个NACK信号,以通知被控发送端结束数据发送并释放SDA,以便主设备发送一个停止信号P。

若发送一个字节后未接收到应答信号:则返回错误,结束传输(标准IIC)。

数据有效性

IIC在进行数据传输时,SDA上的数据必须在时钟的高电平期间保持稳定;只有在SCL为低电平期间,数据线上的电平状态才允许发生变化。

IIC的数据在SCL的上升沿将数据打入器件中。因此,数据应当在SCL的上升沿前一段时间保持稳定。(推测)

数据的传输

从机的选择:IIC总线上的任意一个设备都可以作为主设备和从设备,主设备在向从设备进行数据传输时,需要选择从设备。在起始信号发送后,主机向从机发送从机的地址码(通常为7位),并在地址后添加读/写指令(0表示写,1表示读)。

在IIC总线上传送的数据为同步控制,每一位数据都有一个时钟脉冲相对应,即在SCL串行时钟有效沿处,SDA逐位地串行传输数据。

总线速率

普通模式:100KHz;

快速模式:400KHz;

高速模式:3.4MHz;

IIC仲裁

暂时不了解

IIC总结

- 数据传送时,SCL为高电平时,SDA必须保持稳定;SCL为低时,允许SDA改变;并且每个字节传送时都是高位在前;

- ACK=0时为有效应答位,表示接收端已经成功接收,若为1则说明接受不成功;

- 如果从机需要延迟下一个数据字节开始传送的时间,可以通过把SCL电平拉低并保持来强制主机进入等待状态;

- 主机完成一次通信后还想继续占用总线在进行一次通信,而又不释放总线,就要利用重启动信号。它既作为前一次数据传输的结束,又作为后一次传输的开始;

- 总线冲突时,按“低电平优先”的仲裁原则,把总线判给在数据线上先发送低电平的主器件;

- 在特殊情况下,若需禁止所有发生在I2C总线上的通信,可采用封锁或关闭总线,具体操作为在总线上的任一器件将SCL锁定在低电平即可;

- SDA仲裁和SCL时钟同步处理过程没有先后关系,而是同时进行的。