DC(三)——时钟约束

时钟约束相关概念

建立时间Tsetup:时钟有效沿到来之前,数据需要保持稳定的时间,否则触发器无法锁存数据。

保持时间Thold:在时钟有效沿到来之后,数据需要保持稳定的时间,否则触发器无法锁存数据。

亚稳态semi-stable state:在数据的建立时间和保持时间中对信号进行采样,导致输出无法预测的状态。

时钟树属性概念

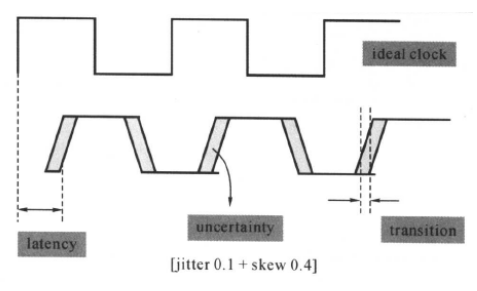

时钟树相关属性对于时钟的影响如下图所示。

时钟偏移(clock skew):由于时钟信号到不同寄存器之间存在的线网延时,导致时钟分支信号在到达不同的寄存器的时钟端口存在的相位差(考虑的对象是不同寄存器之间的延时,相对延时)。与时钟频率无关,与时钟线长度、时钟线驱动的时序单元负载电容、个数。

时钟抖动(clock jitter):由于实际时钟与理想时钟的差异,导致实际时钟存在不随时间积累的、时而超前时而滞后的抖动。与频率无关,来源于热噪声、串扰、电磁干扰等因素。

时钟转换时间(transition):与理想时钟的直接跳变不同,时钟在高电平和低电平转换是通过对电容的充放电实现翻转,因此在跳变过程中存在点容充放电的时间。

时钟的延时(latency):时钟从时钟源到寄存器的时钟端口(绝对延时)的时间称为时钟的延时。包含两种类型:

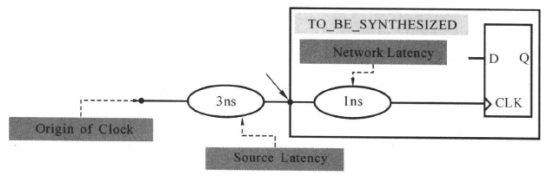

时钟源延时(source latency | insertion delay):是时钟信号从实际原点到模块的时钟端的延时,下图中的3ns;

时钟网络延时(clock network latency):时钟从模块的时钟端到寄存器时钟端口的延时,下图中的1ns。

时序路径及约束

时序路径

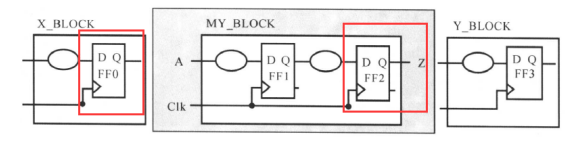

时序路径是点到点的数据通路,数据沿时序路径进行传输,每条时序路径有一个起点和终点。时序路径可以分为四条:输入端口到寄存器,寄存器到寄存器,寄存器到输出端口,输入端口到输出端口。详见《静态时序分析的基本概念和目的——3时序路径与关键路径》https://www.cnblogs.com/lizhiqing/p/12704545.html。

时序路径约束目的:约束时序路径是为了满足寄存器的建立时间和保持时间

路径2(寄存器到寄存器)约束

数据从FF1的D端口传输至FF2的D端口,主要经历的时间是触发器的翻转时间/转换延时Tcq、寄存器与寄存器之间的组合逻辑延迟Tco、连线延迟等。

FF2的建立时间

要求:数据经过上述延时(触发器的翻转时间/转换延时Tcq、寄存器与寄存器之间的组合逻辑延迟Tco、连线延迟)后到达FF2的D端口再加上FF2的建立时间需要小于一个时钟周期。

否则,若延时过大,在下一个cycle的有效沿到达时,FF1的数据仍在传输,则上一cycleFF1的输入数据无法在本cycle传递给FF2,数据可能无法满足建立时间导致无法更新。

对时钟进行建模后,上述延时(触发器的翻转时间/转换延时Tcq、寄存器与寄存器之间的组合逻辑延迟Tco、连线延迟)所允许的最大范围被确定。通过对时钟进行建模后,该路径的延时也被确定,DC将从单元库中选择单元来满足这些延时的约束,如果性能最好的单元仍无法满足建立时间要求,则DC会报错,需要重新修改设计(修改约束或修改代码)。

FF2的保持时间

要求:数据经过上述延时后到达FF2的D端不能小于某个值,否则会导致FF2采样到FF1在本cycle的信号,导致FF2原应保存的FF1上个cycle的信号产生亚稳态。

保持时间一般能够满足,即传输延时一般大于触发器的保持时间;即使无法满足,可以在后盾版图设计的时候采用在路径添加缓冲器来增加延时。因此一般只注意建立时间,而不关注保持时间。

定义时钟命令:

定义时钟(虚拟时钟除外),必须定义时钟周期(-period,下列表达式中10为一个周期的时长)和时钟源(get_port,下列表达式中clk为设计中的时钟端口);同时还允许定义可选项(option),如占空比(duty cycle,如果要同时使用时钟的两个沿,占空比将影响时序的约束),时钟偏移(offset/skew)和时钟名字(clock name)等,可通过 man create_clock查看相关命令。

一旦定义了时钟,就已经对寄存器之间的路径进行了约束,可以用report_clock命令来查看定义的时钟以及其属性。如果仅定义时钟周期对reg2reg进行约束会过于理想,需要再添加其他时钟属性,如时钟偏移skew,时钟抖动jitter,转换时间transition,延时latency等属性,上述时钟属性详见http://www.cnblogs.com/IClearner/p/6440488.html。

create_clock -period 10 [get_ports clk]

定义生成时钟命令2:

除了create_clock命令以外,还有create_generated_clock命令来创建产生的时钟,如分频后的时钟。创建生成的时钟时要指定时钟的名字和端口,分频数(倍频数),生成时钟的端口。

create_generated_clock -source clk2x -divied_by2 [get_pins clk]

定义虚拟时钟(virtual clock):

有时需要创建虚拟时钟用于说明相对于时钟的I/O端口的延迟,虚拟时钟在设计中不驱动触发任何寄存器。下列命令为建立一个周期为10ns,名字为vclk的虚拟时钟,虚拟时钟在定义时不需要定义时钟源。

create_clock -period 10 -name vclk

路径1(输入端口到寄存器)约束

考虑模块前后使用相同的时钟CLK,若使用不同时钟则不同。

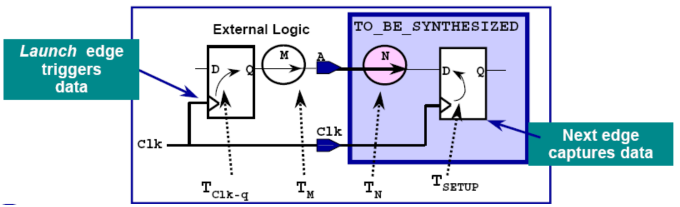

FF2的建立时间和输入的组合逻辑:

外部寄存器FF1在第一个cycle的有效沿发送数据给需要综合的电路,在FF2在下一个cycle接收。其中需要综合的FF2的建立时间Tsu和组合逻辑N的延时TN需要通过时序约束进行确定。因此需要在时序约束中明确FF1的翻转延迟Tclk-q和外部的组合逻辑延时TM。因此可以明确得到当前路径的满足建立时间需要使等式(Tclk-Tclk-q+TM≥TN+Tsu)成立。若不成立,DC则会进行优化,选择合适的单元进行综合使其满足约束;若无法满足约束,DC则会报错。因此需要明确待综合电路的外部延时是多少。

定义单个输入延时命令:

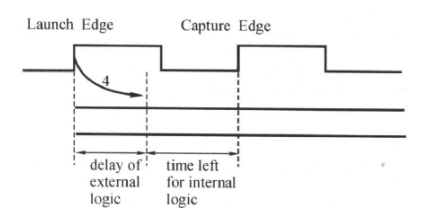

在输入中设置的输入延迟为Tclk-q+TM。如果已知输入端口的外部电路延时(包括FF1的翻转延时和外部组合逻辑M的延时),结合定义的时钟clk,则可以方便的计算出留给待综合电路从输入到寄存器D端口所允许的最大延时。定义输入延时的命令如下,指定了外部逻辑使用了4ns,若定义的时钟周期为10ns,则内部组合逻辑的最大延时允许为10-4-Tsu。

set_input_delay -max 4 -clock clk [get_ports A]

以上为理想状态下的输入约束。在非理想情况下,需要考虑不确定因素,如时钟抖动和偏移U、外部的输入延时D(包括前级寄存器翻转和组合逻辑的延时),则允许的最大延迟为clk_period-D-U-Tsu。

定义多个输入端口延时命令:

可以使用下列命令对除时钟外的所有输入端口设置约束。其中[remove_from_collection [all_inptus] [get_ports clk]]表示从所有输入端口中去除时钟clk。若需要移除多个时钟,可以使用 [remove_from_collection [all_inptus] [get_ports "clk1 clk2"]]。

set_input_delay 3.5 -clock clk -max [remove_from_collection [all_inputs] [get_ports clk]]

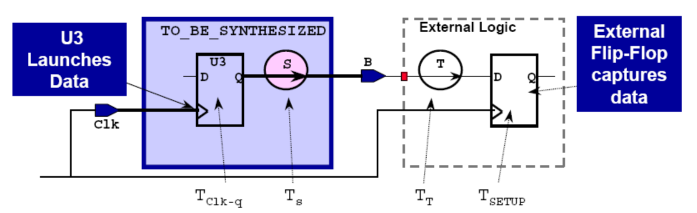

路径3(寄存器到输出端口)约束

路径3的理解方法与路径1的相类似,就是将路径1中的内部电路和外部电路调换位置。从时钟波形上看就是从下一个cycle的有效沿减去外部电路的延时,从该时刻到前一个cycle的有效沿即是内部电路所允许的最大延时。

FF2翻转时间和输出的组合逻辑S

路径3需要满足FF2的翻转延时Tclk-q和内部电路的组合逻辑延时TS,要在Tclk-TT(外部电路组合逻辑延时)-Tsu3(外部寄存器的建立时间)的范围内,DC会选择合适的单元组成内部电路和FF2使其满足时序要求。

定义输出端口延时命令:

在输出约束中设计的输出时间为TT+Tsu。通过输出端口延时命令定义外部逻辑所使用的时间,DC会根据定义的时钟计算内部电路所允许的时间范围。假设外部电路的所有延时为5ns,定义的时钟周期为10ns,那么FF2翻转时间和组合逻辑S的延时应小于10-5=5ns。

set_output_delay -max 5 -clock clk [get_ports B]

同样,上述是理想情况下的输出延时,实际中需要考虑时钟抖动和时钟偏移等不确定因素。

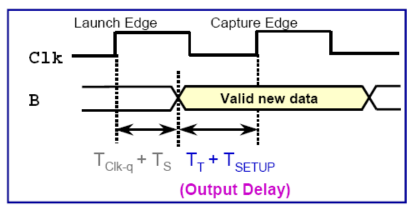

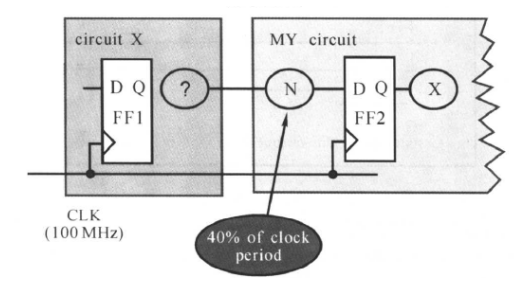

输入端口时序,输出端口时序与时间预算(Time Budget)

在SoC设计中,由于电路规模大,通常会由多个团队共同进行设计,每个设计团队负责部分模块的设计。然而设计者通常不知道每个模块的外部输入/输出延时的建立要求(设计规格书中可能有也可能没有)。

因此需要通过建立时间预算(Time Budget),预先确定外部输入/输出延时,从而方便输入/输出端口进行时序约束。通常有下述基本原则:DC要求对所有时间路径进行约束,而不应在综合时留有未加约束的路径。可以假设输入和输出的内部电路(组合逻辑?)各使用时钟周期的40%,那么存在20%的裕度用于前一级寄存器的翻转时间和后一级寄存器的建立时间。

以上述比例进行举例,对下图电路的时钟约束为:

create_clock -period 10 [get_ports clk]

set_input_delay -max 6 -clock clk [all_inputs]

remove_input_delay [get ports clk] #时钟不需要输入延迟约束

set_output-delay -max 6 -clock clk [all_outputs]

如果设计中模块的以前一级寄存器的输出端Q来划分内外部电路的话,时间预算将会变为如下内容:

create_clock -period 10 [get_ports clk]

set_input_delay -max $Tclk-q -clock clk [all_inputs]

remove_input_delay [get ports clk] #时钟不需要输入延迟约束

set_output-delay -max [expr 10-$Tclk-q] -clock clk [all_outputs]

路径4(输入到输出)约束

路径4是组合逻辑的路径,对于组合逻辑的约束可能需要虚拟时钟的概念,组合逻辑存在两种情况:

模块中有时钟

模块中存在输入端口到输出端口,也存在时序逻辑(模块中有时钟)。输入端口的寄存器和输出端口的寄存器由同一个时钟进行联系,那么模块内部组合逻辑F的延时TF需要在T-Tinput_delay-Toutput_delay的范围内才能满足时序约束。约束内容如下。对于多时钟同步约束,需要修改相应的延时和时钟,参考多时钟同步时序约束。同样,还存在不确定时钟因素。

set_input_delay 0.4 -clock clk -add_delay [get_ports B]

set_output_delay 0.2 -clock clk -add_delay [get_ports D]

set_max_delay $clk_period -from [get_ports B] to [get_ports D] #可无

纯组合逻辑(模块内部无时钟)

需要使用虚拟时钟。

DC中的时钟约束

默认情况下,在逻辑综合过程中一个时钟需要驱动很多寄存器,但是DC并不会在在连线上加时钟缓冲器(clock buffer)以加强驱动能力,而是将时钟直接连接在寄存器的时钟引脚上。换言之,对于高扇出(high fanout)的时钟连线,DC不会对其进行设计规则的检查和优化,通常由后端工具在时钟连线上加时钟缓冲器,或做时钟树的综合(clock tree synthesis),后端工具根据整个设计的物理布局(placement)数据,进行时钟树的综合。综合后的时钟树将满足skew,latency和transition的目标,如下左图为理想情况下的时钟树不确定因素全为0,右图为实际的时钟树。

为在综合过程中表现出时钟的不确定因素,可以在DC约束中设置时钟的不确定因素。逻辑综合中通常会给时钟加上dont_touch的约束,使得DC在综合时不会给时钟网络加入BUFFER以满足skew的要求(PPT与ICer说法矛盾)。时钟网络通常在布局布线阶段进行时钟树综合(CTS),命令为:

set_dont_touch_network [get_clocks clk]

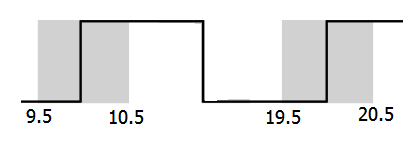

时钟偏移(skew)和抖动(jitter)的建模

命令为set_clock_uncertainty,可以对时钟的偏移和抖动进行建模。通常只约束建立时间,在考虑时钟偏移时,需要寄存器之间的组合逻辑的延时更大。

建立时间的偏移:set_clock_uncertainty -setup 0.5 [get_clocks clk]

保持时间的偏移:set_clock_uncertainty -hold 0.5 [get_clocks clk]

上升沿和下降沿的偏移:set_clock_uncertainty -rise 0.2 -fall -0.5 [get_clocks clk]

时钟转换(transition)时间建模

命令为set_clock_transition,默认的上升转换时间为电压的20%上升至80%的时间,下降的转换时间为电压的80%下降至20%的时间。若命令中不加开关选项‘-setup’和‘-hold’,那么将给时钟上升和下降赋予相同的转换时间。通常只约束最大的转换时间,使用-max命令。

set_clock_transition -max 0.2 [get_clocks clk]

时钟延迟(latency)的建模

命令为set_clock_latency。如上述概念所述,latency包含source latency和network latency,二者需要分开进行约束。在DC过程中通常仅对source latency进行建模,network latency在布局布线后可以计算得出。

通常情况下对最大的延时进行约束,在命令中加入‘-max’。

对时钟源延时进行约束:set_clock_latency -source 3 [get_clocks clk]

布局布线前对network latency的约束:set_clock_latency 3 [get_clocks clk]

在布局布线后可以计算实际的network latency,使用该命令代替上述命令:set_propagated_clock 2 [get_clocks clk]

浙公网安备 33010602011771号

浙公网安备 33010602011771号