DC(二)——DC综合流程

系统层次划分:

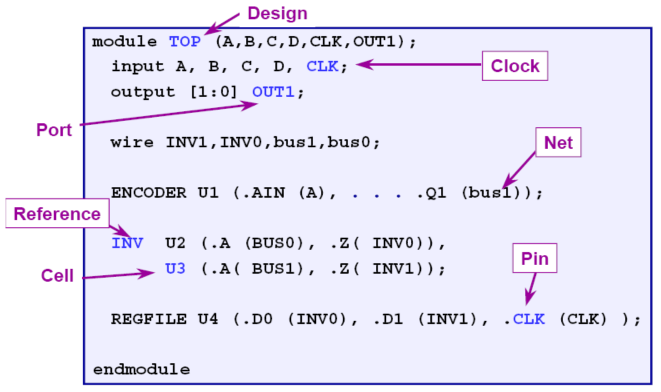

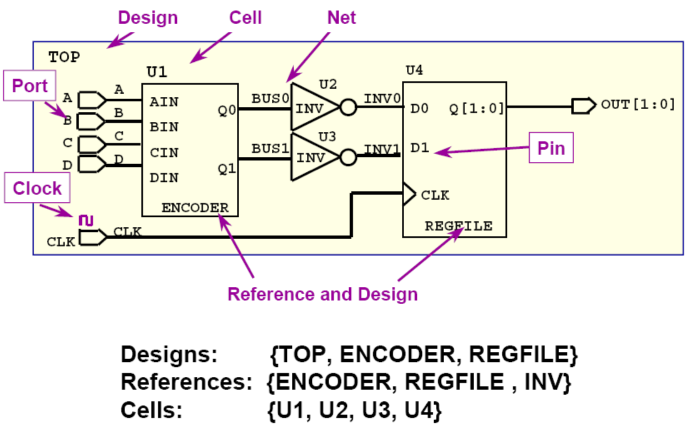

DC中每个设计由6个设计物体组成,分别为:design,cell,port,pin,net和clock。

当前设计为TOP,Port和Pin是与当前设计相关的一对概念,如果当前设计改变,相应的port和pin也会不同。

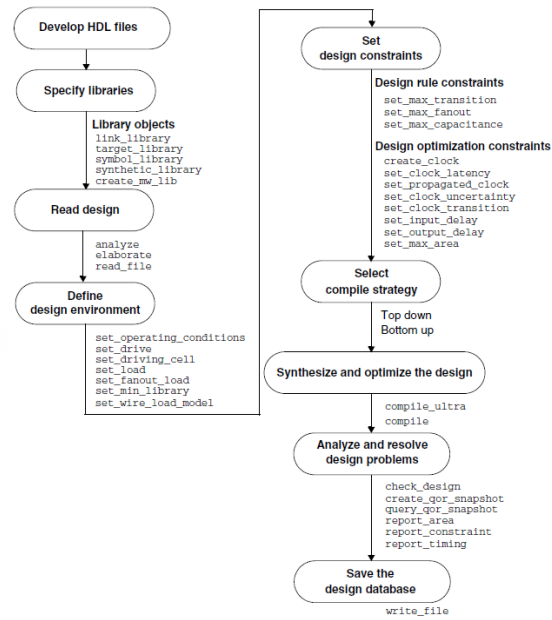

综合的流程

定义库

定义库

DC启动时会启动.synopsys_dc.setup文件,里面设定了综合所需要的工艺库的信息以及一些对于工具的设定命令。

在综合前需要设定好所需要的各种库,如综合库、I/O单元库、IP核等。

综合库中包含许多信息,如单元的功能、面积、时间、功耗、测试等,线负载模型,工作条件和设计规则约束。

单元的延迟与输入的逻辑转换时间和输出负载有关,可以根据每个单元输入逻辑转换时间和输出负载,在工艺库提供的LUT中查找单元的延时。

库:

目标库(target_library):DC在编译过程中来构成电路图的,将电路映射到具体的单元中。如:set target_library my_tech.db

链接库(link_library):是将设计连接到对应的库上,一般包括目标库、宏单元、IP核等。如:set link_library "*my_tech.db"。其中*指明当链接设计时,DC先搜寻内存中已有的库,然后在搜寻变量link_library中指定的其它库。

符号库(symbol_library):定义了单选显示的图形库,当用design_vision来查看图形的时候使用。

综合库(synthetic_library):又Synopsys公司提供的Design Ware库,包含许多IP核及运算单元,用于实现verilog描述的运算符,为电路的优化起着重要 作用。

搜寻路径(search_path):指定各种库的路径,可以将所用的库的路径放入search_path中,在设定target_library和link_library时不必加上库的绝对路径,DC会自动在search_path中寻找所用到的库的路径从而读入该库。

读入设计