存储器及存储器阵列

存储器阵列(memory array)

存储:数字系统需要存储器(memory)来存储电路使用过的数据和生成的数据,使用触发器组成的寄存器是一种存储少量数据的存储器;此外还有可以有效存储大量数据的存储器阵列。

存储器概述

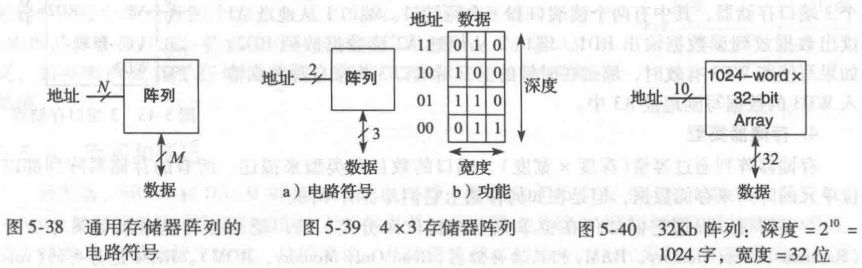

组成:图5-38是存储器阵列的通用电路符号。存储器由一个二维存储器单元阵列构成。存储器可以读取或者写入内容到阵列的一行,每行数据称 为一个字(word)。对于一个N位地址和M位数据的存储器阵列,包含了2N个M位字。

阵列的行与列:为阵列的深度(depth),行由地址(address)指定;列数为宽度(width),读出或写入的值为数据(data)。阵列的大小是depth×width。

样例:图5-40为一个1024字×32位的存储器阵列,地址数为10,字为32位,阵列大小为32Kb。

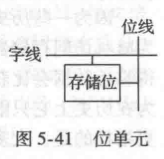

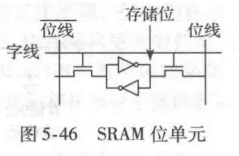

位单元(bit cell)

作用:存储器阵列由位单元的阵列组成。每个为单元存储一位数据,并通过一条字线(wordline)和一条位线(bitline)与外部相连。

读位单元:位线初始化为浮空(Z),字线打开为高,允许存储的值驱动位线为0或1;

写位单元:位线被强制驱动为期望的值,并将对应的字线打开为高,将位线连接至存储位,将期望值写入存储位。

存储器结构

读存储器:一条字线设为高电平,位单元的相应行驱动位线为高电平或低电平。

写存储器:将位线驱动值高电平或者低电平,然后将字线允许为高电平,允许位线的值存储到位单元的相应行中。

存储器端口

所有存储器都有一个或多个端口(port),每一个端口提供对一个存储器地址的读/写访问。多端口存储器可以同时访问多个地址。

存储器类型

存储器阵列通过容量(深度×宽度)、端口的数目和类型来表示。所有的存储器阵列都已以位单元的阵列来存储数据。但是如何存储上存在区别。

历史上,ROM是只能读的,但是现在既可以读也可以写,

ROM和RAM都是随机访问的,访问任何数据字的延迟都相等;与顺序访问存储器(磁带)相对。

当前二者唯一的区别是:RAM是易失型,关掉电源时会丢失数据;ROM是非易失型,没有电源也能无期限的保存数据。

区别:现代ROM不再只读,也可以写入。不同点在于ROM的写入时间更长,但是是非易失的。

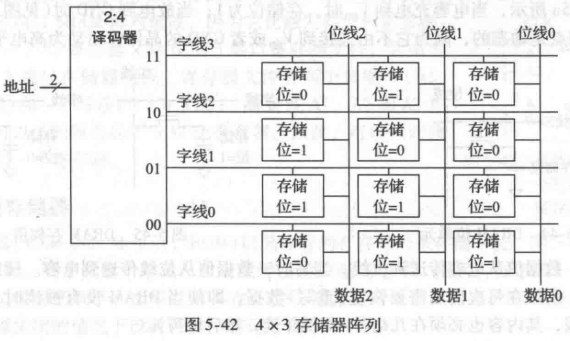

动态随机访问存储器(DRAM):

存储方式:以电容充放电来存储位。位值存储在电容中,nMOS作为开关。字线作为MOS的开关

更新操作:读操作时会破坏存储在电容中的位值,所以在每次读后需要重写数据;即使DRAM没有被读,电容的电压也会泄露,所以其内容需要在几毫秒内刷新。

静态随机访问存储器(SRAM)

存储方式:数据存储在交叉耦合反相器中,当字线有效时,两个MOS管都打开,数据值从位线上传入/传出。

更新存储:由于存在交叉耦合的反相器,如果噪声减弱存储位的值,则交叉耦合反相器将恢复存储值。

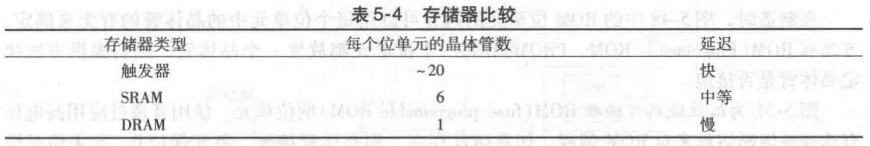

存储器面积、延迟对比

触发器、SRAM和DRAM都是易失的存储器,但是存在不同的面积和延迟特性。

DRAM延迟比SRAM更长,因为其位线不是由晶体管驱动,而是电容,而电容将值移动到位线的速度较慢。

DRAM的吞吐量通常也比SRAM低,因为其必须周期性的在读取后刷新。

当前已有多种不同新的DRAM技术:

同步DRAM(SDRAM),使用一个时钟使存储器访问流水性化;

双倍速率SDRAM(DDR),同时使用时钟的上升沿和下降沿来存取数据,以获得双倍的吞吐率。

存储器的延迟和吞吐量也与存储器的大小有关,在其他条件相同时,大容量存储器一般比小容量存储器更慢。

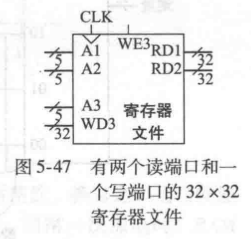

寄存器文件(register file)

作用:数字系统常用一组寄存器来存储临时变量,这组寄存器称为寄存器文件。

组成:通常由小型多端口SRAM阵列组成,比触发器阵列更加紧凑。

下图为一个32×32位的三端口寄存器文件,有两个读端口和一个写端口组成,能同时读两个寄存器,写一个寄存器。

`timescale 1ns / 1ps module ram_dual_port #(parameter N=6, M=32)( inout [M-1:0] data_io, input [N-1:0] addr, input wr, rd, input clk, rst ); reg [M-1:0] ram[2**N-1:0]; reg data; integer i; always@(posedge clk) begin if(!rst) begin for(i=0; i<2**N-1; i=i+1) ram[i] <= 32'b0; end else if(wr) begin ram[addr] <= data_io; end else if(rd) begin data <= ram[addr]; end else data <= 32'bz; end assign data_io = rd ? data : 32'bz; endmodule

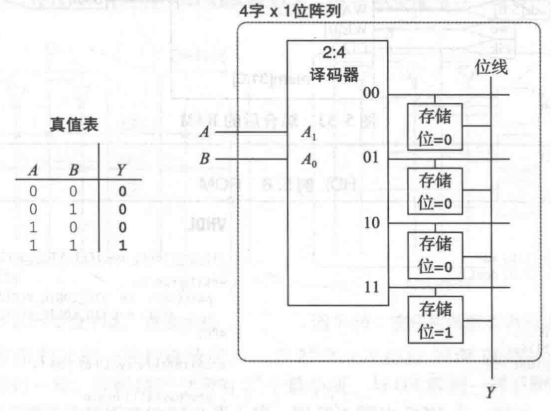

只读存储器(ROM)

注意:ROM的位单元时组合电路,在电源关闭的情况下没有可以“忘记”的状态。

存储方式:以是否存在晶体管作为是否存储一位。在读过程中,位线被拉高,如果存在MOS,则位线被拉低,不存在MOS则保持高。

点表示法:在字线和位线交叉点表示为1。

使用存储器阵列的逻辑

查找表(LookUp Table):用于执行逻辑的存储阵列,存储器阵列可以根据位存储的值,实现组合逻辑功能。

浙公网安备 33010602011771号

浙公网安备 33010602011771号