AXI总线协议

AXI特定名词

AXI Transaction:the complete set of required operations on the AXI bus form the AXI Transaction.表示传输一段数据(AXI burst)所需的一整套操作;

AXI Burst:any required payload data is transferred as an AXI Burst.表示AXI待传数据;

AXI Beats:a burst can comprise multiple data transfers, or AXI Beats.表示AXI burst的组成,一个Beat就是一个transfer。

关系:一个Burst指对一个地址上的数据进行拆分后多次传输,传输Burst的过程称为transaction,每次传输内容称为一个‘Beat’,传输Beat的过程称为transfer。

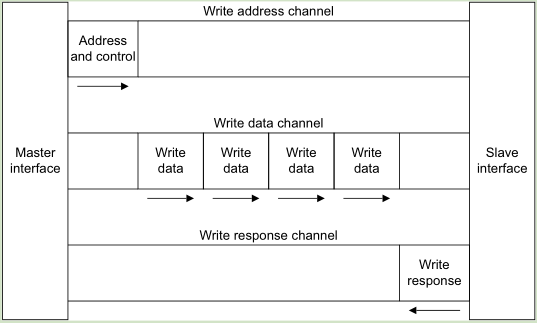

AXI组成

AXI4协议中包含五种信道,通道之间相互独立且存在差别,通过通道进行通信之前需要使用VALID/READY 进行握手,Read和Write根据Master定义:

- 读地址信道(Read Address Channel)

- 写地址信道(Write Address Channel)

- 读数据信道(Read Data Channel)

- 写数据信道(Write Data Channel)

- 写响应信道(Write Response Channel)

还有两种Component

- Master component

- Slave component

通信由Master发起,Master可以对Slave进行读数据(read)或写(write)数据。每次读写操作都需要一个地址,读地址信道(Read Address Channel)和写地址信道(Write Address Channel)用于传输地址。在写完数据后,Master需要确认Slave有没有收完数据,Slave收到完整数据后,会通过写响应信道(Write Response Channel)给Master一个反馈(completion),表示写操作已经完成。

VALID/READY 握手机制

在五个信道通信之前,需要使用VALID/READY进行握手,信道通信仅发生在VALID和READY同时有效的阶段[1]:

由数据发送端发送VALID,表示已经将数据、地址或控制信息置于写总线上;

由数据接收端发送READY,表示已经准备好接收发送端的信息;

当VALID和READY同时置高时,在时钟上升沿到达后,表示开始数据传输;完成数据传输后,两个信号置低。

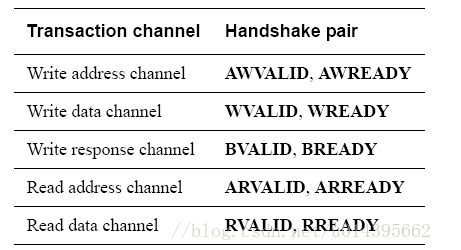

信道中的VALID/READY

五个信道的VALID/READY信号表示如下:

A表示Address,W表示Write,B表示Back(Response),R表示Read;

在握手过程中,还会用到LAST信号。LAST信号存在Write Data Channel和Read Data Channel中,分别表示为WLAST和RLAST,用于标记burst的最后一次数据传输,当slave接收到LAST信号后,说明本次数据传输完成。

双向流控机制

VALID/READY 机制使用双向流控机制,指发送端通过 VALID 置起控制发送速度的同时,接收端也可以通过将置高READY 与否控制接收速度,反压发送方的发送速度。

握手规则

信道的握手规则

VALID信号置高后,在完成本次传输之前不能拉低,直到有相应的READY被声明;

READY信号置高后可以在VALID信号置高之前取消;

VALID信号置高与READY信号无关,VALID信号不能由READY信号控制;

在一个burst的最后一次transfer时,必须由LAST信号置高。

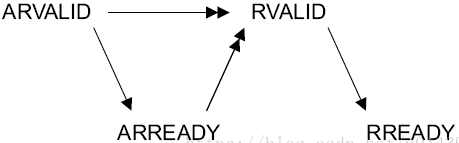

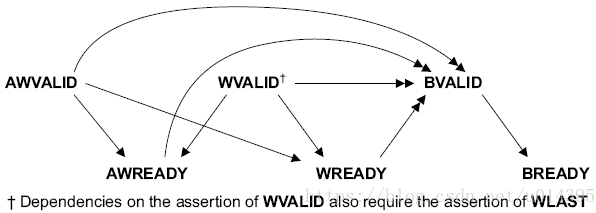

握手信号在不同操作下的依赖关系:

PS:单箭头表示双方无先后要求,双箭头表示箭头所指对象应迟于箭头出发信号发送。

读操作握手信号依赖关系:

读数据通道的握手信号要在读地址通道后传输

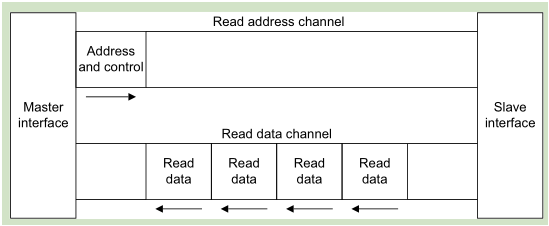

读操作数据传输图:

写操作握手信号依赖关系:

写操作时,写数据通道和写地址通道没有先后关系;

写反馈通道信号必须在写数据通道和写地址通道握手后进行;

WVALID信号与WLAST信号相关;

写操作数据传输图:

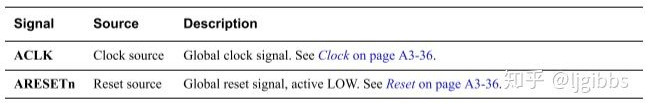

信号

全局信号:

ACLK,全局时钟信号,所有传输操作都发生在上升沿;

ARESETn,全局复位信号,低电平有效,可以异步复位,但是必须和ACLK同步释放。复位过程中VALID信号都要拉低,其他所有信号可以驱动为任意值。

复位过程中,Master必须把ARVILID、AWRVLID和WVALID拉低;Slave必须把RVIALID和BVALID拉低。

写地址通道信号:

| Signal | Source | Description |

| AWID | Master | 写地址ID,写地址 |

| AWADDR | Master | 写地址,在一次burst transaction中第一个transfer的地址。 |

| AWLEN | Master | burst的长度,一次burst中的transfer的数量。 |

| AWSIZE | Master | burst中一次transfer的字节数。 |

| AWBURST | Master | burst类型和size信息,决定本次burst中trasnfer地址的计算方式 |

| AWLOCK | Master | lock类型, |

| AWCACHE | Master | 内存类型 |

| AWPORT | Master | 保护类型, |

| AWQOS | Master | QoS |

| AWREGION | Master | 区域标志,能实现单一物理接口对应多个逻辑接口 |

| AWUSER | Master | user信号,在写地址信号中可选的用户定义信号,仅在AXI4使用 |

| AWVALID | Master | 写地址的valid信号,表示写地址和控制信号可以发送。 |

| AWREADY | Slave | 写地址的ready信号,表示slave可以接受一个地址或相关的控制信号。 |

读地址通道信号

| Signal | Source | Description |

| ARID | Master | 读地址ID |

| ARADDR | Master | 读地址,首地址? |

| ARLEN | Master | burst的长度,一次burst中的transfer的数量。 |

| ARSISE | Master | burst中一次transfer的字节数。 |

| ARBURST | Master | burst类型和size信息,决定本次burst中trasnfer地址的计算方式 |

| ARLOCK | Master | lock类型 |

| ARCACHE | Master | 内存类型,表明一次传输如何通过系统 |

| ARPROT | Master | 保护烈性,一次传输的安全及被 |

| ARQOS | Master | QoS |

| ARREGION | Master | 区域标志 |

| ARVALID | Master | 读地址VALID信号 |

| ARREADY | Slave | 读地址READY信号 |

写数据通道信号

| Signal | Source | Description |

| WID | Master | 写数据ID,仅AXI3支持 |

| WDATA | Master | 写数据 |

| WSTRB | Master | 标记写数据中有效的字节,一位对应一个字节 |

| WLAST | Master | 写LAST信号,在本次burst的最后一次transfer中置高。 |

| WUSER | Master | user信号,在写数据信号中可选的用户定义信号,仅在AXI4使用 |

| WVALID | Master | 写数据的valid信号,表示写地址和控制信号可以发送。 |

| WREADY | Slave | 写数据的ready信号,表示slave可以接受一个地址或相关的控制信号 |

特点:存在一个读数据通道没有的STROBE信号,用于标识写数据中有效的传输字节,或者用于读写宽度不对称

读数据通道

| Signal | Source | Description |

| RID | Slave | 读数据ID |

| WDATA | Slave | 读数据 |

| RRESP | Slave | 读回复信号,表示读transfer的状态 |

| RLAST | Slave | 读LAST信号,在本次burst的最后一次transfer中置高。 |

| RUSER | Slave | user信号,在读数据信号中可选的用户定义信号,仅在AXI4使用 |

| RVALID | Slave | 写数据的valid信号,表示写地址和控制信号可以发送。 |

| RREADY | Master | 写数据的ready信号,表示slave可以接受一个地址或相关的控制信号 |

特点:读Response信号在读数据通道中由slave发送,且无strobe信号。

写回复通道信号

| Signal | Source | Description |

| BID | Slave | 写ID |

| BRESP | Slave | 写回复信号,表示写transaction的状态 |

| BUSER | Slave | user信号,仅AXI4支持 |

| BVALID | Slave | 回复VALID,表示写回复信号可以发送 |

| BREADY | Master | 回复READY,表示master可以接受回复 |

低功耗接口信号

| Signal | Source | Description |

| CSYSREQ | 时钟控制器 | 系统退出低功耗请求,此信号由时钟控制器向外设发送 |

| CSYSACK | 外设 | 退出低功耗状态确认 |

| CACTIVE | 外设 | 外设请求时钟有效 |

Burst传输

In the AHB protocol every transfer comes with an address value on HADDR. As you already know how the address will change because of what is signalled on HBURST, HTRANS and HSIZE, the HADDR information for all transfers after the start of the burst could be considered unnecessary as the target slave could calculate the addresses for transfers after the start of the burst.

In AXI the aim was to reduce unnecessary bus traffic, so here the master just issues the address for the start of a burst, and that is all that is required on the address channel. The target slave then calculates the address changes for each subsequent transfer in the burst based on what it sampled on AxADDR, AxSIZE, AxBURST and AxLEN.

So for example, if the AXI master signals an INCR burst of 4 transfers, with AxSIZE signalling 32-bit transfers, and AxADDR is 0x4, the slave can then see that the transfers for this burst will be to 0x4, 0x8, 0xC and 0x10.[2]

理解:由于每次传输的数据地址变化存在一定规律,因此AXI传输与规律相关的参数,而非直接传输每次的数据地址

AXI协议是基于burst的,Master只给出transaction的第一个字节的地址,Slave必须计算后续transfer的地址。

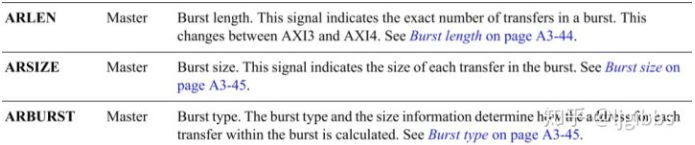

通道信号描述

在地址通道中有三个信号控制进行控制,包括:

BURST类型有三种,分别为:

| AxBURST[1:0] | Burst Type | Description |

| 0b00 | FIXED | 每个transger都使用相同地址,后续数据不断写入起始地址,刷新其实地址上的数据 |

| 0b01 | INCR | 后续地址在前一个地址的基础上递增 |

| 0b10 | WRAP | 从起始地址递增至到达最高地址,再返回起始地址,重复上述操作,用于cache的访问 |

| 0b11 | Reserved |

BURST len:指在一次Burst传输中transfer的次数,从0开始,实际长度为AxLEN+1.

要求:

- INCR类型最大支持长度为256,其他类型最大长度为16,所有BURST类型最少为1;

- 对于长度超过16的INCR BURST,可以转换为较小的BURST,即使transaction attributes指明该transaction时Non-modifiable;

- 对于WRAP模式,BURST len仅能为2、4、8、16;

- 一次传输中,地址不能跨越一个4KB分区,防止跨越两个Slave的边界;

- 一次transaction不能再未达到BURST len的时候提前结束。

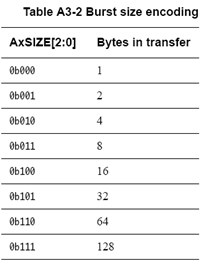

BURST size:指在一次transfer中的最大数据宽度,burst size不能超过数据线本身宽度;当数据线本身宽度大于BURST size时,将根据协议相关规定制定数据在部分数据线中传输。

AxSIZE由三个字节表示,数据大小为2^AxSIZE[2:0]。

BURST address:

- Start_Address:由Master决定,每个burst的第一个transfer的地址

- Number_Bytes = burst size

- Data_Bus_Bytes:总线宽度/8

- Aligned_Address:Start_Address @ Number_Bytes

RRESP[1:0]和BRESP[1:0]

OKAY:Normal access success + Exclusive access failed

EXOKAY: Exclusive access okay

SLVERR: Slave error

- FIFO满或空;

- transfer size不支持;

- 向只读设备写入;

- Slave timeout;

- access to a disabled or powered-down function

DECERR:Decode error

- interconnnect不能成功向Slave access译码;

- access一个缺省Slave,由缺省Slave回应DECERR

在write transaction中,对于整个burst,slave只会回应一个BRESP;

在read transavtion中,Slave可以对不同的transfer回应不同的RRESP;

AxCACHE

参考文献: