时钟分频器

作用

分频器主要用于提供不同相位和频率的时钟

前提

分频后的时钟频率都小于原始时钟的频率,若没有更高频的主时钟无法得到同步分频时钟;

时钟分配原则

时钟的分频应当在规划的初期就进行考虑,也就是在系统层面上进行考虑,而不是到后端设计的时候。时钟分配策略的考虑因素包含以下几点:

- 系统的时钟分配计划,主要包含时钟树方案,各个模块的时钟频率等;

- 时钟的最小延时,主要是根据系统运行速度定义最小延时要求,与时钟的分配计划有重叠?

- 时钟缓冲,考虑负载问题,往往也是在设计时钟树时应当考虑的问题;

- 消除时钟偏移,时钟偏移总是存在的,如何减小时钟偏移以达到预期效果需要考虑;

- 门控时钟,软硬件协同设计等盛典模式的考虑,需要具体情况具体分析,还可从低功耗设计角度进行观察。

一、偶数分频器:

分频原理:

以获得ƒ/2n的时钟信号为例:一个周期内,占空比50%的原始时钟信号ƒ在高电平与低电平的时间相同、相位相差180°(相反),因此相邻的两个上升沿(或者下降沿)的频率必然是原始时钟的1/2倍。之后通过Counter数n个ƒ/2信号就可以获得ƒ/2n的时钟信号了。

module divider #(parameter NUM_DIV = 8)(

output div_clk,

input clk, rst

);

reg [3:0] cnt;

always @(posedge clk)

begin

if(!rst)

cnt <=0;

else if(cnt==(NUM_DIV/2)-1)

cnt <= 0;

else

cnt <= cnt+1;

end

assign div_clk = (cnt<=NUM_DIV/2-1)?1:0;

endmodule

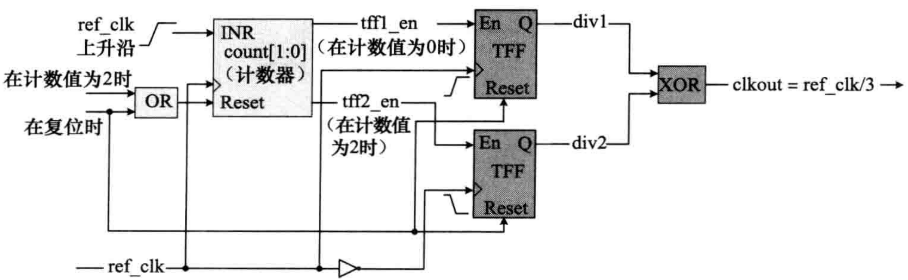

占空比为50%奇数分频器

分频原理:

这种分频器有多种方法实现,其基本原理也是基于多个偶数分频器的组合逻辑实现。

原理1:使用两个周期为2N、相位差为90°的时钟信号来获得周期为N的奇数分频器(N为odd);

原理2:使用一个(N-1)/2和(N+1)/2

原理1:

非整数分频(非50%占分比)

非50%占分比,1.5倍频

1.5倍频为每三个参考时钟包含两个对称的脉冲

应为在多路选择端切换开关时两个输入端的延时不相等,多路器的输出不能马上改变,并可能在输出始终上产生毛刺,并且随着参考时钟(ref_clk)频率的增加,出现错误的可能性会越来越大。在仿真时可以正确工作,但是在综合可能出现问题。

非50%占分比,4.5倍频

根据分频的

浙公网安备 33010602011771号

浙公网安备 33010602011771号