亚稳态

内容

亚稳态

定义:介于两个有效状态之间的中间状态,且无法确定停留在亚稳态的时间。

原因:在违背建立时间、保持时间时,亚稳态可能会出现(并非所有不满足tsu和th的输入变化都会导致亚稳态)。

亚稳态的危害

由于产生亚稳态后,寄存器Q端输出在稳定下来之前可能是毛刺、振荡、固定的某一电压值。在信号传输中产生亚稳态就会导致与其相连其他数字部件将其作出不同的判断,有的判断到“1”有的判断到“0”,有的也进入了亚稳态,数字部件就会逻辑混乱。在复位电路中产生亚稳态可能会导致复位失败。怎么降低亚稳态发生的概率成了FPGA设计需要重视的一个注意事项。

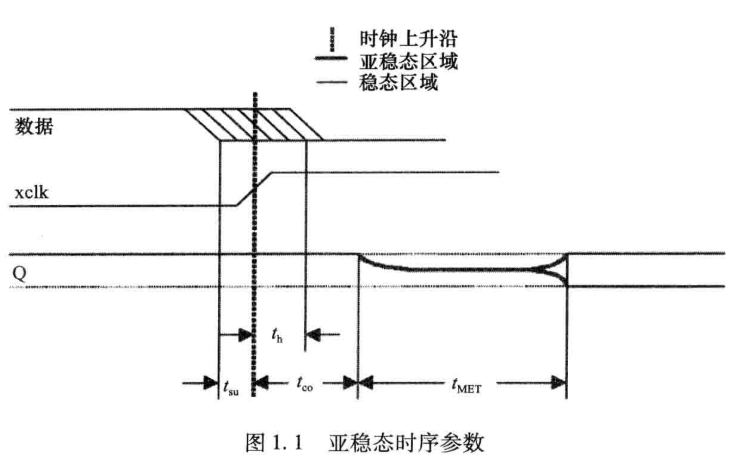

亚稳态时序参数:

建立时间tsu:输入数据在时钟到来之前需要保持稳定的时间;

保持时间th:输入数据在时钟到来之后需要保持稳定的时间;

(输出响应时间)时钟到输出的延迟时间tco:从时钟变化开始到输出数据发生变化的时间;

稳定时间tMET:亚稳态输出恢复到稳定状态所需要时间中超出tco的时间;

触发器是否进入亚稳态和返回稳态的时间都取决于期间工艺和外界环境;通常来讲一般会在一到两个时钟周期内返回稳态。

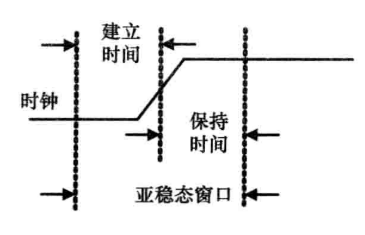

亚稳态窗口(Metastability Window):

由建立时间tsu与保持时间th决定,具有特定时间长度;在这段时间内输入信号和时钟如果发生变化可能会导致输出成为亚稳态;窗口越大,进入亚稳态的概率越大。

Metastability window=tsu+th

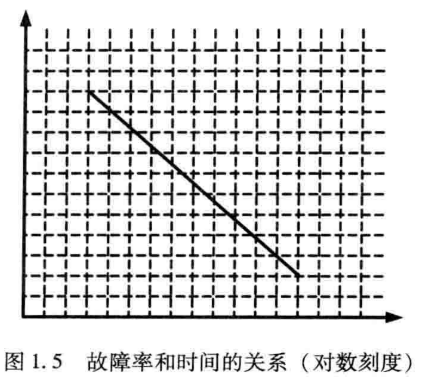

平均无故障时间MTBF:

tr:允许超出器件正常传输延迟时间的解析时间;

τ:触发器的亚稳态时间常数;

W:亚稳态窗口;

fc:时钟频率;

fd:异步信号边沿频率;

根据上图任取两点可以计算解析时间常数;

tr1:解析时间1

tr2:解析时间2

N1:tr1时刻的故障次数

N2:tr2时刻的故障次数

信号违背时序要求的条件:

- 输入信号是异步信号;

- 时钟偏移/摆动(上升/下降时间)高于容限值;

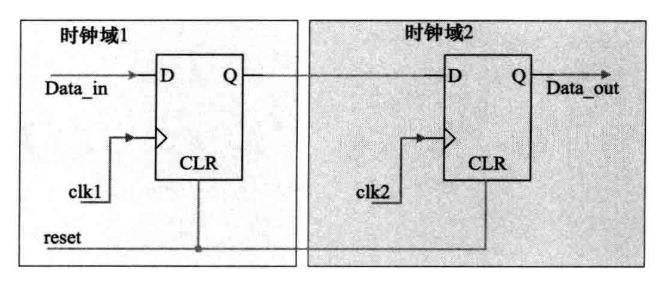

- 信号在两个不同頻率或者相同频率但是相位和偏移不同的时钟域下跨时钟域工作;

- 组合延迟使触发器的数据输入在亚稳态窗口内发生变化;

信号避免亚稳态的方法:

- 确保时钟周期足够长,clk>准稳态的解析时间&通往下一级触发器的路径上的任何逻辑延迟;

- 使用同步器;

同步器模式:

1、模式A:输入频率小于时钟频率

2、模式B:输入频率大于时钟频率

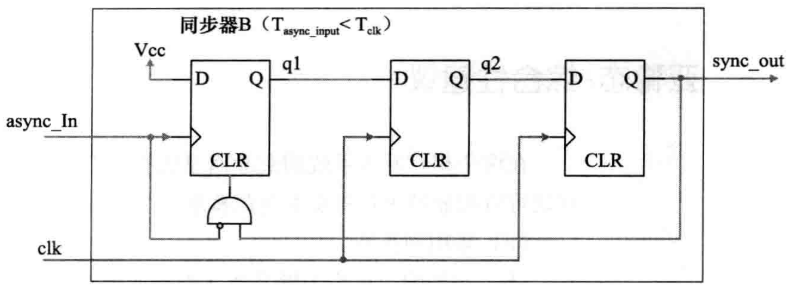

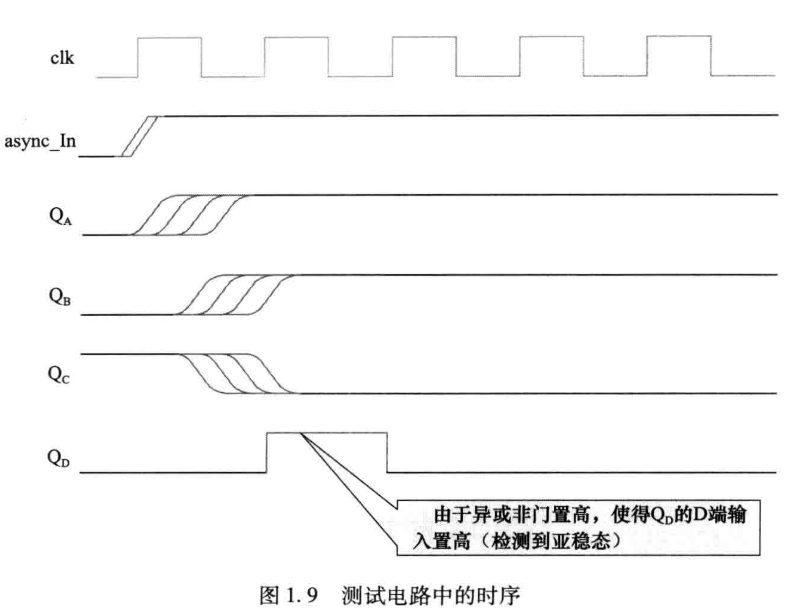

亚稳态检测电路:

异步输入async_In,时钟clk;FFA、FFD正边沿触发,FFB、FFC下降沿触发;

正常情况下,QB和QC的输出互为反向,通过同或门(XNOR)输出为0,QD输出为0;

当亚稳态时,XNOR输出为1,FFD捕捉到亚稳态事件;

可以通过改变时钟高电平时间Δt控制所要求的稳定时间:

tMET=Δt-tACN

tACN为最小时钟周期,等于FFA的输出响应时间+FFB|FFC(解析触发器)的建立时间;

what's mean? 减少解析时间或者稳定时间的方法之一为给建立时间/保持时间出的数据集中加入抖动

亚稳态综合性建议:

- 采用同步器;

- 采用响应更快的触发器(缩短亚稳态窗口Tw);

- 使用亚稳态硬化触发器(转为高带宽设计并且减少为时钟域输入电路而优化的采样时间);

- 使用级联触发器作为同步器(一个触发器的亚稳态失败概率为P,则多个触发器的失败概率为指数倍);

- 减少采样速率;

- 避免使用dV/dt低的输入信号;

浙公网安备 33010602011771号

浙公网安备 33010602011771号