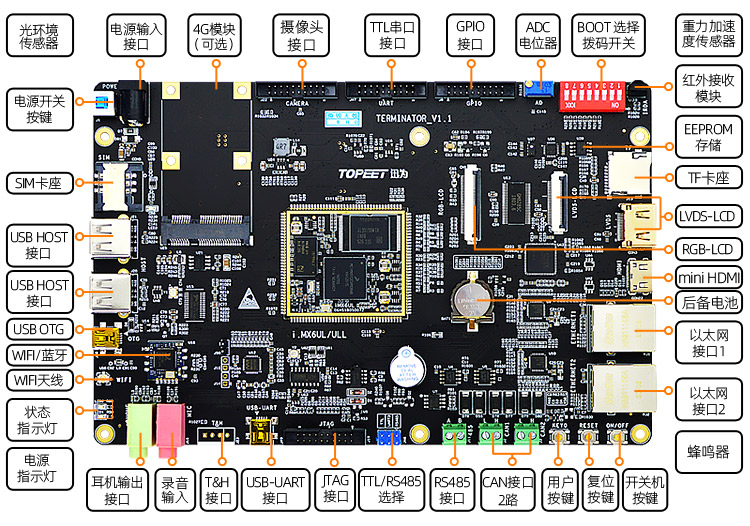

资料丨迅为IMX6ULL开发板-主频和时钟配置例程

在前面几节讲的都是 GPIO 的功能,本章我们会讲解如何修改和配置 CPU 的主频,了解 iMX6ULL 的时钟系统。

15.1 i.MX6ULL 时钟系统

iMX6ULL 的系统主频为 528MHz,有些型号可以跑到 696MHz,但是默认情况下 iMX6ULL 的主频为396MHz。我们想要让 iMX6ULL 运行时候达到最大性能,就需要将主频上调至最大 528MHz,或者更大,其它的外设时钟也要设置到 NXP 官方推荐的值。

更多关于芯片的时钟可以查阅 《IMX6ULL 参考手册.pdf》的第 10 章“Chapter 10 Clock and PowerManagement”和第 18 章“Chapter 18 Clock Controller Module (CCM)”,这两章有详细的讲解。

系统时钟

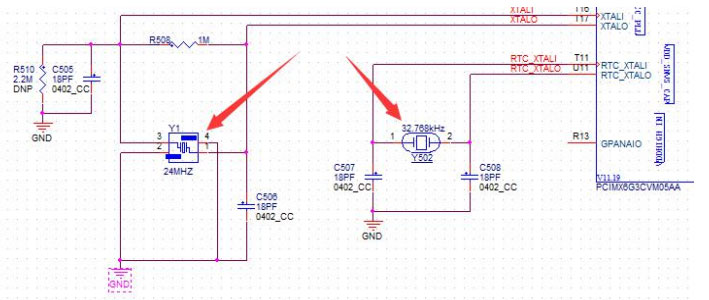

我们打开核心板原理图,搜索“RTC_XTALI”即可看到如图 15.1.1 内容:

这里我们可以看到有两个晶振。32.768KHz 的晶振是 RTC(实时时钟)的时钟源。24MHz 晶振是 CPU 内核及其他外设的时钟源。

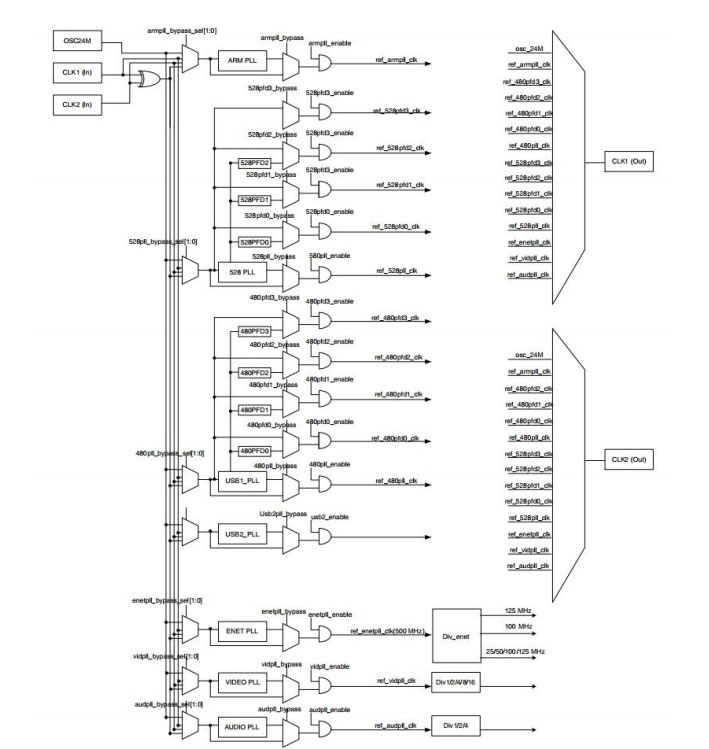

PPL(Phase Locked Loop)时钟源

iMX6ULL 系列外设所需要的时钟源,都是由 24MHz 晶振倍频产生的,一共有 7 组,如图 15.1.2 所示:

PPL1(ARM_PLL):这个 PPL 供内核使用,可编程倍频器,最高可达 1.3GHz。注意,此频率高于芯片支持的最大频率 1.0 GHz。

PPL2(System_PLL 或 528_PLL):固定 22 倍频,产生 528MHz。这个 PPL 还分出 4 路 PFD,即PLL2_PFD0~PLL2_PFD3,528_PLL 和 PLL2_PFD0~PLL2_PFD3 为各种总线提供时钟。他们不提供精确的或恒定的频率,可以实现动态调频。通常的,528_PLL 和 PLL2_PFD0~PLL2_PFD3 作为系统内部总线,内部逻辑处理单元,DDR 接口,NAND/NOR 接口模块等的时钟源。

PPL3(USB1_PLL):用于 USBPHY(OTG PHY),固定 20 倍频,同样分出 4 路 PFD,即 PLL3_PFD0~PLL3_PFD3,产生了 480MHz 的 VCO 频率和 24MHz 振荡器。主 PPL 和 4 路 PFD 也可作为其他接口时钟输入。

PPL4(Audio PLL):用于音频外设,提供低抖动和高精度音频时钟,频率范围为 650MHz~1300MHz,频率分辨率优于 1Hz。可以选择 1/2/48/16 分频。

PPL5(Video PLL):用于标准视频显示外设,提供低抖动和高精度音频时钟,频率范围为 650MHz~1300MHz,频率分辨率优于 1Hz。该时钟主要用作显示和视频接口的时钟。可以选择 1/2/48/16 分频。

PPL6(ENET_PLL):固定为 20+5/6 倍频,产生 500MHz,在此基础上产生 25/50/100/125MHz 网络时钟。

PPL7(USB2_PLL):用于 USB2PHY(OTG PHY),固定 20 倍频,产生了 480MHz 的 VCO 频率和 24MHz振荡器。

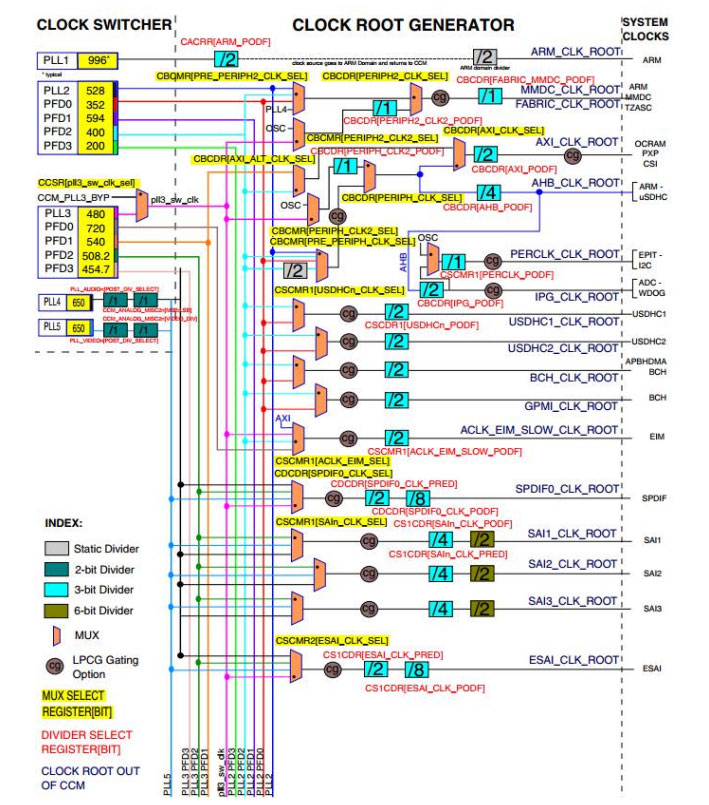

时钟树

如此多的时钟分支都要一一对应不同的外设。我们要参考《IMX6ULL 参考手册.pdf》里的 18.3 小结“CCMClock Tree”,来学习如何选择 PPL 时钟。

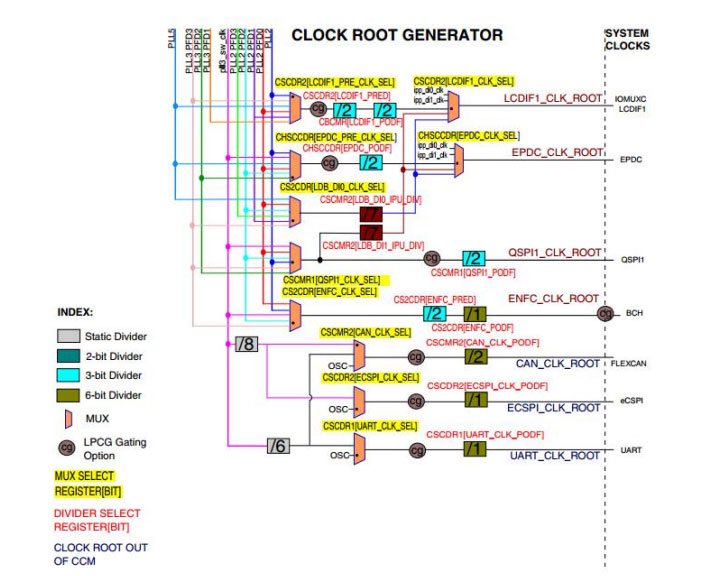

时钟树整体分为三个部分:CLOCK SWITCHER、CLOCK ROOT GENERATOR 和 SYSTEM CLOCKS。其中左边的CLOCK_SWITCHER 就是我们上一小节讲解的那 7 路 PLL 和 8 路 PFD,右边的 SYSTEM CLOCKS 就是芯片外设,中间的 CLOCK ROOT GENERATOR 部分的作用就是选择合适的时钟接入外设接口,负责给 CLOCK SWITCHER 和SYSTEM CLOCKS 连线。就是在 7 路 PLL 和 8 路 PFD 选择合适时钟源,提供给外设使用。

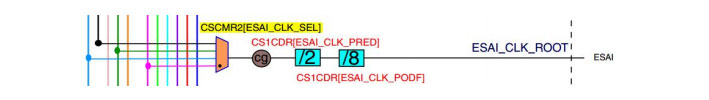

我们以 ESAI 外设为例,ESAI 时钟图 15.1.5 所示:

这里的 CLOCK ROOT GENERATOR 又被分成三部分:

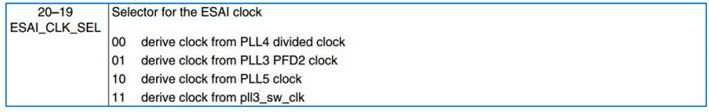

ESAI_CLK_SEL:时钟源选择器,手册中搜索“ESAI_CLK_SELESAI ”可知,有 4 个可选的时钟源:PLL4、PLL5、PLL3_PFD2 和 pll3_sw_clk。具体选择哪一路作为 ESAI 的时钟源是由寄存器 CCM->CSCMR2 的ESAI_CLK_SEL 位来决定的,用户可以自由配置。如图 15.1.6 所示:

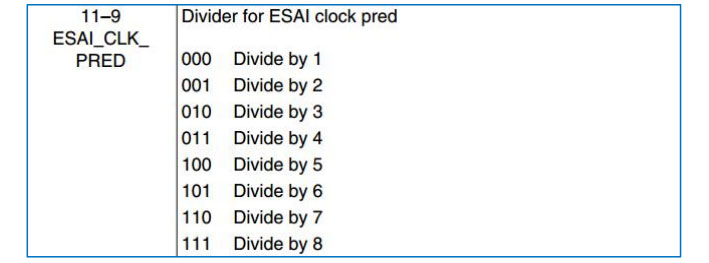

1. ESAI_CLK_PRED:一次分频,手册中搜索“ESAI_CLK_PRED”可知,有 1~8 分频 8 种选择,分频值由寄存器 CCM_CS1CDR 的 ESAI_CLK_PRED 来确定的,假如现在 PLL4=650MHz,我们选择 PLL4 作为 ESAI 时钟,一次分频选择 2 分频,那么此时的时钟就是 650/2=325MHz。如图 15.1.7 所示:

2. ESAI_CLK_PODF:二次分频,手册中搜索“ESAI_CLK_PODF”可知,在一次分频的基础上在此分频,有 1~8 分频 8 种选择,经过此分频器以后的时钟就是 325/8=40.625MHz。因此最终进入到 ESAI 外设的时钟就是 40.625MHz。

以上是以外设 ESAI 为例的设置方式,其他外设可以根据具体需求查看手册去配置。

内核时钟

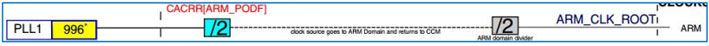

上一节的时钟树上我们可以查找到 ARM 内核时钟如图 15.1.8 所示:

1. 时钟源 PPL1,默认为 996MHz。

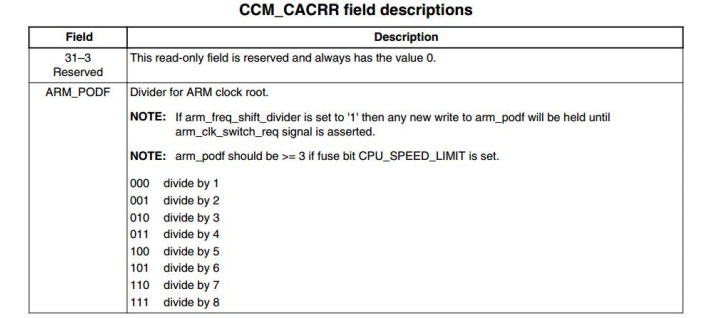

2. 寄存器 CCM_CACRR 的低三位即 ARM_PODF 位对 PLL1 进行分频,有 0~7 分别对应 1~8 分频 8 种选择。这里选择 2 分频,经过分频之后就是 996/2=498MHz,如图 15.1.9 所示:

这样,出来的就是 ARM 的内核时钟,也就是芯片主频(498MHz)。

如果我们要设置 528MHz,我们需要设置 PPL1 为 1056MHz,寄存器 CCM_CACRR 的 ARM_PODF 位配置为 2 分频即可。如果我们要设置为 696MHz 主频。我们需要将 PPL1 设置为 696MHz,那么寄存器 CCM_CACRR的 ARM_PODF 位配置为 2 分频即可。

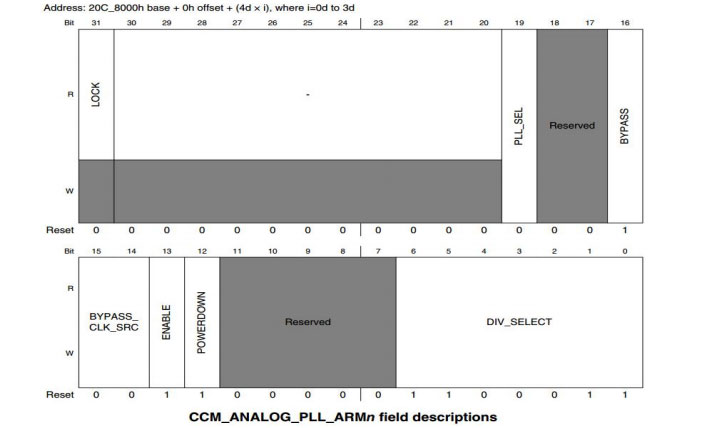

我们在来看下如何设置 PPL1。PPL1 是由寄存器 CCM_ANALOG_PLL_ARMn 决定的,结构如图 15.1.10:

寄存器 CCM_ANALOG_PLL_ARMn 中有两个主要位:

ENABLE: 时钟输出使能。1:使能 PLL1 输出,0:关闭 PLL1 输出。

DIV_SELECT: 设置 PLL1 的输出频率,可设置范围为:54~108,PLL1 CLK = Fin *div_seclec/2.0,Fin=24MHz。如果 PLL1 要输出 1056MHz 的话,div_select 就要设置为 88。在修改 PLL1 时钟频率的时候我们需要先将内核时钟源改为其他的时钟源,PLL1 可选择的时钟源如图 15.1.11 所示:

1. pll1_sw_clk 也就是 PLL1 的最终输出频率。

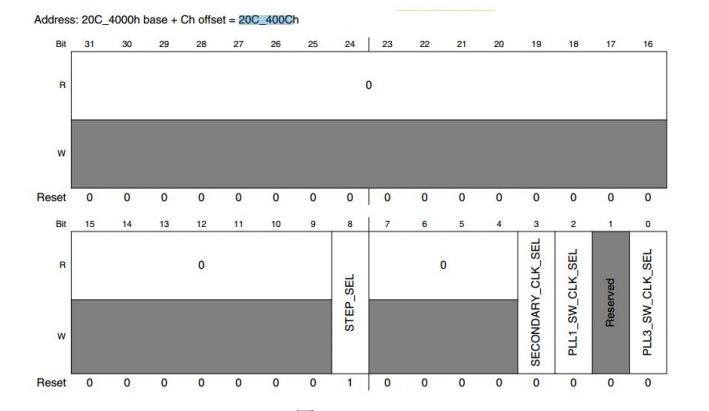

2. 选择器,选择 pll1_sw_clk 的时钟源,寄存器 CCM_CCSR 的 PLL1_SW_CLK_SEL 位决定 pll1_sw_clk 是选择 pll1_main_clk 还是 step_clk。正常情况下应该选择 pll1_main_clk,但是如果要对 pll1_main_clk(PPL1)的频率进行调整的话,比如我们要设置 PLL1=1056MHz,此时就要先将 pll1_sw_clk 切换到 step_clk 上。等pll1_main_clk 调整完成以后再切换回来。

3. 选择器,选择 step_clk 的时钟源,由寄存器 CCM_CCSR 的 STEP_SEL 位来决定 step_clk 是选择 osc_clk还是 secondary_clk。一般选择 osc_clk,也就是 24MHz 的晶振。

这里我们就用到了一个寄存器 CCM_CCSR,结构如图 15.1.12 所示: <ignore_js_op>

<ignore_js_op>